半导体器件物理II必背公式+考点摘要.docx

《半导体器件物理II必背公式+考点摘要.docx》由会员分享,可在线阅读,更多相关《半导体器件物理II必背公式+考点摘要.docx(18页珍藏版)》请在冰豆网上搜索。

半导体器件物理II必背公式+考点摘要

半二复习笔记

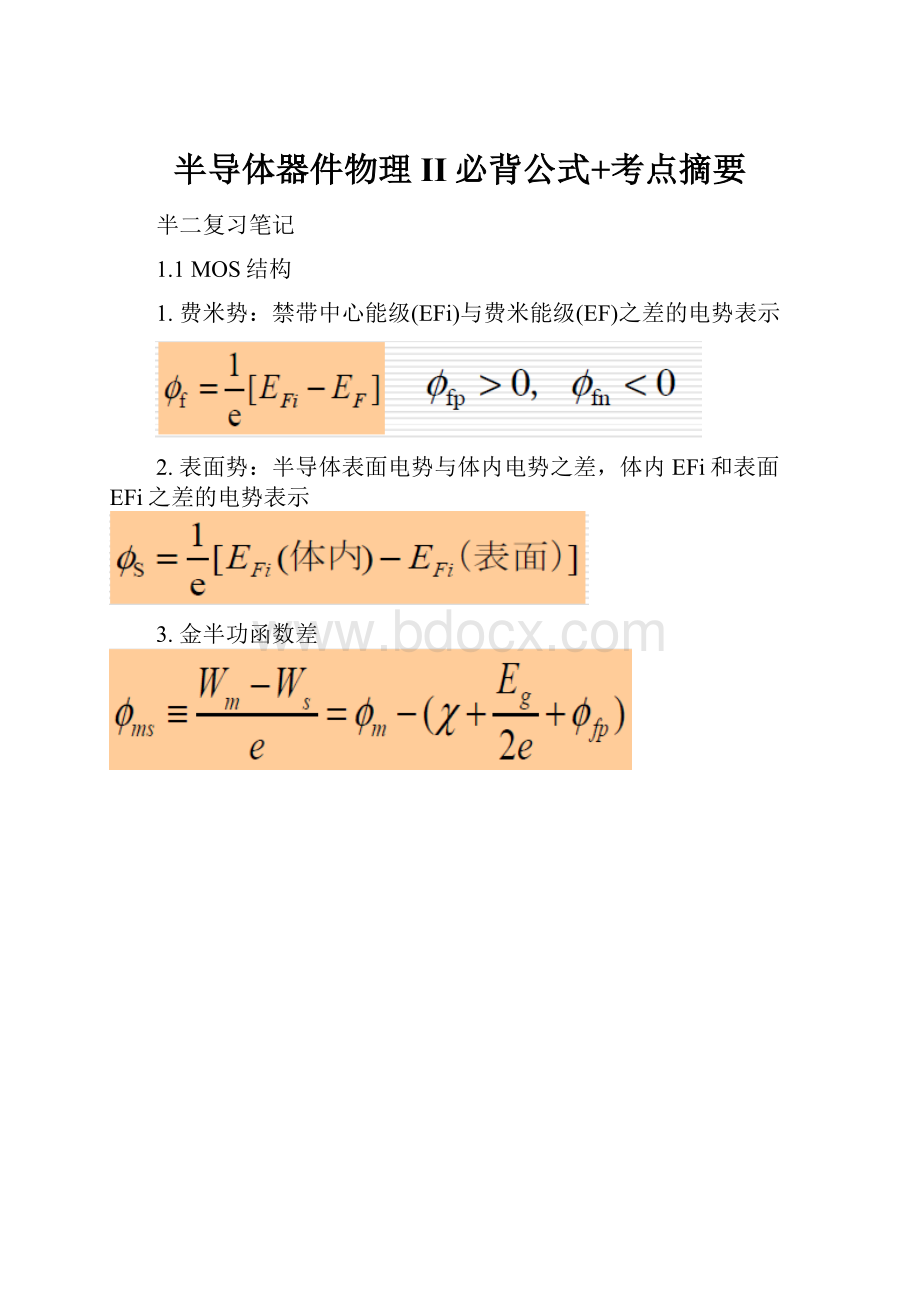

1.1MOS结构

1.费米势:

禁带中心能级(EFi)与费米能级(EF)之差的电势表示

2.表面势:

半导体表面电势与体内电势之差,体内EFi和表面EFi之差的电势表示

3.金半功函数差

4.P沟道阈值电压

注意faifn是个负值

1.3MOS原理

1.MOSFET非饱和区IV公式

2.跨导定义:

VDS一定时,漏电流ID随VGS变化率,反映了VGS对ID的控制能力

3.提高饱和区跨导途径

4.衬底偏置电压VSB>0,其影响

5.背栅定义:

衬底能起到栅极的作用。

VSB变化,使耗尽层宽度变化,耗尽层电荷变化;若VGS不变,则反型沟道电荷变化,漏电流变化

1.4频率特性

1.MOSFET频率限制因素:

①沟道载流子的沟道运输时间(通常不是主要的限制因素)②栅电容充放电需要时间

2.截止频率:

器件电流增益为1时的频率

高频等效模型如下:

栅极总电容CG看题目所给条件。

若为理想,CgdT为0,CgsT约等于Cox,即CG=Cox;

非理想情况即栅源、栅漏之间有交叠,产生寄生电容:

①CgdT的L为交叠部分长度②CgsT的L为L+交叠部分长度(CgsT=Cgs+Cgsp)。

3.提高截止频率途径

1.5CMOS

1.开关特性

2.闩锁效应过程

2.1非理想效应

1.MOSFET亚阈特性

①亚阈值电流:

弱反型态:

势垒较低→电子有一定几率越过势垒→形成亚阈值电流

②关系式:

③注:

若VDS>4(kT/e),最后括号部分≈1,IDsub近似与VDS无关

④亚阈值摆幅S:

漏电流减小一个数量级所需的栅压变化量,S是量化MOS管能否随栅压快速关断的参数。

⑤快速关断:

电流降低到Ioff所需VGS变化量小。

因此S越小越好

⑥亚阈特性的影响:

开关特性变差:

VGS=0时不能理想关断;静态功耗增加

⑦措施:

提高关断/待机状态下器件的阈值电压VT(如通过衬底和源之间加反偏压,使VT增加)、减小亚阈值摆幅

2.沟长调制效应(VDS↑⇒ID↑)

①机理

理想长沟:

L`≈L,导电沟道区的等效电阻近似不变,饱和区电流饱和;实际器件(短沟):

L`②夹断区长度

③修正后的漏源电流

④影响因素

衬底掺杂浓度N越小⇒ΔL的绝对值越大⇒沟道长度调制效应越显著;

沟道长度L越小⇒ΔL的相对值越大⇒沟道长度调制效应越显著

3.迁移率变化

①概念:

MOSFET载流子的迁移率理想情况下:

近似为常数;实际受沟道内电场的影响,迁移率非常数。

VGS↑→垂直电场↑→漂移运动的电子更接近于氧化层和半导体的界面→表面散射增强,载流子的表面迁移率μ下降

②影响:

漏电流、跨导随栅压增加而增加的趋势减缓

4.速度饱和

①概念:

E较低时,μ为常数,半导体载流子漂移速度v与沟道方向电场E正比;E较高时,达到一临界电场EC时,载流子漂移速度v将达到饱和速度vSat,使载流子的μ下降

②影响:

使电流饱和

原因:

③易发生情况:

短沟器件,U大L小,E大,易达到饱和Ec

④考虑速度饱和后的饱和漏源电流

⑤跨导:

与偏压、沟长无关

⑥截止频率:

与偏压无关

5.弹道输运

特点:

①沟道长度L<0.1μm,小于散射平均自由程

②载流子从源到漏运动大部分没有一次碰撞

③高速器件:

不经散射的速度大于经历散射的平均漂移速度

非弹道输运特点:

沟道长度L>0.1μm,大于散射平均自由程;载流子从源到漏运动需经过多次散射;因经历多次散射,载流子运动速度用平均漂移速度表征

2.2按比例缩小

按比例缩小的参数:

器件尺寸参数(L,tox,W,xj):

k倍

掺杂浓度(Na,Nd):

1/k倍

电压V:

k倍

电场E:

1倍

耗尽区宽度Xd:

k倍

电阻R(与L/W成正比):

1倍;

总栅电容(与WL/tox成正比):

k倍

漏电流I(与WV/L成正比):

k倍

2.3阈值电压调整

1.短沟道效应(L↓⇒VT↓)

①概念:

随着沟长L变短,栅压VG可控空间电荷区仅仅为下方梯形→可控耗尽层电荷占耗尽层越来越少→使得可控Qsd变小,VT下降

②影响因素:

a.L↓→VTN↓b.Na↑→VTN↓c.VDS>0→漏衬n+p反偏压↑→Qsd↓→VTN↓d.VSB↑→VTN↓(ΔVT绝对值更大,使VT整体减小)

2.窄沟道效应(W↓⇒VT↑)

概念:

表面耗尽层在宽度方向将存在横向展宽现象→VGS作用下要产生中间矩形和两侧的耗尽层电荷→W越小,相同偏压VG下能用来控制下方矩形部分的电压V越少→VT随W的↓而增大

3.离子注入调整

①原理:

通过离子注入技术向沟道区注入杂质

a.p型衬底表面注入受主杂质(如B)→半导体表面净掺杂浓度Na↑→/Q`SDmax/↑→表面更难以反型→VT↑

b.p型衬底表面注入施主杂质(如P)→半导体表面净掺杂浓度Na↓→/Q`SDmax/↓→表面更容易反型→VT↓

②离子注入关系

P型衬底加入受主杂质:

2.4击穿特性

1.栅氧化层击穿

①概念:

VGS↑→氧化层电场强度Eox≥临界电场强度EB,氧化层发生介电击穿,栅衬短路,栅电流产生

②影响因素:

静电使栅两侧出现电荷积累,易产生强电场使之击穿

③措施:

a.设计和使用做好防静电措施

b.进行电路设计

2.漏衬pn结雪崩击穿(沟道未形成)

①概念:

结反偏压VDS大到一临界值BVDS,发生雪崩击穿

②雪崩击穿:

载流子从大E获得大能量,与晶格原子碰撞→共价键断裂,产生电子空穴对→产生的电子空穴也会从E获得能量,继续碰撞→产生大量的电子被漏极收集(加入ID),发生击穿,产生的空穴注入衬底(产生Isub)

③影响因素:

a.击穿电压BVnp,其为轻掺杂侧掺杂浓度Na的函数

b.MOSFET漏衬PN结的BVDS耗尽区的电场在拐角处(棱角电场)容易集中,大于平面处电场

3.沟道雪崩倍增效应(VGS>VT)

①概念:

发自S端的载流子,形成电流IS,进入沟道区,受沟道E的加速→在D端附近发生雪崩倍增→产生的电子被漏极收集(加入ID),产生的空穴注入衬底(产生Isub)

②影响因素:

a.VDS越大,E越强,越容易诱发倍增

b.VGS越大,沟道载流子数越多,倍增越快,BVDS越小

4.寄生晶体管击穿(雪崩击穿正反馈)

①概念

前提:

MOSFET存在寄生的双极型晶体管

雪崩击穿→存在衬底电流Isub,同时Rsub不为零→寄生晶体管基极电势增高,使源衬结正偏→电子由重掺源区扩散至衬底,一部分电子加入ID使ID↑→雪崩击穿加剧(正反馈)

②易发生情况:

短沟高阻衬底的MOSFET

a.短沟,基区较窄,注入沟道区的电子易被漏极收集,同时漏结附近的E较强,倍增效应强

b.高阻,Rsub大

③措施:

重掺衬底

5.源漏穿通效应(短沟器件)

①概念:

漏衬结的空间电荷区扩展至和源衬结空间电荷区相接→导致源端和源漏之间半导体的势垒高度降低→电子跨越势垒高度由源区注入到源漏之间半导体区的几率增加

②影响:

a.VGS=0时,源和沟道区势垒高度被拉更低→源区电子注入到沟道区数量增多→亚阈值电流增加

b.VDS↑→源和沟道区势垒高度降低→ID指数↑→栅压控制器件ID能力下降

②易发生情况:

短沟高阻衬底的MOSFET

③措施:

增大栅氧下方会发生穿通效应的衬底浓度NB、增大VSB

6.LDD结构的MOSFET

①定义:

轻掺杂漏结构(LightlyDopedDrain)

②概念:

在沟道的漏端及源端增加低掺杂区,降低沟道端口处的掺杂浓度及掺杂浓度的分布梯度

③作用:

降低沟道中漏附近的电场,提高器件的击穿电压

2.5辐射效应与热载流子效应

1.辐射效应

①概念:

x射线、γ射线等离化辐射将SiO2中的电子-空穴对打开,同时产生自由电子和自由空穴

②影响:

a.产生氧化层电荷

b.产生界面态

c.辐射总剂量越大,曲线斜率小,亚阈值摆幅增大

2.热载流子效应

①热载流子定义:

热载流子有效温度Te高,若环境温度为T,则平均能量(kTe)大于晶格能量(kT)的载流子。

MOSFET的热载流子,从VDS产生的E获得能量

②影响

a.热载流子(能量高)越过Si-SiO2界面势垒注入到SiO2层中→被氧化层陷阱俘获,氧化层电荷变化

b.热载流子越过界面,会打开Si-O键,产生界面态,使界面陷阱电荷变化

c.表面散射增强,使迁移率下降

d.被栅极收集,形成栅电流

③特点:

是连续过程、易发生于短沟器件

④措施:

采用轻掺杂漏结构(LDD)

原因:

漏区掺杂浓度较低且分布梯度较缓,电力线不易集中,沟道中漏附近的电场降低;减缓热载流子的产生;减缓雪崩击穿效应,寄生双极晶体管击穿效应

3.1JFET场效应管与MESFET

1.MESFET基本结构

2.肖特基二极管特点

①反向饱和电流数量级更高

②多子器件,无扩散电容无少子存储效应,开关特性好

3.2JFET理想直流特性

1.内建夹断电压Vp0:

沟道夹断时栅结总压降,Vp0>0

2.夹断电压Vp:

沟道夹断时的栅源电压,根据沟道类型可正可负

3.直流特性

①近似公式:

,IDSS为VGS=0时的沟道漏电流

②阈电流:

,为JFET在VGS,Vbi均为0时的最大漏电流,无空间电荷区

注意上式和Nd有关,即漏电流与掺杂浓度成正相关;因此跨导gm也与掺杂浓度正相关

3.3JFET等效电路和频率限制

1.提高fT的方法

①减小栅长

②降低栅电容

③增加跨导

④提高迁移率

2.二维电子气:

2DEG指在两个方向上可以自由运动,而在第三个方向上的运动受到限制的电子群

3.4高电子迁移率晶体管

1.量子阱结构

2.HEMT器件结构

考试时只需要自上而下画出:

源栅漏、n-AlGaAs、(I-AlGaAs隔离层)I-GaAs、sub-GaAs即可拿满分

隔离层作用:

减弱电离杂质的库仑力对电子的影响,这样能更进一步提高电子迁移率

3.GaN材料优势

①宽禁带,温度稳定性、辐射稳定性好

②BV高,高功率

③ΔEC高,形成高二维电子气浓度

④热导率高

欢迎您的下载,

资料仅供参考!

致力为企业和个人提供合同协议,策划案计划书,学习课件等等

打造全网一站式需求