计算机接口技术第2章0911讲义11.docx

《计算机接口技术第2章0911讲义11.docx》由会员分享,可在线阅读,更多相关《计算机接口技术第2章0911讲义11.docx(32页珍藏版)》请在冰豆网上搜索。

计算机接口技术第2章0911讲义11

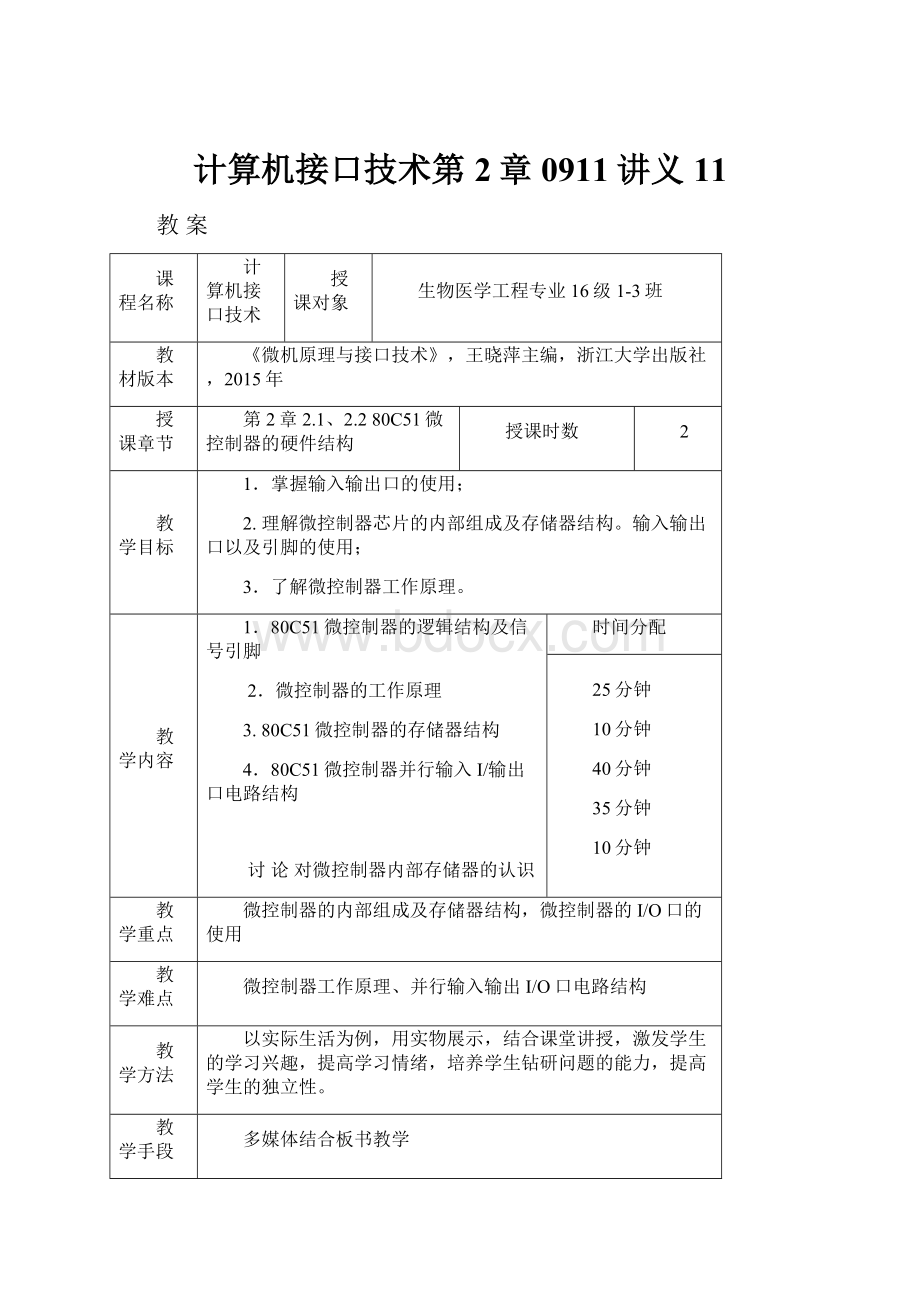

教案

课程名称

计算机接口技术

授课对象

生物医学工程专业16级1-3班

教材版本

《微机原理与接口技术》,王晓萍主编,浙江大学出版社,2015年

授课章节

第2章2.1、2.280C51微控制器的硬件结构

授课时数

2

教学目标

1.掌握输入输出口的使用;

2.理解微控制器芯片的内部组成及存储器结构。

输入输出口以及引脚的使用;

3.了解微控制器工作原理。

教学内容

1.80C51微控制器的逻辑结构及信号引脚

2.微控制器的工作原理

3.80C51微控制器的存储器结构

4.80C51微控制器并行输入I/输出口电路结构

讨论对微控制器内部存储器的认识

时间分配

25分钟

10分钟

40分钟

35分钟

10分钟

教学重点

微控制器的内部组成及存储器结构,微控制器的I/O口的使用

教学难点

微控制器工作原理、并行输入输出I/O口电路结构

教学方法

以实际生活为例,用实物展示,结合课堂讲授,激发学生的学习兴趣,提高学习情绪,培养学生钻研问题的能力,提高学生的独立性。

教学手段

多媒体结合板书教学

课后作业

教材第二章:

练习题

(一)、

(二)相关题

参考资料

1.吴秀清、周荷琴.微控制器原理与接口技术.北京:

中国科学技术大学出版社,2009.

2.谢宜仁,微控制器实用技术问答,人民邮电出版社

课后分析

微控制器工作原理、并行输入输出I/O口电路结构仔细讲

长治医学院生物医学工程系信息技术教研室2018年9月11日

授课教师:

郝文延职称:

副教授

基本内容

备注及时间分配

第2章8051微控制器硬件结构

第2章8051微控制器硬件结构

内容提要

本章内容分为9个教学单元,主要包括8051微控制器的结构、工作原理,内部存储器配置与地址空间,特殊功能寄存器SFR的功能与作用,I/O端口结构与特点,时钟与复位,微控制器的工作方式,以及8051微控制器的技术发展等。

2.1微控制器结构

2.2微控制器的工作原理

2.3存储器结构与地址空间

2.4P0-P3端口结构与特点

2.1微控制器结构

图2-1中这些部件通过内部总线连接起来,基本结构仍然是通用CPU加上外围芯片的结构模式,但功能单元上的控制与先前相比有重大变化,采用了特殊功能寄存器(SFR:

SpecialFunctionRegisters)进行集中控制的方法。

2.1.2功能特点

1.CPU(中央处理器),是微控制器的核心,包括运算器和控制器两部分电路,主要完成运算和控制功能,又增设了“面向控制”的处理功能,增强了实时性。

2.数据存储器(RAM)分为:

内部(256B),外部(64KB)

3.程序存储器(ROM)

分为:

内部(4-64KB),外部(64KB)

4.中断系统

具有内、外共5个中断源,即外中断两个,定时/计数中断2个,串行中断1个。

全部中断分为高级和低级2个中断优先级。

5.定时器/计数器

80C51共有2个16位的定时器/计数器,80C52则有3个16位的定时器/计数器。

具有4种工作方式。

6.串行I/O口

目前高档8位微控制器均设置了全双工的通用异步接收和发送器UART,具有4种工作方式,可以进行串行通信和串行扩展I/O接口。

7.4个8位并行I/O口

单片机往往提供了许多功能强、使用灵活的并行输入/输出引脚,用于检测与控制。

有些I/O引脚还具有多种功能,比如可以作为数据总线的数据线、地址总线的地址线、控制总线的控制线等。

单片机I/O引脚的驱动能力也逐渐增大,甚至可以直接驱动外扩的LED显示器。

80C51有四个8位的I/O口(P0、P1、P2、P3),以实现数据的并行输入输出。

8.布尔处理器(位处理器)

微控制器主要用于控制,需要有较强的位处理功能,因此,位处理器是必要的,也称为布尔处理器。

9.时钟电路

10.指令系统

有5大功能,共111条指令,采用复杂指令系统(CISC)。

11.总线

2.1.3引脚与功能

1.封装形式

80C51有40引脚双列直插(DIP)、44引脚(PLCC)和44引脚(PQFP/TQFP)封装形式。

80C51/80C52的封装及逻辑图如图2-2a所示。

在某些场合,不需通过并行总线扩展芯片,这时常采用20引脚双列直插(DIP)甚至仅14引脚的单片机,如ATMEL公司的1051/2051/4051单片机等,或PHILIPS公司的P87LPC764单片机。

它们的封装及引脚见图2-2b。

图2-2a80C51/80C52的封装及逻辑图

图2-2bAT89C2051/P87LPC764的封装及逻辑图

AT89C51和AT89C2051主要性能表

由于AT89C2051的IO线很少,导致它无法外加RAM和程序ROM,片内Flash存储器也少,但它的体积比AT89C51小很多,在开发工作中可根据实际需要来选用。

它们各有其特点,但其核心是一样的。

芯片封装简介

DIP(DualIn-linePackage)双列直插式封装

PLCC(PlasticLeadedChipCarrier)带引线的塑料芯片封装

PQFP(PlasticQuadFlatPackage),一般大规模或超大型集成电路都采用这种封装形式,其引脚数一般在100个以上。

PGA(PinGirdArraypackage)插针网格阵列封装

ZIF(ZeroInsertionForcesocket)是指零插拔力的插座。

贴片封装

随着生产技术的提高,电子产品的体积越来越小,体积较大的直插式封装集成电路已经不能满足需要。

故设计者又研制出一种贴片封装的集成电路,这种封装的集成电路引脚很小,可以直接焊接在印制电路板的印制导线上。

贴片封装的集成电路主要有薄型QFP(TQFP)、细引脚间距QFP(VQFP)、缩小型QFP(SQFP)、塑料QFP(PQFP)、金属QFP(MetalQFP)、载带QFP(TapeQFP)、J型引脚小外形封装(SOJ)、薄小外形封装(TSOP)、甚小外形封装(VSOP)、缩小型SOP(SSOPShrinkSmallOutlinePackage)、薄的缩小型SOP(TSSOP)及小外形集成电路(SOIC)(SmallOutlinePackage)等派生封装。

芯片标号的识别

eg:

STC89C51RC40C-PDIP0707

STC-前缀,表示该芯片为STC公司生产的产品。

其他前缀有AT,i,SST等。

8-表示该芯片为8051内核芯片。

9-表示内部含FlashE2PROM存储器。

还有如80C51中0表示内部含MaskROM(掩膜ROM)存储器;如87C51中7表示内部含EPROM存储器。

C-表示该器件为CMOS产品。

还有如89LV52和89LE58中的LV、LE都表示该芯片为低电压产品(通常为3.3V电压供电);而89S52中的S表示该芯片含有可串行下载功能的Flash存储器,即具有ISP可在线编程功能。

5-固定不变。

1-表示该芯片内部程序存储空间的大小,1为4KB,2为8KB,3为12KB,即该数乘上4KB就是该芯片内部的程序存储空间的大小。

RC-STC单片机内部RAM为512B。

40-表示芯片外部晶振最高可接入40MHZ。

对AT单片机数值一般为24,表示其外部晶振最高为24MHZ。

C-产品级别,表示芯片使用温度范围。

C表示商业级,温度范围为0℃—+70℃。

PDIP-产品封装型号。

PDIP表示双列直插式。

0707-表示本批芯片生产日期为07年第7周。

例:

STC12LE5630AD-35I-LQFP32

2.引脚功能

芯片按引脚的功能可分为三部分:

(1)电源和时钟:

·Vcc——运行和程序校验时接电源正端。

·Vss——接地。

·XTAL1——片内振荡器的反相放大器输入端。

·XTAL2——片内振荡器的反相放大器输出端。

图 80C51的振荡器方式

对于80C51,使用外部振荡器时,外部振荡信号应直接加到XTAL1,而XTAL2悬空。

内部方式时,晶振的频率可以在1MHz-24MHz内选择。

微调电容取30PF左右(见图所示)。

(2)控制线:

共4根。

·RST:

复位信号输入,高电平有效。

在振荡器工作时,在RST上作用两个机器周期以上的高电平,将器件复位。

——

(VPD:

备用电源引入端,当电源发生故障,电源降到下限值时,备用电源经此端向内部RAM提供电压,以保护内部RAM中的数据不丢失)·

/EA(Vpp:

编程电压,具体电压值视芯片而定)——片外程序存储器访问允许信号,低电平有效。

/EA=1,选择片内程序存储器(80C51为4KB,80C52为8KB);/EA=0,则程序存储器全部在片外而不管片内是否有程序存储器。

·/PSEN——片外程序存储器读选通信号,低电平有效。

在从片外程序存储器取指期间,在每个机器周期中,当其有效时,程序存储器的内容被送上P0口(数据总线)。

它可以驱动8个LSTTL负载。

·ALE(PROG:

编程脉冲)——地址锁存允许信号,输出。

在访问片外存储器或I/O时,用于锁存低八位地址,以实现低八位地址与数据的隔离。

即使不访问外部存储器,ALE端仍以固定的频率输出脉冲信号(此频率是振荡器频率的1/6)。

在访问外部数据存储器时,出现一个ALE脉冲。

ALE可以驱动8个LSTTL负载。

对片内程序存储器编程时,该引脚用于输入编程脉冲PROG。

(3)I/O引脚:

共4个口,32根I/O线。

·P0——8位、漏极开路的双向I/O口。

当使用片外存储器(ROM及RAM)时,作低八位地址和数据总线分时复用。

P0口(作为总线时)能驱动8个LSTTL负载。

·P1——8位、准双向I/O口。

在编程/校验期间,用做输入低位字节地址。

P1口可以驱动4个LSTTL负载。

·P2——8位、准双向I/O口。

当使用片外存储器(ROM及RAM)时,输出高8位地址。

在编程/校验期间,接收高位字节地址。

P2口可以驱动4个LSTTL负载。

·P3——8位、准双向I/O口,具有内部上拉电路。

P3提供了各种替代的第二功能。

在提供这些功能时,其输出锁存器应由程序置1。

P3口可以驱动4个LSTTL负载。

P3口第二功能(实际使用时,总是按需要优先选择第二功能,剩下不用的才作口线使用),P3口第二功能见表2-1所示(教材P34)。

PinoutDescription

Pins1-8:

Port1Eachofthesepinscanbeconfiguredasaninputoranoutput.

Pin9:

RSAlogiconeonthispindisablesthemicrocontrollerandclearsthecontentsofmostregisters.Inotherwords,thepositivevoltageonthispinresetsthemicrocontroller.Byapplyinglogiczerotothispin,theprogramstartsexecutionfromthebeginning.

Pins10-17:

Port3Similartoport1,eachofthesepinscanserveasgeneralinputoroutput.Besides,allofthemhavealternativefunctions:

Pin10:

RXDSerialasynchronouscommunicationinputorSerialsynchronouscommunicationoutput.

Pin11:

TXDSerialasynchronouscommunicationoutputorSerialsynchronouscommunicationclockoutput.

Pin12:

INT0Interrupt0input.

Pin13:

INT1Interrupt1input.

Pin14:

T0Counter0clockinput.

Pin15:

T1Counter1clockinput.

Pin16:

WRWritetoexternal(additional)RAM.

Pin17:

RDReadfromexternalRAM.

Pin18,19:

X2,X1Internaloscillatorinputandoutput.Aquartzcrystalwhichspecifiesoperatingfrequencyisusuallyconnectedtothesepins.Insteadofit,miniatureceramicsresonatorscanalsobeusedforfrequencystability.

Pin20:

GNDGround.

Pin21-28:

Port2Ifthereisnointentiontouseexternalmemorythentheseportpinsareconfiguredasgeneralinputs/outputs.Incaseexternalmemoryisused,thehigheraddressbyte,i.e.addressesA8-A15willappearonthisport.Eventhoughmemorywithcapacityof64Kbisnotused,whichmeansthatnotalleightportbitsareusedforitsaddressing,therestofthemarenotavailableasinputs/outputs.

Pin29:

PSENIfexternalROMisusedforstoringprogramthenalogiczero(0)appearsoniteverytimethemicrocontrollerreadsabytefrommemory.

Pin30:

ALEPriortoreadingfromexternalmemory,themicrocontrollerputstheloweraddressbyte(A0-A7)onP0andactivatestheALEoutput.AfterreceivingsignalfromtheALEpin,theexternalregister(usually74HCT373or74HCT375add-onchip)memorizesthestateofP0andusesitasamemorychipaddress.Immediatelyafterthat,theALUpinisreturneditspreviouslogicstateandP0isnowusedasaDataBus.Asseen,portdatamultiplexingisperformedbymeansofonlyoneadditional(andcheap)integratedcircuit.Inotherwords,thisportisusedforbothdataandaddresstransmission.

Pin31:

EAByapplyinglogiczerotothispin,P2andP3areusedfordataandaddresstransmissionwithnoregardtowhetherthereisinternalmemoryornot.Itmeansthateventhereisaprogramwrittentothemicrocontroller,itwillnotbeexecuted.Instead,theprogramwrittentoexternalROMwillbeexecuted.ByapplyinglogiconetotheEApin,themicrocontrollerwillusebothmemories,firstinternalthenexternal(ifexists).

Pin32-39:

Port0SimilartoP2,ifexternalmemoryisnotused,thesepinscanbeusedasgeneralinputs/outputs.Otherwise,P0isconfiguredasaddressoutput(A0-A7)whentheALEpinisdrivenhigh

(1)orasdataoutput(DataBus)whentheALEpinisdrivenlow(0).

Pin40:

VCC+5Vpowersupply.

80C51MemoryStructure

EA=0Inthiscase,themicrocontrollercompletelyignoresinternalprogrammemoryandexecutesonlytheprogramstoredinexternalmemory.

EA=1Inthiscase,themicrocontrollerexecutesfirsttheprogramfrombuilt-inROM,thentheprogramstoredinexternalmemory.

Inbothcases,P0andP2arenotavailableforusesincebeingusedfordataandaddresstransmission.Besides,theALEandPSENpinsarealsoused.

2.2微控制器工作原理

2.2.1CPU的结构和组成

CPU的组成结构:

CPU由运算器和控制器两大部分组成。

运算器是用来对数据进行算术运算和逻辑操作的执行部件;控制器是统一指挥和控制微控制器工作的部件。

(1)控制器电路

控制电路是微控制器的指挥控制部件,保证MCU各部分能自动而协调地工作。

控制器电路包括:

PC(ProgramCounter)、PC递增器、指令寄存器IR、指令译码器ID、定时与控制逻辑PLA等。

MCU执行指令是在控制电路的控制下进行的。

执行一条指令的大致过程:

读出指令->指令寄存器->指令译码器(译码)->定时与控制逻辑电路(由控制定时逻辑电路产生各种定时和控制信号,然后送往系统各部件去进行相应的操作)。

(2)运算器电路

运算电路是微控制器的运算部件,用于实现算术和逻辑运算。

运算器电路包括:

ALU(ArithmeticLogicUnit)、ACC(累加器)、B寄存器、程序状态字PSW(ProgramStatusWord)、TEMP1和TEMP2两个暂存器等。

运算电路以ALU为核心,基本的算术和逻辑运算均在其中进行,运算和操作的状态由PSW状态寄存器保存。

2.2.2微控制器的工作过程

指令是CPU能执行的一个基本操作,CPU的设计者对CPU的所有指令进行编码,用户用编码形式的指令进行编程,程序存放在内存中,CPU从内存取来编码形式的指令,对指令进行译码,发出执行该指令功能所需的信号。

工作过程:

取指令→分析指令→执行指令→取指令→分析指令→执行指令、、、

2.3存储器结构与地址空间

普林斯顿结构:

程序和数据共用一个存储器逻辑空间,统一编址。

哈佛结构:

程序与数据分为两个独立存储器逻辑空间,分开编址。

2.3.1存储器配置物理空间与地址

物理结构上有4个存储器空间

程序存储器:

片内程序存储器;片外程序存储器。

数据存储器:

片内数据存储器;片外数据存储器

.逻辑上有3个存储器地址空间

片内、片外统一的64KB程序存储器地址空间;

片内256B(80C52为384B)数据存储器地址空间;片外64KB的数据存储器地址空间。

2.3.2程序存储器

1.ROM的空间与地址

80C51单片机的程序存储器(programmemory)用于存放经调试正确的程序和表格之类的固定常数。

由于采用16位的程序计数器PC和16位的地址总线,因而其可直接扩展的地址空间为64KB。

2.ROM的编址重叠问题

整个程序存储器可以分为片内和片外两部分CPU访问片内和片外存储器,可由/EA引脚所接的电平来确定:

3.程序存储器某些单元被保留用于特定的程序入口地址

由于系统复位后的PC地址为0000H,故系统从0000H单元开始取指,执行程序。

从0003H~002DH单元被保留用于6个中断源的中断服务程序的入口地址。

2.3.3数据存储器RAM

数据存储器(datamemory)由随机存取存储器RAM构成,用来存放采集数据、中间结果、控制参数、传送数据。

在80C51中,数据存储器又分片内数据存储器(internaldatamemory)和片外数据存储器(externaldatamemory)两部分。

1.内部数据存储器

片内数据存储器(IRAM)地址只有8位,因而最大寻址范围为256个字节。

在80C51中,设置有一个专门的数据存储器的地址指示器——数据指针DPTR,用于访问片外数据存储器(ERAM)。

数据指针DPTR也是16位的寄存器,这样,就使80C51具有64KB的数据存储器扩展能力。

片内数据存储器是最灵活的地址空间。

它在物理上又分成两个独立的功能不同的区。

•片内数据RAM区:

对80C51,为地址空间的低128B。

•特殊功能寄存器SFR区:

对80C51,为地址空间的高128B。

2.片内RAM配置

工作寄存器区:

字节地址:

00H~1FH位寻址区:

字节地址:

20H~2FH

位地址为:

00H~7FH用户RAM区/堆栈区:

字节地址:

一般使用30H~7FH

(1)工作寄存器区:

这是一个用寄存器直接寻址的区域,指令的数量最多,均为单周期指令,执行的速度最快。

从上图中可知,其中片内数据RAM区的0~31(00H~1FH),共32个单元,是4个通用工作寄存器组(见下表或教材P41表所示),每个组包含8个8位寄存器,