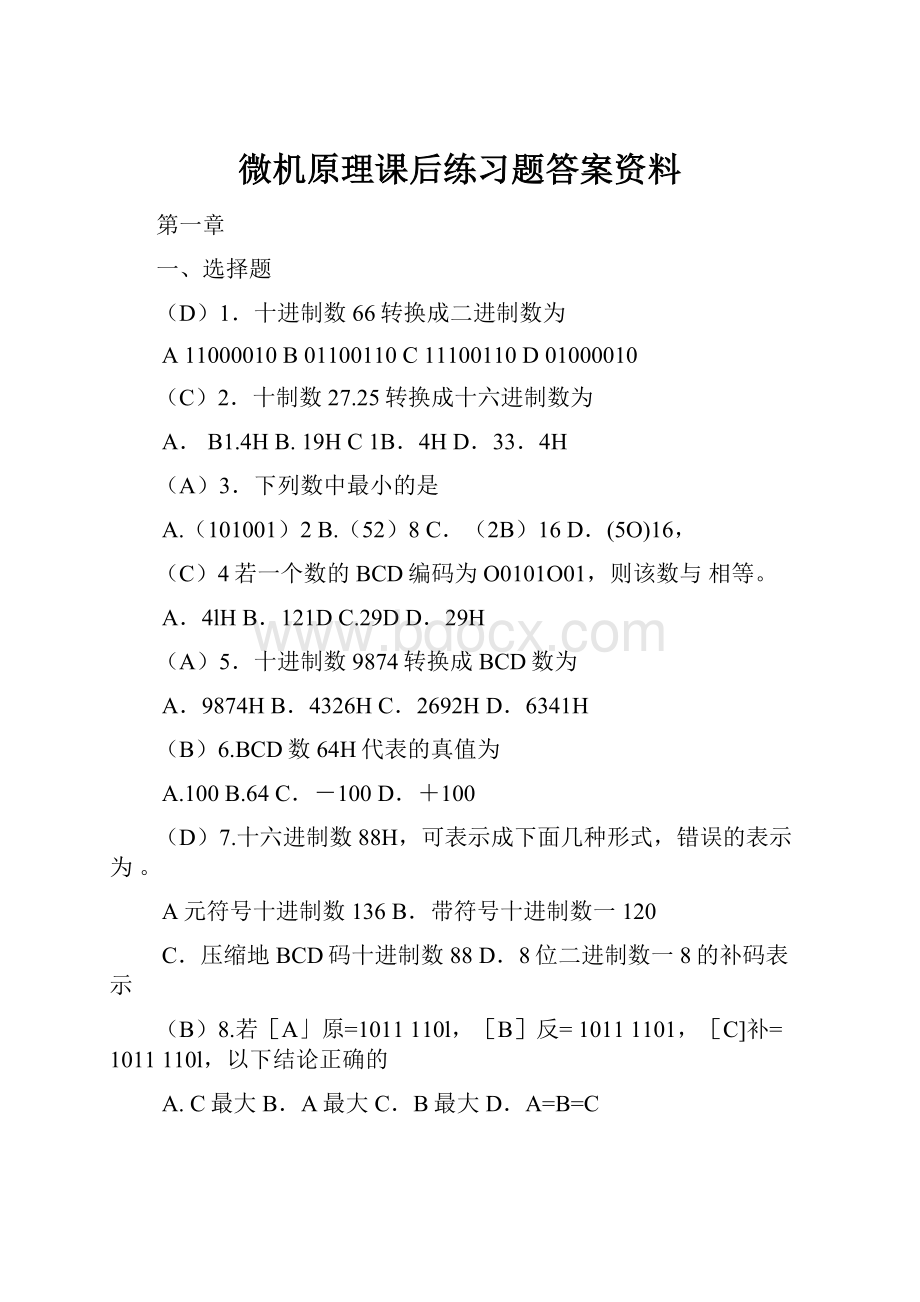

微机原理课后练习题答案资料.docx

《微机原理课后练习题答案资料.docx》由会员分享,可在线阅读,更多相关《微机原理课后练习题答案资料.docx(66页珍藏版)》请在冰豆网上搜索。

微机原理课后练习题答案资料

第一章

一、选择题

(D)1.十进制数66转换成二进制数为

A11000010B01100110C11100110D01000010

(C)2.十制数27.25转换成十六进制数为

A.B1.4HB.19HC1B.4HD.33.4H

(A)3.下列数中最小的是

A.(101001)2B.(52)8C.(2B)16D.(5O)16,

(C)4若一个数的BCD编码为O0101O01,则该数与相等。

A.4lHB.121DC.29DD.29H

(A)5.十进制数9874转换成BCD数为

A.9874HB.4326HC.2692HD.6341H

(B)6.BCD数64H代表的真值为

A.100B.64C.-100D.+100

(D)7.十六进制数88H,可表示成下面几种形式,错误的表示为。

A元符号十进制数136B.带符号十进制数一120

C.压缩地BCD码十进制数88D.8位二进制数一8的补码表示

(B)8.若[A」原=1011110l,[B]反=10111101,[C]补=1011110l,以下结论正确的

A.C最大B.A最大C.B最大D.A=B=C

(D)9.8位二进制补码表示的带符号数10000000B和11111lllB的十进制数分别

A128和25511.128和一1C.-128和255D.-128和一l

(C)10.微机中地址总线的作用是

A.用于选择存储器单元

B.用于选择进行信息传输的设备

C.用于指定存储器单元和I/o设备接口单元的选择地址

D.以上选择都不对

(A)11.计算机中表示地址使用

A.无符号数B.原码C.反码D.补码

二、填空题

(运算器)l.计算机的主机由、控制器、主存储器组成。

(冯·诺依曼、输出器、存储器、存储器)2.确定了计算机的5个基本部件:

输入器、、运算器、和控制器,程序和数据存放在中,并采用二进制数表示。

(16.B8H、52.59、1110010.01B)3.10110.10111B的的十六进制数是,34.97H的十进制数是,将114.25转换为二进制数为。

(1010000000、280)4.(640)10=()2=()16。

(100000000.011、100.6)5.(256.375)l0=()2=()16

(188.8125、0BC.D)6.(10111100.1101)2=()10=()16

(-1、-126、-127)7.二进制数10000001B若为原码,其真值为;若为反码,其真值为;若为补码,其真值为。

(-125)8.一个8位的二进制整数,若采用补码表示,且由3个“1”和5个“0”组成,则最小的十进制数为。

(尾数、指数)9在微机中,一个浮点数由和两个部分构成。

(-16、-111、-112)10.若[X]原=[y]反=[z]补=90H,试用十进制分别写出其大小,X=:

Y=;Z=。

三、问答题

1.在计算机中为什么都采用二进制数而不采用十进制数?

二进制数有哪两种缩写形式?

答:

计算机中使用的都是数字逻辑器件,只能识别高、低两种状态的电位,所以计算机处理的所有信息都以二进制的形式表现。

二进制的两种缩写形式有八进制、十六进制。

2.什么是程序计数器PC?

答:

存放着将要执行的下一条指令的地址的寄存器,具有自动加1的功能。

3.已知[X]补=10011101B,「[Y补=11001001,[Z]补=0010011BB,计算[X+Y]补=?

,并指出是否溢出;计算[X一Z]补=?

.并指出是否溢出。

答:

[X+Y]补=[X]补+[Y]补=101100110最高位符号发生变化,产生溢出

[X一Z]补=[X]补+[-Z]补=101110111最高位符号发生变化,产生溢出

4.将下列十六进制数的ASCll码转换为十进制数。

(1)313035H

(2)374341H(3)32303030H(4)38413543H

答:

(1)105

(2)1994(3)8192(4)35420

第二章

一、选择题

(C)1.8086/8088CPU内部有一个始终指示下条指令偏移地址的部件是___。

A.SPB.CSC.IPD.BP

(D)2,指令队列的作用是

A.暂存操作数地址B.暂存操作数

C.暂存指令地址D.暂存预取指令

(A)3.8086/8088下列部件中与地址形成无关的是_______。

A.ALUB.通用寄存器C.指针寄存器D.段寄存器

(B)4.对于8086,下列说法错误的是_。

A.段寄存器位于BIU中B.20位的物理地址是在EU部件中形成的

C.复位后CS的初值为FFFFHD.指令队列的长度为6个字节

(D)5.8086/8088中ES、DI分别属于

A.EU、BIUB.EU、EUC.BIU、BIUD.BIU、EU

(A)6.BIU与EU工作方式的正确说法是_。

A并行但不同步工作B.同步工作

C.各自独立下作D.指令队列满时异步工作,空时同步工作

(A)7.在执行转移、调用和返回指令时,指令队列中原有的内容______。

A、自动清除B.用软件清除

C.不改变D.自动清除或用软件清除

(D)8.下列说法中,正确的一条是

A.8086/8088标志寄存器共有16位,每一位都有含义

B.8088/8086的数据总线都是16位

C.8086/8088的逻辑段不允许段的重叠和交叉

D.8086/8088的逻辑段空间最大为64KB,实际应用中可能小于64KB

(C)9.8086/8088工作于最大模式,是因为______。

A.可以扩展存储容最B.可以扩大I/O字间

C.可以构成多处理器系统D.可以提高CPU主频

(B)10.8086/8088最大模式比最小模式在结构上至少应增加

A.中断优先级控制器B.总线控制器

C.数据驱动器D.地址锁存器

(D)11.组成最大模式下的最小系统,除CPU、时钟电路、ROM、RAM及l/O接口外,至少需增加的芯片类型为。

a.总线控制器b.总线裁决器c.地址锁存器d.总线驱动器

A.b,dB.a,b,cC.a,dD.a,c.d

(A)12.工作在最小模式时.对CPU而言.下列信号皆为输人信号的是。

A.HOLD、TEST、READYB.M/IO、TEST、READY

C.M/IO、HOLD、TESTD、DT/R、HOLD、READY

(A)13.LOCK引脚的功能是

A.总线锁定B.地址锁定C.数据输入锁定D,数据输出锁定

(A)14.与存储器或外设同步以及与协处理器同步的引脚信号依次为

A.READY、TESTB.READY、HOLD

C.LOCK、RESETD.TEST、LOCK

(A)15.工作在最大模式时,下列信号皆为输出信号的是

A.QS0、QS1、LOCKB.QS0、RA/GT0、LOCK

C.QS1、RQ/GT1、S0D.RQ/GT0、QS1、BHE

(C)16.8086/8088最大模式时,LOCK引脚有效时的正确含义是

A.能中断CPU的工作B.能进行DMA操作

C.其他总线部件不能占有总线D.暂停CPU的了作

(C)17.工作在最大模式时,一经总线控制器8288将对应CPU最小模式时的3个引脚状态进行组合,产生控制和命令信号,这3个引脚应为

A.MN/MXM/IODT/RB.DENM/IOMN/MX

C.M/IODT/RMN/MXD.DENDT/RMN/MX

(B)18.8088/8086中,关于总线周期叙述不正确的是

A总线周期通常由连续的T1~T4。

组成

B.在读写操作数时才执行总线周期

C.总线周期允许插入等待状态

D.总线周期允许存在空闲状态

(B)19.在8086读总线同期中,进入T3后发现READY=0,需要插入等待状态.则在插入等待状态时其引脚的高地址A19~A16。

A.表示读数据对应的高4位的地址

B.表示CPU当前工作状态

C.处于高阻状态

D.处于不定状态

(D)20.设8086/8088工作于最小模式,在存储器读、写周期中.总线ADl5~AD0上数据开始有效的时刻(不插入TW)分别是。

A.T2,T2B.T2、T3C.T3、T4D.T3、T2

二、填空题

(BIU、EU、独立)l.8086,8088CPU在结构上由两个独立的处理单元和构成,这两个单元可以工作,从而加快了程序的运行速度。

(ES、SS、CS、DS、IP、AX、BX、CX、DX、BP、SP、SI、DI)2.8086是intel系列的16位处理器,从功能上,它分为两个部分:

即总线接口单元和执行单元。

总线接口单元由、、、、等寄存器和20位地址加法器和6字节指令队列构成。

执行单元有4个通用寄存器,即、、、;4个专用寄存器,即、、、等寄存器和算术逻辑单元组成。

(FR、ZF)3.任何CPU都有一个寄存器存放程序运行状态的标志信息,在8086中,该奇件器是。

其中,根据运算结果是否为零,决定程序分支走向的标志位是。

(TF、DF、IF)4.8086/8088CPU中标志寄存器的3个控制位是、、。

(9E100H)5.逻辑地址9B50H:

2C00H对应得物理地址是。

(高电平)6.在任何一个总线周期的T1状态,ALE输出。

(MV/_______MX、一个处理器、多个处理器)7.8086有两种工作模式,即最小模式和最大模式,它由决定。

最小模式的特点是,最大模式的特点是。

(________BHE、A0、A0~A18)8.8086CPU可访问的存储器的空间为1MB,实际上分奇数存储体和偶数存储体两部分,对奇数存储体的选择信号是,对于偶数存储体的选择信号是,对于每个存储体内的存储单元的选择信号是。

(读I/O端口)9.在8086的最小系统,当M/______IO=0,_______WR=1,_______RD=0时,CPU完成的操作是。

(0、0、1、1)10.在最小模式下,执行“OUTDX,AL”指令时,M/____IO、_______WR、_______RD、DT/___R的状态分别是、、、。

(1、2)11.8086CPU从偶地址读写两个字节时,需要个总线周期,从奇地址读取两个字节时,需要个总线周期。

(1、0、0)12.8086在存取存储器中以偶地址为起始地址的字时,M/____IO、________BHE、A0的状态分别是、、。

(0、1)13.8086向内存地址1200Bll写一个字节数据时,需要一个总线周期,在该总线周期的T1状态,_________BHE为,A0为。

(3)14.假设某个总线周期需插入两个TW等待状态,则该总线日期内对READY信号检测的次数是。

(FFFFH、0000H、0000H、0000H)15.8086CPU上电复位后,CS=,IP=,DS=,标志寄存器FR=。

(4)16.8086/8088的复位信号至少要维持个时钟周期。

(DT/____R、_______RD、________WR、M/_____IO、__________DEN)17.8086CPU工作在最小模式下,控制数据流方向的信号是、、、、。

(READY、Tw)18.当存储器的读出时间大于CPU所要求的时间时,为了保证CPU与存储器的周期配合,就要利用信号,使CPU插入一个状态。

(队列为空)19.当8086/8088工作于最大模式时,QS0=1,QS1=0,其表示指令队列的状态为。

(0)20.在T2、T3、TW、T4状态时,S6为,表示8086/8088表示当前连在总线上。

(INTR、NMI、屏蔽)21.8086/8088提供的能接受外中断请求信号的引脚是和。

两种情求信号的主要不同处在于是否可。

(1)22.一台微机的CPU,其晶振的主振频率为8MHz.二分频后作为CPU的时钟频率。

如果该CPU的一个总线周期含有4个时钟周期,那么此总线周期是us。

(时钟周期0.05μs、运算速度0.3μs)23.某微处理器的主频为20MHz。

,由2个时钟周期组成一个机器周期,设平均3个机器周期可完成一条指令,其时钟周期和平均运算速度分别为。

三、问答题

1.8086/8088CPU在结构上由哪两个独立的处理单元构成?

这样的结构最主要的优点是什么?

答:

由总线接口单元BIU和执行单元EU两部分。

这样的电路便于管理和设计电路。

执行单元EU专门负责指令的执行,总线接口单元BIU是从内存指定区域取出指令送到指令队列缓冲器。

EU和BIU两个功能部件并行工作,EU执行BIU在前一个时刻取出的指令,与此同时,BIU又取出下一时刻要执行的指令,由此能使大部分取指令和执行指令的操作重叠进行,大大缩短了等待指令所需的时间,提到了微处理器的利用率和整个系统的执行速度。

2.完成下列补码运算,并根据结果设置标志SF、ZF、CF和OF,指出运算结果是否溢出?

(1)00101101B+10011100B

(2)01011101B-10111010B

(3)876AH-0F32BH(4)10000000B十11111111B

(1)00101101B

+10011100B

11001001B=C9H

SF=1ZF=0CF=0OF=0

(2)-10111010B=01000110B

01011101B-10111010B=01011101B

+01000110B

10100011B

SF=1ZF=0CF=0OF=1

(3)876AH-0F32BH=876AH

+0CD5H

943FH

SF=1ZF=0CF=0OF=0

(4)10000000B

+11111111B

101111111B=7FH

SF=0ZF=0CF=1OF=1

3.存储器采用分段方法进行组织有哪些好处?

答:

8086微处理器CPU中寄存器都是16位,16位的地址只能访问大小为64K以内的内存。

8086系统的物理地址由20位地址空间进行访问,就需要两部分地址,在8086系统中,就是由段地址和偏移地址组成。

而这两个地址都是16位,在地址形成中,当段地址确定后,该段的寻址范围就已经确定,其容量不大于64KB。

同时,通过修改段寄存器的内容,可达到逻辑段在整个1MB空间中浮动。

各个逻辑段之间可以紧密相连,可以中间有间隔,也可以相互重叠。

这种方式的优点是:

满足对8086系统的1MB存储空间的访问空间的访问,同时在大部分指令中只要提供16位的偏移地址即可。

4.Intel8086/8088处理器芯片功能强大,但引脚数有限,为了建立其与外围丰富的信息联系,Intel8086/8088处理器引脚采用了复用方式,说明其采用了何种复用方式?

采用了地址/数据分时复用、地址/状态分时复用。

控制引脚的复用,在最大和最下模式下表现不同的功能。

5.8086CPU是怎样解决地址线和数据线的复用问题的?

ALE信号何时处于有效电平?

地址和数据是分时复用的,在与内存交换数据时,首先发出的是地址信号,然后发送数据信息到数据线上。

为了配合这种应用,在CPU芯片外需要为其配置相应的地址锁存器和双向数据缓冲器。

。

在总线周期的第一个时钟周期ALE输出高电平为有效电平,表示当前复用线上输出的是地址信息,ALE作为锁存信号,对地址进行锁存。

ALE端不能浮空。

6.8086/8088系统用的时钟发生器会产生哪些信号?

会产生4.77MHz的标准时钟信号CLK。

此时钟信号作为系统时钟,同时还对复位和就绪信号实现内部的时钟同步,然后再输出,实施对8086/8088的控制,时钟发生器产生恒定的时钟信号CLK,RESET,READY。

7.说明8086CPU的READY输入信号和—————TEST信号的作用是什么?

READY信号有效时,表示内存或外设准备就绪,马上就可以进行数据传输。

如果检测到READY信号为低电平,则在T3状态后插入等待状态Tw,直到READY信号有效时,停止插入等待状态Tw,进入T4状态,完成数据传输过程,从而结束当前总线周期。

—————TEST信号和WAIT指令结合起来使用,在CPU执行WAIT指令时,CPU处于等待状态,当—————TEST信号为低电平时,等待状态结束,CPU继续往下执行被暂停的指令。

习题3

一、选择题

D1.寻址方式指出了操作数的位置,一般来说。

A.立即寻址给出了操作数的地址

B.寄存器直接寻址的操作数在寄存器内,而指令给出了存储器

C.直接寻址直接给出了操作数本身

D.寄存器直接寻址的操作数包含在寄存器内,由指令指定寄存器的名称

A2.寄存器寻址方式中,操作数在。

A.通用寄存器B.堆栈C.内存单元D.段寄存器

C3.寄存器间接寻址方式中,操作数在。

A.通用寄存器B.堆栈C.内存单元D.段寄存器

B4.下列指令中的非法指令是。

A.MOV[SI+BX],AXB.MOVCL,280

C.MOV[0260H,2346HD.MOVBX,[BX]

A5.设(SP)=0100H,(SS)=2000H,执行PUSH指令后,栈顶的物理地址是。

A.200FEHB.0102HC.20102HD.00FEH

C6.指令“LEABX,TAB”执行后,其结果是。

A.将TAB中内容送BXB.将TAB的段基址送BX

C.将TAB的偏移地址送BXD.将TAB所指单元的存储内容送BX

D7,下列正确的指令格式有

A.MOV[SX],1B.MOVAL,0345H

C.MOVES:

PTR[CX],3D.XI。

入f

C8.设(AX〕=C544H,在执行指令“ADDAH,AL”之后,。

A.CF=0,OF=0B.CF=0,OF=1

C.CF=1,OF=0D.CF=1,OF=1

B9.若AL、BL中是压缩BCD数,在执行“ADDAL,BL”之后,(AL)=0CH,CF=1,AF=0。

若再执行DAA后,(AL)=

A.02HB.12HC.62HD.72H

C10,执行下列程序后AL的内容为_______。

MOVAL,25H

SUBAL,71H

DAS

A.B4HB.43HC.54HD.67H

A11.下列4条指令中,需要使用DX寄存器的指令是_____。

A.MULBXB.DIVBLC.INAX,20HD.OUT20H,AL

B12.设(AL)=0E0H,(CX)=3,执行“RCLAL,CL”指令后,CF的内容。

A.0B.1C.不变D.变反

A13.下列4条指令中,错误的是______。

A.SHLAL,CXB.XCHGAL,BL

C.MOVBX,[SI]D.ANDAX,BX

D14.串操作指令中,有REP前缀的串操作指令结束的条件是_______。

A.ZF=1B.ZF=0C.C>0D.ANDAX,BX

A15.对于下列程序段:

AGAIN:

MOVAL,[SI]

MOVES:

[DI],AL

INCSI

INCSI

LOOPAGAIN

也可用指令完成同样的功能。

A.REPMOVSBB.REPLODSB

C.REPSTOSBD.REPESCASB

A16.JMPWORDPTR[DI]是指令。

A.段内间接转移B.段内直接转移

C.段间间接转移D.段间直接转移

C17.条件转移指令JNE的转移条件是_______。

A.ZF=1B.CF=0C.ZF=0D.CF=1

D18.下列指令中,影响标志位的指令是____。

A.从存储器取数指令B.条件转移指令

C.压找指令D.循环移位指令

D19.假设外部设备的状态字已经读入AL寄存器,其中最低位为0,表示外部设备忙,为了判断外部设备是否忙而又不破坏其他状态位,应选用下列_______指令。

A.RCRAL,0lHB.CMPAL,00H

JZLabelJZLabel

C.ANDAL,01HD.TESTAL,01H

JZLabelJZLabel

C20.假定一组相邻字节的首地址在BX中,未地址在DI中,为了使下面的程序段能用来查找出其中第一个非零字节,并把它存放在AL中,在横线处应填入指令。

SUBDI,BX

INCDI

MOVCX,DI

NEXT:

INCBX

CMPBYTEPTR[BX],0

LOOPNEXT

MOVAL,BYTEPTR[BX]

A.MOVSI,CXB.SUBBX,BXC.DECBXD.INCBX

二、填空题

1.指令“MOV[BX十SI],AL”中的目的操作数使用段寄存器,属于寻址方式。

DS(数据段);基址加变址

3.若(BX)=42DAH,则下列指令段

PUSHBX

POPF

指令执行完销后,(SF,ZF,CF,OF)=。

1100

4.假设(DS)=1000H,(ES)=0200H,(BP)=0100H,(DI)=0200H,(10200H)=11H,(10201H)=12H,执行指令“LEAAX,TABLE”后;(AX)=。

0300H

5.假定(DS)=4000H,(DI)=0100H,(40100H)=55H,(40101H)=AAH,执行指令“LEABX,[DI]”后,BX中的内容是。

0100H

6.如果TABLE为数据段3400H单元的符号名,其中存放的内容为0505H,当执行指令“MOVAX,TABLE”后,(AX)=;而执行指令“LEAAX,TABLE”后,AX=。

0505H;3400H

7.若(DS)=1000H,(SI)=2000H,(DI)=1000H,(AX)=2500H,(34000H)=AAH,(34001H)=34H,(34002H)=00H,(34003H)=50H,变量AREA的值为3000H,执行指令“LDSSI,AREA[DI]”后,SI的内容是,DS的内容是。

3400H;5000H

8.已知(AL)=2EH,(BL)=6CH,执行“ADDAL,BL”之后,(AL)=9AH,(BL)=6CH,ZF=0,AF=1,AF=1,OF=1,PF=1,CF=0。

9AH;6CH;0;1;1;1;0

9.CPU对两个无符号8位二进制数进行加法运算后,结果为OEH,且标志位CF=1,OF=1,SF=0,其结果应为十进制数。

270

10.8086CPU执行“SUBAH,AL”后结果为(AH)=85H,OF=1,CF=1。

若AH,AL中为带符号数,则指令执行前寄存器中的数大。

AL

11.若(AX)=753111,(BX)=42DAH,则“CMPAX,BX”指令执行后,(AX)=,(SF,ZF,CF,OF)=。

7531H;0000

12.设(AL)=10100000B,则执行NEGAL后,(AL)=10000