南邮软件设计613.docx

《南邮软件设计613.docx》由会员分享,可在线阅读,更多相关《南邮软件设计613.docx(14页珍藏版)》请在冰豆网上搜索。

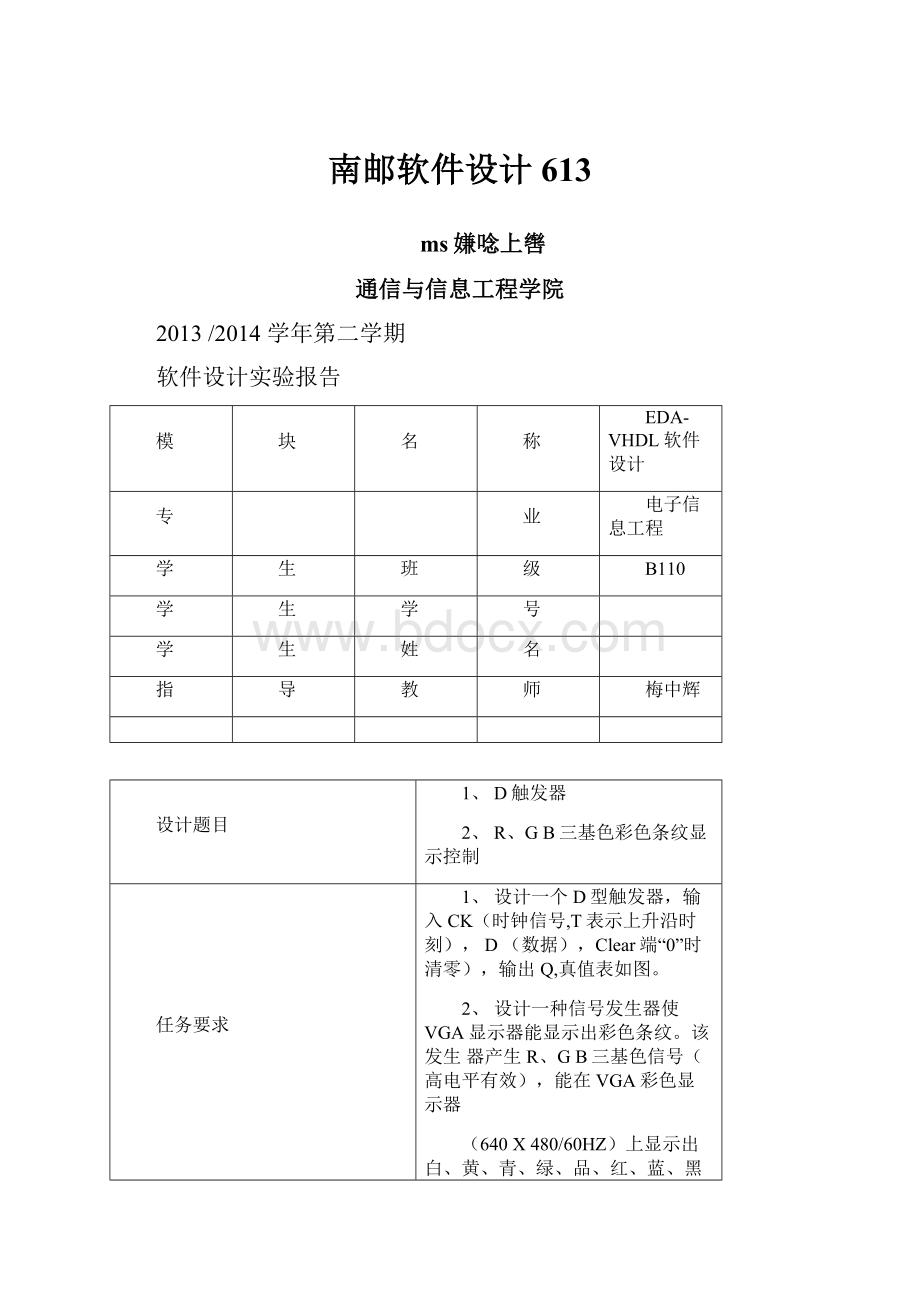

南邮软件设计613

ms嫌唸上辔

通信与信息工程学院

2013/2014学年第二学期

软件设计实验报告

模

块

名

称

EDA-VHDL软件设计

专

业

电子信息工程

学

生

班

级

B110

学

生

学

号

学

生

姓

名

指

导

教

师

梅中辉

设计题目

1、D触发器

2、R、GB三基色彩色条纹显示控制

任务要求

1、设计一个D型触发器,输入CK(时钟信号,T表示上升沿时刻),D(数据),Clear端“0”时清零),输出Q,真值表如图。

2、设计一种信号发生器使VGA显示器能显示出彩色条纹。

该发生器产生R、GB三基色信号(高电平有效),能在VGA彩色显示器

(640X480/60HZ)上显示出白、黄、青、绿、品、红、蓝、黑条纹,各种彩色条纹所对应的R、GB编码如下表所示。

另外需产生行同步HS和场同步VS信号。

当VS=QHS=0时,CRT显示的内容为亮的过程,即正向扫扌田过程,约为26us,当一行扫扌田兀毕,行同步HS=1约为6us;其间CRT扫描产生消隐,电子束回到CRT左边下一行起始位置(x=0,y=1);当扫描完480行后,CRT的场同步VS=1,产生场同步使扫描线回到CRT的第一行第一列(x=0,y=0),约需两行周期。

已知该发生器的输入时钟为12MHz

实验设备

及软件

1:

微型计算机

2:

quartusII开发软件

同组人员

学号及姓

名

参考文献

《VHDL开发精解与实例剖析》詹仙宁云耕编著

《VHDL数字电路及系统设计》江思敏编著

报告内容

实验目的:

1.使学生全面了解如何应用该硬件描述语言进行高速集成电路设计;

2.通过软件使用、设计与仿真环节使学生熟悉EDA-VHD开发环境;

3.通过对基本题、综合题的设计实践,使学生掌握硬件系统设计方法(自底向

上或自顶向下),熟悉VHDL语言三种设计风格,并且培养学生应用VHDL语言解决实际问题的能力。

实验设备:

1:

微型计算机2:

quartusII开发软件

实验课题:

1、D触发器

一、实验内容:

设计一个D型触发器,输入CK(时钟信号,T表示上升沿时刻),D(数据),Clear端(“0”时清零),输出Q真值表如图。

、原理图

CKClearD

Q

X0X

0

f10

0

f11

1

三、功能分析

Clear端为0时,无论D为何值,Q置0。

当Clear为1时,遇到输入时钟信号CK上升沿时,Q=D

算法框图:

四、时序仿真图

ff-srt

E

pPE

3D.pElzL&l.Qm0ell皿giXOns

umticPbiTiO.JlTESDOOlznsa:

Tj

_L_i1!

L!

d:

1__i__

L

414tt*

L

i

1:

111....

厂

~一…’1.1L」

*

[

ir

..i

J

结果分析:

当clear为0时,Q端置0;clear为1时,Q在CK上升沿处跳至与D相等的值。

仿真结果与分析相同,结果正确。

五、调试过程与问题

这个实验是第一次使用quartusII开发软件和VHDL语言,虽然是一个简单的问题,但是也花费了不少时间。

首先顶层实体名称必须与设计顶层文件的文件名一致,与VHDL设计中的顶

层实体名一致。

具体做法是Assignments中Settings里General标签中的

Top-levelentity要与VHDL程序中ENTITY后面的文件名一致。

不然程序无法

编译,这个问题一开始也是困扰了很久的。

成功编译程序之后,一开始不知道如何设置仿真的波形,通过网上搜索和翻阅一些参考书,花了一些时间之后终于找到了波形仿真相关按钮的位置、并掌握

了波形仿真的步骤。

时序仿真成功后,通过分析时序图发现,当clear端为0时,只有遇到CK上升沿Q端才会置0,与题目要求不符。

于是重新调整语句,将clear是否为0作为第一个判断条件。

一开始信号周期选的较小,由于存在延时,不便于观察结果是否正确。

选取较大周期信号后,延时基本可以忽略。

六、VHDL源程序

见附录一

实验课题:

2、R、GB三基色彩色条纹显示控制

一、实验内容:

设计一种信号发生器使VG/显示器能显示出彩色条纹。

该发生器产生R、GB三基色信号(高电平有效),能在VGA彩色显示器(640X480/60HZ)上显示出白、黄、青、绿、品、红、蓝、黑条纹,各种彩色条纹所对应的R、G

B编码如下表所示。

另外需产生行同步HS和场同步VS信号。

当VS=0HS=0时,CRT显示的内容为亮的过程,即正向扫描过程,约为26us,当一行扫描完毕,行同步HS=1,约为6us;其间CRT扫描产生消隐,电子束回到CRT左边下一行起始位置(x=0,y=1);当扫描完480行后,CRT的场同步VS=1,产生场同步使扫描线回到CRT的第一行第一列(x=0,y=0),约需两行周期。

已知该发生器的输入时钟为12MHz

第

£

红

品

r黄

白

R

0

0

€

0

]

1

1

1

G円

0

0

1

0

]

)

0

1

0

1

0

0

)

二、设计思路

需要一个时钟输入信号,根据输入信号产生水平扫描计数从而产生行同步信号HS,再根据水平扫描计数的进位产生竖直扫描计数从而产生场同步信号,完成扫描过程。

之后在根据要求将水平或竖直方向的扫描信号的显示时间分为8

组,显示出8个彩条。

信号扫描时序图:

—图像显示t消隐

时间

垂直扫描

水平扫描

时间长度

时钟周期

等效行数

时间长度

时钟周期数

Ts

16.07ms

385600

482

33.3

lis

800

Tdisp

16ms

384000

480

26.67

[is

640

Tpw

66.7iis

1600

2

6.67

is

160

Y

V>480

N

N

N

N

N

三、算法框图

V=V+1

五、调试过程与问题

在程序成功编译之后开始时序仿真,设定好输入波形之后开始时序仿真发现输出信号全为0,于是将中间信号加入到时序仿真中,发现波形正常,考虑到可能是仿真时长不够,输出信号还未开始变化,将仿真时长设定为1ms之后,成功看到按顺序变化的RGB言号。

之后开始对于题目中给出的时间要求,更改程序中的相关数据。

由于正向扫描过程约为26us,为640个时钟周期,需要水平扫描信号为24MHz,而输入时钟信号只有12MHz,时钟信号倍频相对困难,于是在一个时钟周期内扫描两个水平像素点来保证正向扫描约为26us,约为6us的行消隐信号约为144个时钟周期。

六、VHDL源程序

见附录二实验小结:

这是第一次接触VHDL语言,通过查阅参考书,从零做起,从实际的题目中一点一点了解了VHDL语言的用法。

先理解书上一些实际的例题,然后自己去更改、编写程序,从而完成了实验课题。

只有通过自己动手实验,才能更快的掌握新的知识,才能发现纯理论学习中发现不了的问题。

这次的实验基本都是通过自学完成的,在实验过程中遇到的问题大多都是通过参考书、网络或是和同学讨论解决的,大大提高了自己的学习能力。

实验分为基本题和综合题的形式。

基本题较简单,很好得帮助我了解VHDL语言以及quartusII开发软件的使用。

之后的综合题较为复杂,帮助我进一步学习VHDL语言,以及题目相关的其他知识。

无论是基本题还是综合题在实验过程中都是遇到了各种各样的问题,困难重重,通过自己的努力完成这次实验收获还是不小的。

附录:

一、

libraryieee;

useieee.std_logic_1164.all;

entityHYisport(D,CK,clear:

instd_logic;

Q:

outstd_logic);

end;

architectureaofHYissignalQ_temp:

std_logic;

beginpl:

process(CK)begin

ifclear='0'then

Q_temp<='0';

elsifclear='1'thenifCK'eventandCK='1'then

Q_temp<=D;endif;endif;

Q<=Q_temp;

endprocess;

end;

附录二:

libraryiEEE;

useIEEE.STD_LOGIC_1164.ALL;

entityB11011013is

port(Clk:

inSTD_LOGIC;

Rst:

inSTD_LOGIC;Red:

outSTD_LOGIC;

Green:

outSTD_LOGIC;Blue:

outSTD_LOGIC;

H_Sync:

outSTD_LOGIC;

V_Sync:

outSTD_LOGIC);

endB11011013;

architectureBchavioralofB11011013issignalCnt_H:

integerrange0to800;signalCnt_V:

integerrange0to482;signalClk_H:

std_logic:

='0';signalClk_V:

std_logic:

='0';signalRGB:

std_logic_vector(0to2);

begin

Red<=RGB(0);

GreeN<=RGB

(1);

Blue<=RGB

(2);

---12MHZ作为水平扫描信号的时钟p1:

process(Clk)

begin

Clk_H<=Clk;

endprocess;

--水平扫描计数,并产生竖直扫描计数的时钟p2:

process(Clk_H,Rst)

begin

if(Rst='1')then

Cnt_H<=0;

Clk_V<='1';

elsif(Clk_H'eventandClk_H='1')thenif(Cnt_H>=800)then

Cnt_H<=0;

else

Cnt_H<=Cnt_H+2;

if(Cnt_H>400)then

Clk_V<='0';else

Clk_V<='1';endif;

endif;

endprocess;

---竖直扫描计数p3:

process(Clk_V,Rst)begin

if(Rst='1')then

Cnt_V<=0;elsif(Clk_V'eventandClk_V='1')thenif(Cnt_V=482)then

Cnt_V<=1;

else

Cnt_V<=Cnt_V+1;

endif;

endif;

endprocess;

--产生水平扫描信号和竖直扫描信号p4:

process(Clk,Rst)begin

if(Rst='1')then

H_Sync<='0';

V_Sync<='0';

elsif(Clk'eventandClk='1')thenif(Cnt_H>=641)then

H_Sync<='1';else

H_Sync<='0';endif;

if(Cnt_V>480)then

V_Sync<='1';

else

V_Sync<='0';

endif;

endif;

endprocess;

--输出颜色控制

p5:

process(Clk,Rst,Cnt_V)

begin

if(Rst='1')then

RGB<="000";

elsif(Cnt_V>480)then

RGB<="000";

elsif(Clk'eventandClk='1')then

caseCnt_His

when1to80=>RGB<="000";when81to160=>RGB<="001";when161to240=>RGB<="010";when241to320=>RGB<="011";when321to400=>RGB<="100";when401to480=>RGB<="101";when481to560=>RGB<="110";when561to640=>RGB<="111";whenothers=>RGB<="XXX";endcase;

endif;

endprocess;

endBchavioral;

设计成绩评定

评分内容

具体要求

总分

评分

上机时间

上机时间是否达到要求的学时,按照实际情况给与一定的成绩。

10分

报告审阅结果

报告结构严谨,文字通顺,用语符合技术规范,图表清楚,书写格式规范,不与别人雷同。

30分

验收结果

原理

原理清楚,能较好地理解课题任务并提出实施方案。

20分

完成情况

独立完成规定设计任务,论证、分析、设计、计算、结构、建模、实验正确合理,有一定的创新。

30分

操作

能熟练操作相关工具软件,并利用工具软件完成设计任务。

10分

总成绩(五分制)

100分

指导教师评阅意见