多功能数字钟的设计与实现.docx

《多功能数字钟的设计与实现.docx》由会员分享,可在线阅读,更多相关《多功能数字钟的设计与实现.docx(18页珍藏版)》请在冰豆网上搜索。

多功能数字钟的设计与实现

数字逻辑

课程设计报告

——多功能数字钟的设计与实现

一、设计目的

1、学会应用数字系统设计方法进行电路设计;

2、学习使用QuartusII9.0,进一步提高软件的开发应用能力,增强自己的动手实践能力。

3、培养学生书写综合实验报告的能力。

二、设计任务及要求

实现多功能数字钟的设计,主要有以下功能:

1、记时、记分、记秒

2、校时、校分、秒清0

3、整点报时

4、时间正常显示

5、闹时功能(选做)

三、设计思路

3.1计时模块

3.1.1设计原理

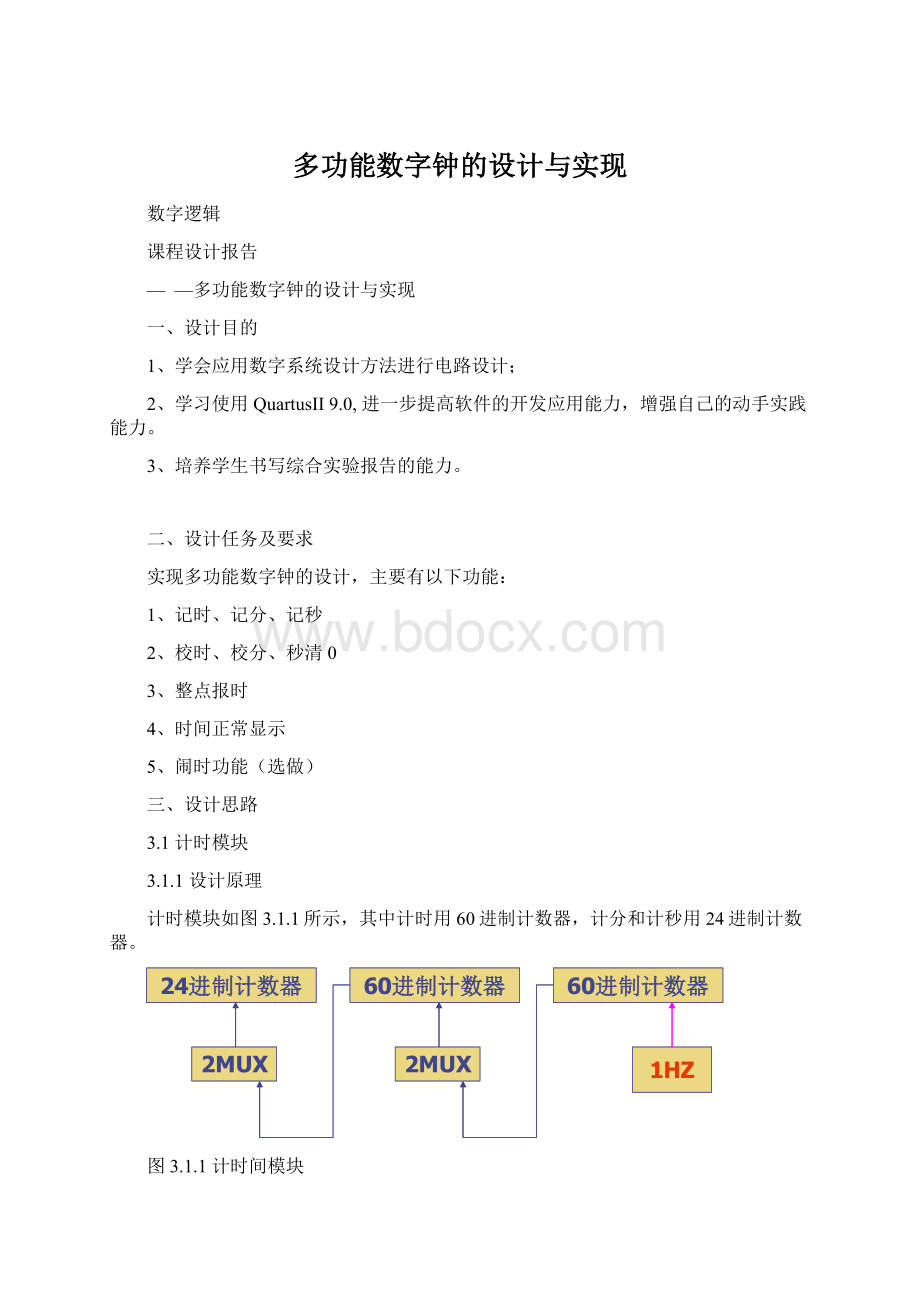

计时模块如图3.1.1所示,其中计时用60进制计数器,计分和计秒用24进制计数器。

图3.1.1计时间模块

计时间过程:

计秒:

1HZ计数脉冲,0~59循环计数,计数至59时产生进位信号;

计分:

以秒计数器进位信号作为分计数脉冲,0~59循环计数,59时产生进位;

计时:

以分计数器进位信号作为时计数脉冲,0~23循环计数,23时清0。

计数器的设计:

3.1.2设计程序

编程分别设计24、60进制计数器,计数状态以BCD码形式输出。

24进制计数器源程序:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityFEN24is

port(en,clk:

instd_logic;----高电平有效的使能信号/输入时钟

co:

outstd_logic;

h1,h0:

outstd_logic_vector(3downto0));----时高位/低位

endFEN24;

architecturebehaveofFEN24is

begin

process(clk)

variablecnt1,cnt0:

std_logic_vector(3downto0);----记数

begin

if(en='0')then---“使能”为0

cnt0:

="0010";

cnt1:

="0001";

elsifclk'eventandclk='1'then---上升沿触发

ifcnt1="0010"andcnt0="0011"then

cnt0:

="0000";----高位/低位同时为0时

cnt1:

="0000";

co<='1';

else

co<='0';

ifcnt0="1001"then

cnt0:

="0000";

cnt1:

=cnt1+1;

else

cnt0:

=cnt0+1;-----高位记数累加

endif;

endif;

endif;

h1<=cnt1;

h0<=cnt0;

endprocess;

endbehave;

60进制计数器源程序:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityFEN60is

port(en,clk:

instd_logic;---高电平有效的使能信号/输入时钟

co:

outstd_logic;---输出/进位信号

s1,s0:

outstd_logic_vector(3downto0));

endFEN60;

architecturebehaveofFEN60is

begin

process(clk,en)

variablecnt1,cnt0:

std_logic_vector(3downto0);---计数

begin

ifen='0'then---“使能”为0

cnt1:

="0000";

cnt0:

="0000";

elsifclk'eventandclk='1'then

ifcnt0="1001"then

cnt0:

="0000";

ifcnt1="0101"then---当计数为58(实际是经过59个计时脉冲)

cnt1:

="0000";

co<='1';---进位

else

cnt1:

=cnt1+1;

co<='0';

endif;

else

cnt0:

=cnt0+1;

endif;

endif;

s1<=cnt1;

s0<=cnt0;

endprocess;

endbehave;

3.1.3设计仿真及生成器件

24进制计数器仿真波形截图如图3.1.2所示,其中计到23时,即高位h1为2,低位h0为3时产生进位。

图3.1.224进制计数器仿真波形

60进制计数器仿真波形截图如图3.1.3所示,其中计到59时,即高位s1为5,低位s0为9时产生进位。

图3.1.360进制计数器仿真波形

24进制计数器和60进制计数器生成器件分别如图3.1.4、图3.1.5所示,其中en为时能信号,接高电平,clk接1kHz的时钟信号,co为进位,h1为时高位,h0为时低位,s1为秒或分高位,s0为秒或分低位。

图3.1.424进制计数器图3.1.560进制计数器

3.2校时模块

3.2.1设计原理

计、校时对模块如图3.2.1所示。

图3.2.1计、校时对模块

校时模块设计要求实现校时、校分以及清零的功能。

按下校时键,时位迅速递增以调至所需要的小时位,满23清0;

按下校分键,分位迅速递增以调至所需要的分位,满59清0;

按下清零键,秒清零;

选择实验板上的三个脉冲按键进行锁定。

对此模块的设计,需要注意两个问题:

1.如何实现校对时间时,计数器快速递增?

按键校对时间时,将一个频率较高的计数脉冲信号作用于计数器,屏蔽正常计时的计数脉冲信号。

2.“抖动”的消除

电路抖动:

一次按键的弹跳现象,电路产生多个计数脉冲,导致一次按键,多次计数的误动作。

抖动产生的原因:

物理原因。

消除抖动简易方法:

D触发器,同步按键脉冲。

原理:

一个CP内,屏蔽所有抖动脉冲。

两种脉冲信号用两路选择器进行选择,选择条件为是否按键。

按键输出经过了消抖处理。

3.2.2设计程序

二路选择器源程序:

libraryieee;

useieee.std_logic_1164.all;

entityMUX2is

port(A,B,S:

inbit;

Y:

outbit);

endMUX2;

architectureoneofMUX2is

begin

process(A,B,S)

begin

ifS='0'then

Y<=A;

else

Y<=B;

endif;

endprocess;

endone;

3.2.3设计仿真及生成器件

二路选择器生成器件如图3.2.2所示。

图3.2.2二路选择器

3.3整点报时模块

3.3.1设计原理

报时模块原理图如图3.3.1所示,数字钟从59分50秒开始,每2秒一次低音报时,当达到整点时,进行一次高音报时,其中低音报时频率为500Hz,高音报时频率为1kHz。

图3.3.1报时模块

进行报时的条件是计数器计数至所要求的时间点,因而需要实现一个比较模块,如图3.3.2所示,将分计数器和秒计数器的输出连至比较模块输入端完成比较工程。

图3.3.2比较模块

3.3.2设计程序

整点报时源程序:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityZDBSis

port(mh,ml,sh,sl:

instd_logic_vector(3downto0);--输入分秒高低位信号

sig500,sig1k:

outstd_logic);---频声控制

endZDBS;

architecturebehaveofZDBSis

begin

process(ml)

begin

sig500<='0';

sig1k<='0';

ifmh="0101"andml="1001"then

ifsh="0101"and(sl="0000"orsl="0010"orsl="0100"orsl="0110"orsl="1000")

thensig500<='1';----低频输出为1

elsesig500<='0';----否则输出为0

endif;

endif;

ifmh="0000"andml="0000"andsh="0000"andsl="0000"-----整点报时

thensig1k<='1';-----高频输出为1

elsesig1k<='0';

endif;

endprocess;

endbehave;

3.3.3设计仿真及生成器件

整点报时生成器件如图3.3.3所示,器件输入为分和秒,分别接分计数器和秒计数器的高低位,输出为高频声控sig500和sig1k。

图3.3.3整点报时

3.4分频模块

3.4.1设计原理

分频模块如图3.4.1所示,系统需要用到多种不同频率的脉冲信号,上至高音报时信号,下至1Hz的计秒脉冲,所有这些脉冲信号均可以通过一个基准频率分频器生成,基准频率分频器就是一个进制很大的计数器,利用计数器的分频功能,从不同的输出位得到所需要的脉冲信号。

因此可以设计一个进制较大的计数器,分频产生各种频率的脉冲信号。

图3.4.1分频模块

3.4.2设计程序

分频器源程序:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

entityFPQis

port(clk:

instd_logic;

hz512:

outstd_logic;

hz64:

outstd_logic;

hz4:

outstd_logic;

hz1:

outstd_logic

);

endFPQ;

architecturebehaveofFPQis

signalq:

std_logic_vector(9downto0);

begin

process(clk)

begin

ifclk'eventandclk='1'then

q<=q+1;

endif;

endprocess;

hz512<=q(0);

hz64<=q(3);

hz4<=q(7);

hz1<=q(9);

endbehave;

3.4.3设计仿真及生成器件

分频器仿真波形如图3.4.2所示,clk为时钟输入信号,设为1024Hz,由于1Hz和4Hz频率太小,因此在仿真波形图上为一条直线,从图上可以清楚看到512Hz和64Hz的频率

图3.4.2分频器仿真波形

分频器生成器件如图3.4.3所示,其中左端为时钟输入信号clk,右端为频率端,主要是整点报时用的1000Hz与500Hz的脉冲信号,及闹钟报时的4Hz,秒输入信号1Hz。

图3.4.3分频器

3.5动态扫描显示模块

3.5.1设计原理

由于资源不足无法完整显示6位时间,因此采用动态扫描的方式实现时间显示。

在动态扫描方式下,所有的