数字电子技术基础课程设计.docx

《数字电子技术基础课程设计.docx》由会员分享,可在线阅读,更多相关《数字电子技术基础课程设计.docx(12页珍藏版)》请在冰豆网上搜索。

数字电子技术基础课程设计

苏州科技大学电子与信息工程学院

数字电子技术基础课程设计报告

专业班级:

电子1412

学号:

14200106214

姓名:

孙玮

指导教师:

潘欣裕

2016年07月03日

一、基础部分(共55分,利用下列芯片,构建出具有验证其逻辑或时序功能的系统,实现仿真电路,并附详细参数计算及说明)

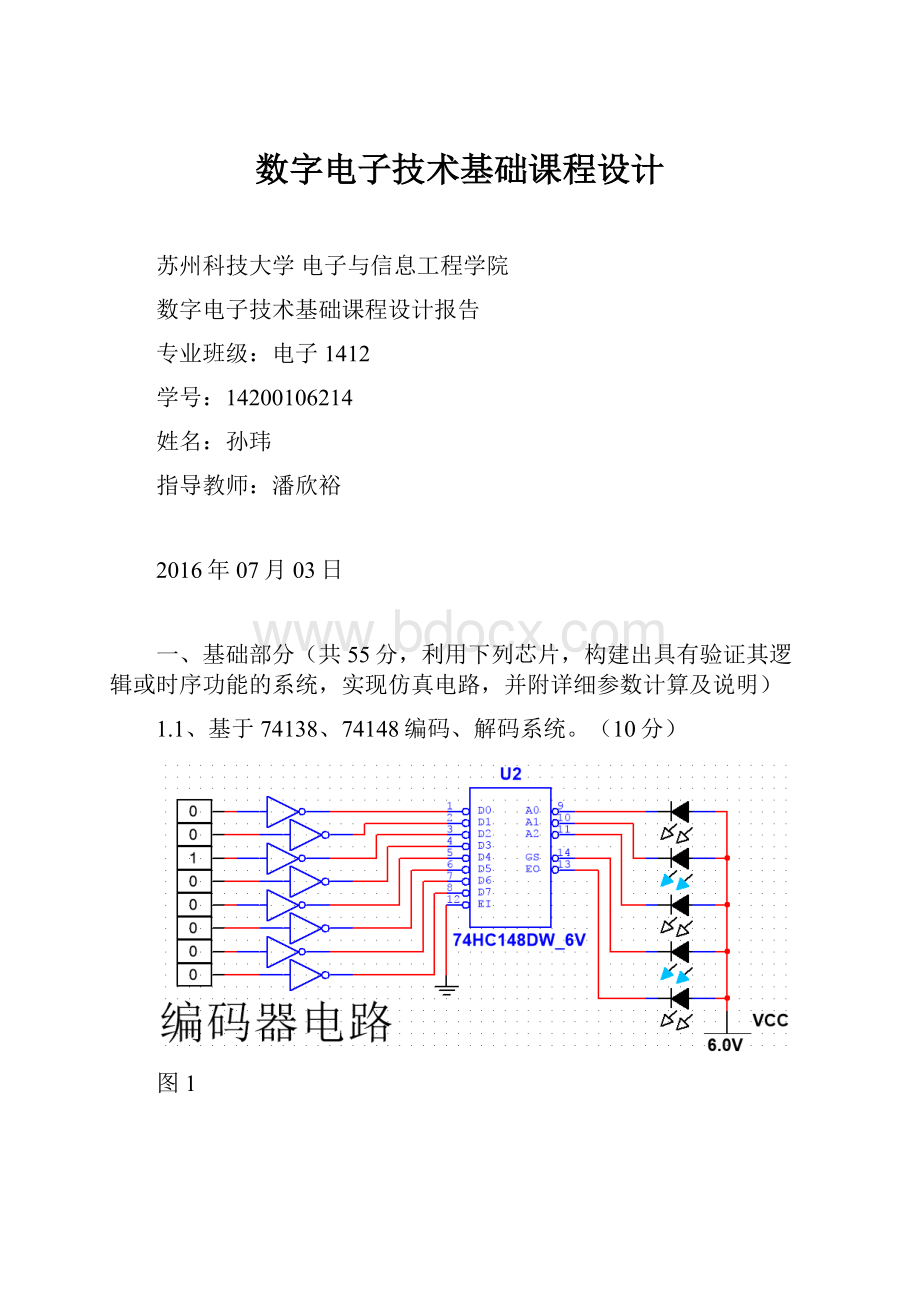

1.1、基于74138、74148编码、解码系统。

(10分)

图1

图2

图1为编码器电路,图2为解码器电路。

他们的逻辑转换表如下所示。

图3

图4

74HC148在S’=0电路正常的工作状态下,允许I0’~I7’当中同时有几个输入端为低电平,即有编码输入信号。

I7’的优先级最高,I0’的优先级最低。

当有多个输入时,编码器只会对优先级最高的进行编码,优先级较低的不会进行编码。

当出现Y2’、Y1’、Y0’都为0时,可以用Ys’和Yex’的不同状态来区分。

只有当S’为0时。

编码器才会工作,不为0时,编码器不工作,输出均为1。

有输入时Ys’为1,Yex’为0,当使用两片接成16-4编码器时,第一片的Ys’连到第二片的S’。

74HC138只有当S1=1,且S2’=S3’=0时才会工作。

数据由S1段输入,由A2A1A0来确定输出口,所以S1成为数据输入端,A2A1A0为地址输入端,以反码输出。

将73HC148的输出作为74HC138的地址输入可以实现完整的编码解码电路。

1.2、基于74161或74160的计数电路。

(10分)

图5

图5所示为基于74HC161的计数电路。

该电路是由两片74HC161级联实现的256进制计数器。

其输入端逻辑电平如下图所示。

图6

74HC161为十六进制计数器,其从0000到1111计数。

RD’为0时,74HC161不论其他引脚的接法直接异步置零,当CLK为上升沿时,且RD’为1,LD’=0是芯片工作在预置数状态,同步置数;CLK上升沿,RD’=LD’=1,芯片处于计数状态,每来一次上升沿,芯片会有一次加一。

图中芯片处于计数状态,~LOAD和~CLR接1,ENP与ENT接1,芯片开始正常计数。

当数据加到1111时,在RCO处产生进位。

此外,通过多个级联可以实现多进制的计数器。

1.3、基于74151数据选择器的功能电路。

(10分)

图7所示为基于74151数据选择器的功能电路。

图8所示为74151数据选择器的逻辑转换表。

74151是八选一的数据选择器,使用ABC输入地址代码,可以选择八个数据中的一个,并在Y输出,~W输出Y的取反值。

例如如图中所示,当输入为D0=D1=D2=D4=D5=1,D3=D6=D7=0,A=0,B=C=1,数据选择器选择了D3,所以表现在二极管上是不导通。

图7

图8

1.4、基于JK触发器的时序电路。

(10分)

图9

图9所示为由四个JK触发器构成的十六进制计数电路。

其输出波形如下图所示。

图10

由图可见,各触发器驱动方程分别为T0=1T1=Q0T2=Q0Q1T3=Q0Q1Q2。

将上式代入T触发器(由JK触发器构成)的特性方程可得Q0*=Q0’Q1*=Q0Q1’+Q0’Q1Q2*=Q0Q1Q2’Q3*=Q0Q1Q2Q3’+(Q0Q1Q2)Q3’+(Q0Q1Q2)’Q3。

电路输出方程为C=Q0Q1Q2Q3。

其电路状态转换表如下图所示。

图11

1.5、555的信号产生电路、施密特触发电路各一个。

(15分)

图12

如图12所示为基于施密特触发器的整波电路。

它的功能是将正弦波转化为方波信号。

仿真的示波器截图如下图所示。

图13

如图14所示为基于555定时器的多谐振荡电路。

其充电周期T1=Ln2*(R1+R2)C2,放电周期T2=Ln2*R1*C2,T=T1+T2。

因此,图中电路所产生信号频率为f=1/T=476Hz。

测量波形如下图所示。

图14

二、提高部分(40分)

2.1、制作一个时钟电路,具有时、分、秒显示、重置、预置等功能,要求写出必要的设计过程,并画出对应的逻辑图,实现仿真。

(15分)

计数部分截图如图15所示;置数如图16所示;复位如图17所示。

1、秒钟设计:

秒钟是六十进制,用两片74HC160实现,第一片作为秒,十进制,第二片作为十秒,设置成六进制,并将第一片的进位信号连接到第二片的ENT与ENP;秒位满十进制进位溢出给十秒位计数信号,所以秒位计十次,十秒位计一次,从而实现六十进制。

74HC160输出端接数码管读出计数。

2、分钟设计:

原理和秒钟一样,也是采用六十进制。

3、时钟设计:

时钟与之前两个不一样,设置为二十四进制,整体进行置数,当时钟达到24时直接置零,从头开始计数。

4、秒钟与分钟之间的连接:

当秒钟计到59时,会对分钟产生进位。

所以用与门将秒位的二进制九和十秒位上的二进制五通过与门连接到分钟的ENT/ENP使得分钟正常计数开始,从而实现秒钟计数六十次,分钟计数一次。

5、分钟与时钟的连接:

原理与秒钟和分钟的连接类似,将秒钟和分钟上的二进制位的59通过一个与门连接到时钟的ENP/ENT,使得时钟得以正常计数,从而实现分钟计数60,时钟计数一次。

6、整体时钟的置零:

将各个位的CLR位引出来和六进制的复位连线经与门之后连接到单刀双掷开关上,CLR是低电平有效,所以当单刀双掷开关接地时,整个时钟电路时置零。

7、整体时钟电路置数:

将每一片的74HC160的输入端连接到一个开关,通过控制开关的连接控制输入1或者0。

将所有芯片的Load端引至一个单刀双掷开关,低电平有效,从而实现同时置数。

以上就是设计时钟电路的简要思路。

图15

图16

图17

2.2、用两片四位全加器74283和必要的逻辑门设计一个数制转换电路,实现将输入的两位十进制数转换成二进制数,十进制数的输入采用8421BCD码来表示,要求写出必要的设计过程,并画出对应的逻辑图,实现仿真。

(15分)

图18

如图18所示为仿真的截图。

其左端输入BCD码10001001,右端LED显示的是01011001,均分别为十进制数89。

设计思路:

假设有一个两位十进制数X,其对应的八位BCD码为ABCDEFGH,即ABCD*(10000)BCD+EFGH=(X)10。

上式=ABCD*(1000)B+ABCD*(10)B+EFGH,所以二进制为ABCD000+ABCD0+EFGH=ABCD000+ABCD0+0EFG0+H。

由上式可知,H可以直接输出,其为二进制的最低位。

然后我们可以用第一片74283将ABCD与0EFG求和,将得到的结果设为KLMN,进位为O。

于是二进制数可以表示为KLMN0+O00000+ABCD000+H。

由此可见,M与N分别为二进制的倒数第三与第二位。

而其前四位可由74283将ABCD与OKL相加得到,最终输出七位二进制数。

2.3、自主设计一个具有特定功能,且包含4个以上不同类型芯片的系统,要求写出必要的设计过程,并画出对应的逻辑图,实现仿真。

(10分)

本部分我自主设计了一个四位二进制乘法器,其仿真截图如下所示。

图中两个输入端分别输入了1011与1101,其乘法运算结果为10001111,与仿真结果相符。

图19

设计思路:

假设一个四位二进制数为ABCD,另外一个为EFGH,则其相乘的运算过程为:

ABCD*EFGH=(A*E)(B*E)(C*E)(D*E)000+(A*F)(B*F)(C*F)(D*F)00+(A*G)(B*G)(C*G)(D*G)0+(A*H)(B*H)(C*H)(D*H)。

因此我们可以将EFGH每一位提出来与ABCD每一位相乘,然后将其加起来求和。

这里提出EFGH中每一位的过程可以通过移位寄存器实现。

此外,因为74HC283只能实现4位二进制的全加过程,因此每次相加完都需要将和的最低位取出进行保存。

此处保存使用移位寄存器(因为前面我们使用了移位寄存器,且其也移动四位,所以可以使用前面使用的移位寄存器来实现数据的保存)。

另外,因为74HC283不是时序逻辑电路,所以需要将它输出的用于下一步求和的数据(此处的数据为求和结果的高三位与进位)存于寄存器中。

等待下个上升沿到来后,将数据传输到74HC283的B输入口(B4输入进位,B3~B1输入前一次求和结果的高三位)。

由此,经过四个周期之后,乘法运算就全部计算完毕。

但由于在运行完四个周期后还会继续运行,导致数据无法保存,所以需要加一个计数器(这里采用74HC160)。

当计数计到0100的时候,通过逻辑电路将时钟信号与计数器停止。

下次运行时只需摁下复位开关将寄存器与计数器复位即可进行下次运算。