Verilog语言实现设计交通灯控制器.docx

《Verilog语言实现设计交通灯控制器.docx》由会员分享,可在线阅读,更多相关《Verilog语言实现设计交通灯控制器.docx(3页珍藏版)》请在冰豆网上搜索。

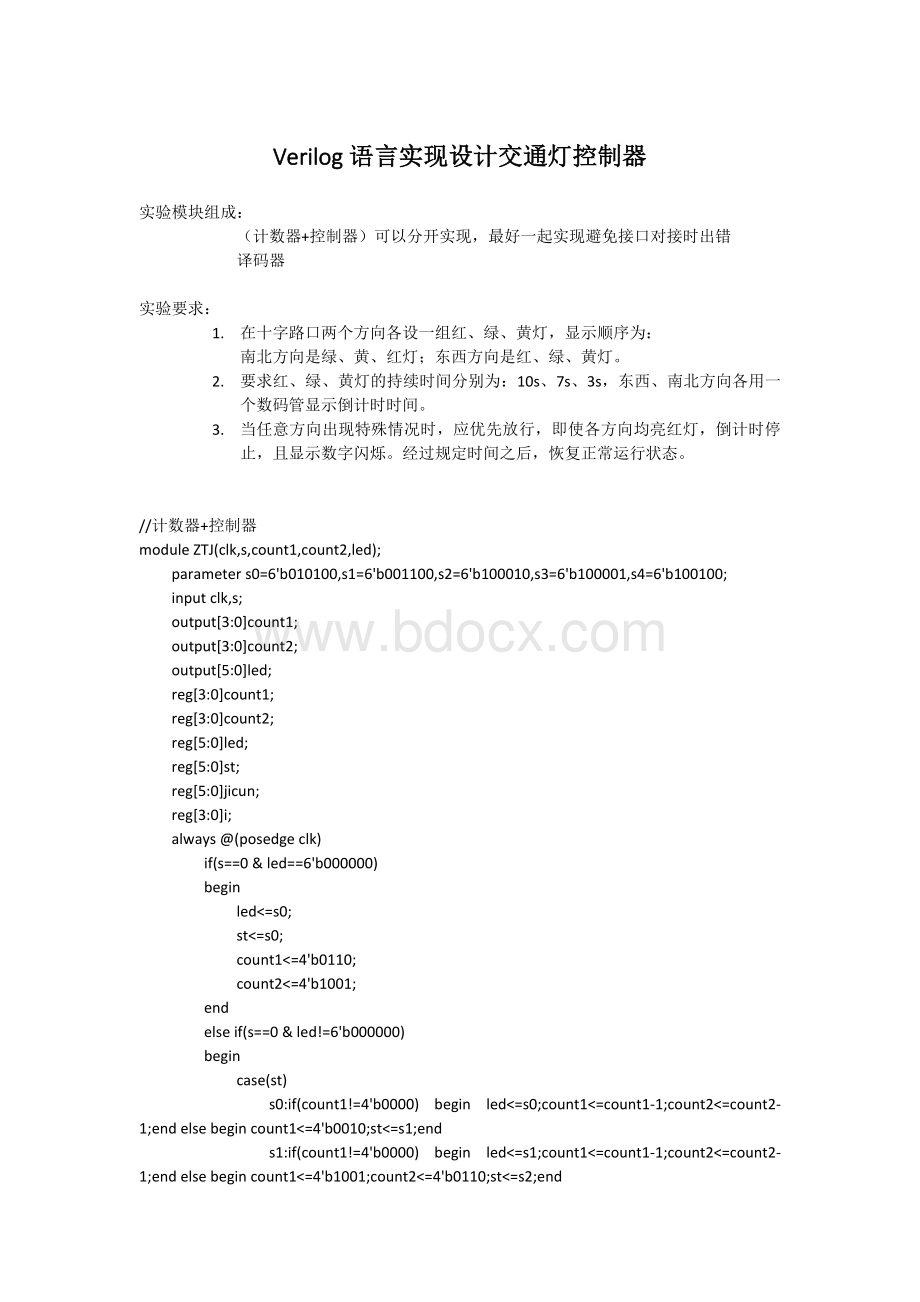

Verilog语言实现设计交通灯控制器

实验模块组成:

(计数器+控制器)可以分开实现,最好一起实现避免接口对接时出错

译码器

实验要求:

1.在十字路口两个方向各设一组红、绿、黄灯,显示顺序为:

南北方向是绿、黄、红灯;东西方向是红、绿、黄灯。

2.要求红、绿、黄灯的持续时间分别为:

10s、7s、3s,东西、南北方向各用一个数码管显示倒计时时间。

3.当任意方向出现特殊情况时,应优先放行,即使各方向均亮红灯,倒计时停止,且显示数字闪烁。

经过规定时间之后,恢复正常运行状态。

//计数器+控制器

moduleZTJ(clk,s,count1,count2,led);

parameters0=6'b010100,s1=6'b001100,s2=6'b100010,s3=6'b100001,s4=6'b100100;

inputclk,s;

output[3:

0]count1;

output[3:

0]count2;

output[5:

0]led;

reg[3:

0]count1;

reg[3:

0]count2;

reg[5:

0]led;

reg[5:

0]st;

reg[5:

0]jicun;

reg[3:

0]i;

always@(posedgeclk)

if(s==0&led==6'b000000)

begin

led<=s0;

st<=s0;

count1<=4'b0110;

count2<=4'b1001;

end

elseif(s==0&led!

=6'b000000)

begin

case(st)

s0:

if(count1!

=4'b0000)beginled<=s0;count1<=count1-1;count2<=count2-1;endelsebegincount1<=4'b0010;st<=s1;end

s1:

if(count1!

=4'b0000)beginled<=s1;count1<=count1-1;count2<=count2-1;endelsebegincount1<=4'b1001;count2<=4'b0110;st<=s2;end

s2:

if(count2!

=4'b0000)beginled<=s2;count1<=count1-1;count2<=count2-1;endelsebegincount2<=4'b0010;st<=s3;end

s3:

if(count2!

=4'b0000)beginled<=s3;count1<=count1-1;count2<=count2-1;endelsebegincount1<=4'b0110;count2<=4'b1001;st<=s0;end

default:

led<=s4;

endcase

end

else

begin

jicun<=led;

led<=s4;

count1<=count1;

count2<=count2;

i<=i+1;

if(i==4'b1001)

led<=jicun;

end

endmodule

//译码器

moduleDECL7S(A,LED7S);

input[3:

0]A;

output[6:

0]LED7S;

reg[6:

0]LED7S;

always@(A)

begin

case(A)

4'b0000:

LED7S<=7'b0111111;

4'b0001:

LED7S<=7'b0000110;

4'b0010:

LED7S<=7'b1011011;

4'b0011:

LED7S<=7'b1001111;

4'b0100:

LED7S<=7'b1100110;

4'b0101:

LED7S<=7'b1101101;

4'b0110:

LED7S<=7'b1111101;

4'b0111:

LED7S<=7'b0000111;

4'b1000:

LED7S<=7'b1111111;

4'b1001:

LED7S<=7'b1101111;

4'b1010:

LED7S<=7'b1110111;

4'b1011:

LED7S<=7'b1111100;

4'b1100:

LED7S<=7'b0111001;

4'b1101:

LED7S<=7'b1011110;

4'b1110:

LED7S<=7'b1111001;

4'b1111:

LED7S<=7'b1110001;

default:

LED7S<=7'b0111111;

endcase

end

endmodule