基于MSI芯片74160设计模为100的计数器.docx

《基于MSI芯片74160设计模为100的计数器.docx》由会员分享,可在线阅读,更多相关《基于MSI芯片74160设计模为100的计数器.docx(16页珍藏版)》请在冰豆网上搜索。

基于MSI芯片74160设计模为100的计数器

基于MSI芯片74160设计模为100的计数器

1、实验目的:

基于MSI芯片74160,利用QuartusII软件设计并实现一个计数器的逻辑功能,通过电路的仿真和硬件验证,进一步了解计数器的特性和功能。

2、实验原理:

利用集成计数器MSI芯片的清零端和置数端实现归零,可以按自然态序进行计数的N进制计数器的方法。

集成计数器中,清零、置数均采用异步方式的有74LS163;均采用异步方式的有74LS193、74LS197、74LS192;清零端采用异步方式、置数端采用同步方式的有74LS161、74LS160。

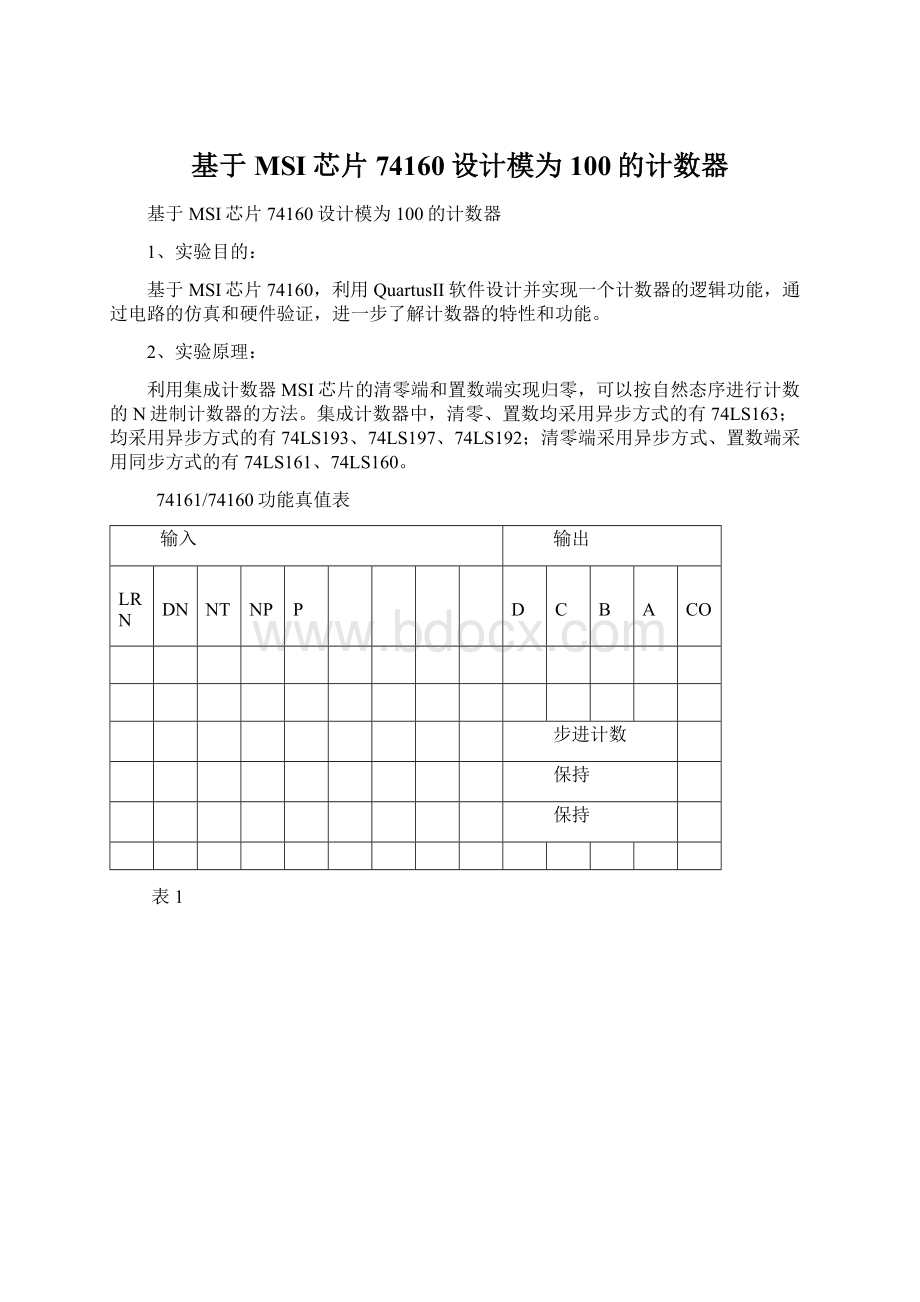

74161/74160功能真值表

输入

输出

CLRN

LDN

ENT

ENP

CP

D

C

B

A

QD

QC

QB

QA

RCO

0

X

X

X

X

X

X

X

X

0

0

0

0

0

1

0

X

X

↑

D

C

B

A

D

C

B

A

1

1

1

1

↑

X

X

X

X

步进计数

1

1

0

X

X

X

X

X

X

保持

1

1

X

0

X

X

X

X

X

保持

0

表1

图1

3、实验环境:

PC机(Windowsxp,QuartusII)

4、实验内容:

按照第五章相关内容,完成计数器的实际,包括原理图输入、编译、综合、适配、仿真,并将此计数器电路设计成一个硬件符号入库。

最后利用两个MSI芯片74160完成一个模为60的计数器的设计,包括原理图的输入、编译、综合、适配、仿真。

5、实验步骤:

Step1.启动QuartusII“开始”菜单“所有程序”中的“Altera”程序框中选择“QuartusII”如图1所示:

Step2.建立工作库目录文件夹以便设计工程项目的存储

EDA工具中的任何一项设计都是一项工程(PROJECT),应首先为此工程建立一个放置与此工程相关的文件的文件夹,此文件夹将被EDA软件默认为工作库(WORKLIBRARY).一般不同的设计项目最好放在相应的文件夹中,注意,一个设计项目可以包含多个设计文件夹。

本项目中的文件夹取名为counter_100,路径为:

E:

/数字逻辑/作业//。

注意:

文件夹名不能用中文,且不可带空格。

Step3.输入设计

(1)打开QuartusII,选择File|New命令。

在New窗口中(如图2所示)的DeviceDesignFile中选择硬件设计文件类型为BlockDiagram/SchematicFile,然后在框图设计文件编辑窗中输入源程序图1的文件。

图2

(2)放置元件

在原理图空白处双击鼠标,跳出Symbol选择窗口(或单击右键选择Inster→Symbol…),出现元件对话框图2

图3

为了设计一位全加器,可参考图1,分别调入元件input、output、与门AND4、MSI芯片74160,并连接好。

然后分别在input和output的PINNAME上双击使其变黑,再用键盘分别输入各引脚名:

CLRN,CLK(时钟),CO(输出),Q[7..0](两个74160共8个输出)。

以及Q[0]到Q[7]输出。

(3)文件存盘

从菜单File中选择Saveas命令,选择刚才为自己工程建立的目录E:

/数字逻辑/作业//,将设计好的图文件取名为:

counter_100(注意后缀是.bdf),并存盘在E:

/数字逻辑/作业//目录内,如图4所示。

图4

Step4.新建工程

(1)单击File/NewProjectWizard,弹出“工程设置”对话框,如图5

图5

第1行的E:

/数字逻辑/作业//表示工程所在的工作库文件夹,第2行表示该工程的工程名,此工程名可以取任何其他的名,也可以用顶层文件实体名作为工程名;第3行是当前工程顶层文件的实体名(此处输入的顶层文件实体名与之后的设计文件实体名相同,默认的顶层文件名与工程名相同),此处即为counter_100。

(2)加入设计文件

单击Next按钮,在弹出的对话框中单击File栏中的“…”,将于工程相关的所有文件加入工程中,单击Add按钮进入此工程,即可得如图6所示的情况。

图6添加设计文件

(3)选择目标芯片(用户必须选择与开发板相应的FPGA器件型号):

这时弹出选择目标芯片的窗口,首先在Family栏选择目标芯片系列,在此选择Cylone系列,如图7所示。

再次单击Next按钮,选择此系列的具体芯片EP1C6Q240C8,这里EP1C6表示Cylone系列及此器件的规模,Q表示PQFP封装,C8表示速度级别。

图7选择目标芯片

(4)选择仿EDA工具:

设计中可能用到的EDA工具有时序分析工具、仿真工具和综合工具。

单击图7中Next按钮,可从弹出的窗口中选择EDA工具类型,如果都选None,表示选QuartusII中自带的EDA工具。

(5)单击Next按钮后进入下一步。

弹出“工程设置统计”窗口,如图8所示。

图8工程设计统计

(6)结束设置。

最后单击Finish按钮,即表示已设定好此工程,并出现counter_100的工程管理窗口(亦称CompilationHierarchies窗口),该窗口主要显示该项目的层次结构和各层次的实体名,如图9所示。

完成设置后可以看到窗口左上角显示所设工程路径的变化。

QuartusII将工程信息文件存储在工程配置文件(.qsf)中。

它包括设计文件、波形文件、SignalTapII文件、内存初始化文件,以及构成工程的编译器、仿真器的软件构件设置等有关QuartusII工程的所有信息。

图9

Step5.编译综合

QuartusII默认把所有编译结果放在工程根目录中,为了让QuartusII像VisualStudio等IDE一样把编译结果放在一个单独的目录中,需要指定编译结果的输出路径。

单击菜单项Assignment→settings,选中CompilationprocessSetting选项卡,勾选右边的SaveProjectoutputfilesinspecifieddirectory,输入路径(releaseordebug),如下图:

QuarterII编译器是由一系列处理模块构成,这些模块负责对设计项目检错,逻辑综合、结构综合、输出结果的编辑配置,以及时序分析。

单击菜单选项Processing→Start→StartAnalysis&Synthesis执行分析与综合项目检错(或Ctrl+K),如果仅仅需要检测语法,那么执行Analysis&Elaboration(分析与解析),但这一步生成的数据并不对应FPGA器件的物理结构,生成的网表中节点的名称也不与FPGA器件的Cell名称对应。

更多情况下直接执行StartAnalysis&Synthesis。

执行分析与综合后,生成的数据库对应FPGA器件的物理结构,映射后的数据库包含FPGA底层Cell的位置信息和Cell的时序信息。

上面所有工作做好后,执行QuartusII主窗口的Processing菜单的StarCompilation选项,启动全程编译。

编译好后的工程管理窗口如图10所示。

图10

编译过程中应注意工程管理窗下方的Processing栏中的编译信息。

如果编译有错,启动编译后下方Processing栏会显示出来,可双击错误提示,即弹出对应用深色标记的相关错误位置,再次编译直至排除所有错误。

在图10中单击Report可得到如图11所示的界面,此界面左上角是工程管理窗口,单击其中各项可了解编译和分析结果。

如单击FlowSummary,将在右栏显示此工程的硬件耗用报告:

TimingAnalyzer项,则能看到当前工程所有相关时序特性的报告。

图11

Step6.仿真测试

该工程编译通过后,必须对其功能和时序性能进行仿真检测,以验证设计结果是否满足设计要求。

整个时序仿真测试流程一般有建立波形文件、输入信号节点、设置波形参数、编辑输入信号、波形文件存盘、运行仿真器和分析仿真波形等步骤。

现给出以.vwf文件方式的仿真测试流程的具体步骤如下:

(1)建立仿真波形文件

选择QuartusII主窗口主窗口的File菜单的New选项,在弹出的文件类型编辑对话框中,选择Verification/DebuggingFiles中的VectorWeaveformFiles项,单击OK按钮,打开波形文件编辑窗口。

单击File→SaveAs,即出现如图12所示:

图12

(2)设置仿真参数

选择Assigment中的settings对话框,可以进行如仿真激励文件、毛刺检测、功耗估计、输出等设置,一般情况下选默认值。

如图13所示:

图13

本题中整个仿真时间区域蛇为10µs、时间轴周期为100ns,其设置步骤是在Edit菜单中选择EndTime,在弹出窗口中Time出填入10,单位选择µs,同理在GrideSize中TimePeriod输入50ns,单击OK按钮,设置结束。

(3)输入工程的信号节点

单击Edit→Insert→InsertNodeorBUS…,即可弹出如图14的对话框,单击NodesFound选项,在NodesFound对话框Filter项中选择Pins:

All,然后单击List按钮,在下方的窗口中出现设计中的工程的所有窗口的引脚名,选择欲观察信号节点,用中间的“≥”将需要观察的信号选到右边,如图15所示,单击OK按钮,回到InsertNodeorBUS对话框,再单击OK按钮即可,如图16所示。

图14.

图15

图16

(4)设计输入信号波形

单击图16窗口的输入信号CP使之变成蓝色条,再单击右键,选择Value设置中的Clock对话框(如图17所示),设置其周期为50ns,同理分别设置其他信号的波形,波形编辑结果如图19所示。

双击图16所示输出信号CO、Q[7..0],将弹出信号输出格式设置对话框图18所示,在对话框的Radix中有6中选择,将在后续试验中要用到。

图17图18

图19

(5)启动仿真器,观察结果

所有设置完成后,选择“File”中的“SaveAs”项,将波形文件以默认名存盘后,即可启动仿真器Processing|StartSimulation,直到出现Simulationwassuccessful,仿真结束。

QuartusII9.0中默认的Simulationmode为Timing(时序仿真)仿真波形输出文件SimulationReport将自动弹出如图20所示,通过该图可查看实际设计的电路运行时是否满足延时要求。

注意,QuartusII的仿真波形文件中,波形编辑文件(*.bdf)与波形仿真报告输出文件(SimulationReport)是分开的,而MaxplusII的激励波形编辑文件与波形仿真报告输出文件是合二为一的。

图20

(6)包装元件入库

分析仿真结果正确无误后,选择File→Create/update→CreateSymbolFileforCurrentFile,将当前文件变成了一个包装好的单一元件(counter_100.bsf),并放置在工程路径指定的目录中以备后用。

Step7.下载实现及硬件测试

(1)确定引脚编号

为在试验系统上验证设计的正确性,完成硬件测试,必须进行用于实现设计电路的输入和输出端口与目标芯片引脚之间连接关系的引脚锁定工作。

对于GW48EDA实验平台