计算机组成原理典型例题讲解Word文档格式.docx

《计算机组成原理典型例题讲解Word文档格式.docx》由会员分享,可在线阅读,更多相关《计算机组成原理典型例题讲解Word文档格式.docx(14页珍藏版)》请在冰豆网上搜索。

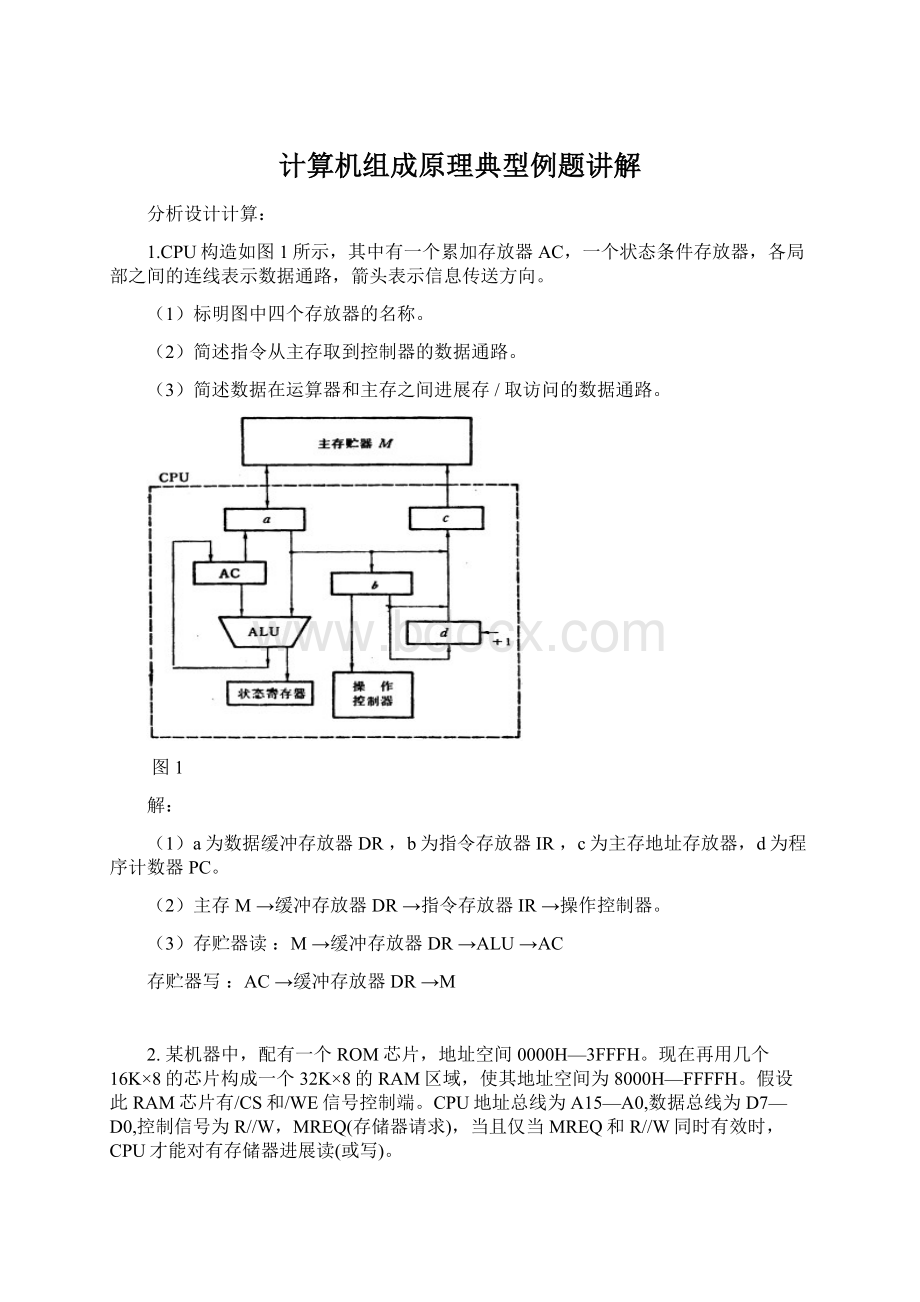

假设此RAM芯片有/CS和/WE信号控制端。

CPU地址总线为A15—A0,数据总线为D7—D0,控制信号为R//W,MREQ(存储器请求),当且仅当MREQ和R//W同时有效时,CPU才能对有存储器进展读(或写)。

〔1〕满足条件的存储器,画出地址码方案。

〔2〕画出此CPU与上述ROM芯片和RAM芯片的连接图。

存储器地址空间分布如图1所示,分三组,每组16K×

8位。

由此可得存储器方案要点如下:

(1)用两片16K*8RAM芯片位进展串联连接,构成32K*8的RAM区域。

片地址:

A0——A13,片选地址为:

A14——A15;

(2)译码使用2:

4译码器;

(3)用/MREQ作为2:

4译码器使能控制端,该信号低电平〔有效〕时,译码器工作。

(4)CPU的R//W信号与RAM的/WE端连接,当R//W=1时存储器执行读操作,当R//W=0时,存储器执行写操作。

如图1

图1

CPU与芯片连接如图2:

图2

3.某机器中,配有一个地址空间为(0000—1FFF)16的ROM区域,现在用一个SRAM芯片〔8K×

8位〕形成一个16K×

16位的ROM区域,起始地址为〔2000〕16。

假设SRAM芯片有/CS和/WE控制端,CPU地址总线A15——A0,数据总线为D15——D0,控制信号为R//W〔读/写〕,/MREQ〔当存储器读或写时,该信号指示地址总线上的地址是有效的〕。

要求:

(1)满足条件的存储器,画出地址码方案。

(2)画出ROM与RAM同CPU连接图。

解:

存储器地址空间分布如图1所示,分三组,每组8K×

16位。

(5)组地址:

A12——A0〔A0为低位〕;

(6)组号译码使用2:

(7)RAM1,RAM2各用两片SRAM芯片位进展并联连接,其中一片组成高8位,另一片组成低8位。

(8)用/MREQ作为2:

(9)

CPU的R//W信号与SRAM的/WE端连接,当R//W=1时存储器执行读操作,当R//W=0时,存储器执行写操作。

如图2

4.参见以下列图数据通路,画出数据指令“STAR1,(R2)〞的指令周期流程图,其含义是将存放器R1的容传送至〔R2〕为地址的存贮单元中。

标出各微操作信号序列。

5.用16K×

1位的动态RAM芯片构成64K×

8位的存储器,要求:

(1)画出该存储器组成的逻辑框图

(2)设存储器的读写周期均为0.5μs,CPU在1μs至少要访问存一次。

试问采用那种刷新方式比较合理?

两次刷新的最大时间间隔是多少?

对全部存储单元刷新一遍所需的实际刷新时间是多少?

〔1〕根据题意,存储器总容量为64KB,故地址线总需16位。

现使用16K×

1位的DRAM芯片,共需32片。

芯片本身地址线占14位,所以采用位并联与地址串联相结合的方法来组成整个存储器,其组成逻辑框图如下列图,其中使用一片2:

4译码器

(2)根据条件,CPU在1μs至少需要访存一次,所以整个存储器的平均读/写周期与单个存储器片的读/写周期相差不多,应采用异步式刷新方式比较合理。

DRAM存储器来讲,两次刷新的最大时间间隔是2ms.

DRAM芯片读/写周期为0.5μs。

假定16K×

1位的RAM芯片由128×

128矩阵存储元构成,刷新时只对128行进展异步式刷新,那么刷新间隔为2ms/128=15.6μs,可取刷新信号周期为15μs.

6.某16位机运算器框图如下列图,其中ALU为加法器,SA,SB为锁存器,4个通用存放器的读/写控制符号如下表所示:

(1)请设计微指令格式〔具体考虑控制字段,顺序控制字段只画框图〕

(2)“ADDR0,R1”指令完成〔R0〕+(R1)R1的操作,画出微程序流程图.

(1)微指令格式如下:

12位12位111111

R

RA0RA1

W

WA0WA1

LDSA

LDSB

LSB

reset

I

P字段

下址字段

其中LDSA,LDSB为锁存器打入信号,CLR为SB清零信号;

LSB为SB送原码控制信号,/LSB为SB送反码控制信号;

I为公共微程序信号

(2)流程图如图:

7.某计算机的数据通路如下列图,其中M—主存,MBR—主存数据存放器,MAR—主存地址存放器,R0-R3—通用存放器,IR—指令存放器,PC—程序计数器〔具有自增能力〕,C、D--暂存器,ALU—算术逻辑单元〔此处做加法器对待〕,移位器—左移、右移、直通传送。

所有双向箭头表示信息可以双向传送。

请按数据通路图画出“ADD〔R1〕,〔R2〕+〞指令的指令周期流程图。

该指令的含义是两个数进展求和操作。

其中源操作地址在存放器R1中,目的操作数寻址方式为自增型存放器间接寻址〔先取地址后加1〕。

“ADD〔R1〕,〔R2〕+〞指令是SS型指令,两个操作数均在主存中。

其中源操作数地址在R1中,所以是R1间接寻址。

目的操作数地址在R2中,由R2间接寻址,但R2的容在取出操作数以后要加1进展修改。

指令周期流程图如图

8.以下列图所示的处理机逻辑框图中,有两条独立的总线和两个独立的存贮器。

指令存贮器IM最大容量为16384字〔字长18位〕,数据存贮器DM最大容量是65536字〔字长16位〕。

设处理机指令格式为:

171090

OP

X

加法指令可写为“ADDX(R1)〞。

其功能是〔AC0〕+〔〔Ri〕+X〕→AC1,其中〔〔Ri〕+X〕局部通过寻址方式指向数据存贮器,现取Ri为R1。

〔1〕请写出以下各存放器的位数:

程序计数器PC;

指令存放器IR;

累加存放器AC0和AC1;

通用存放器R0—R3;

指令存储器的地址存放器IAR;

指令存储器的数据缓冲存放器IDR;

数据存储器的地址存放器DAR;

数据存储器的数据缓冲存放器DDR。

〔2〕试画出ADD指令从取指令开场到执行完毕的指令周期流程图。

〔1〕PC=14位IR=18位AC0=AC1=16位R0—R3=16位IAR=14位IDR=18位DAR=16位DDR=16位

〔2〕加法指令“ADDX〔Ri〕〞是一条隐含指令,其中一个操作数来自AC0,另一个操作数在数据存贮器中,地址由通用存放器的容〔Ri〕加上指令格式中的X量值决定,可认为这是一种变址寻址。

指令周期流程图如图3。

图3

9.某计算机有8条微指令I1—I8,每条微指令所包含的微命令控制信号见下表,a—j分别对应10种不同性质的微命令信号。

假设一条微指令的控制字段仅限8位,请安排微指令的控制字段格式。

〔答案不唯一〕为了压缩指令字的长度,必须设法把一个微指令周期中的互斥性微命令信号组合在一个小组中,进展分组译码。

经分析,〔e,f,h〕和〔b,i,j〕可分别组成两个小组或两个字段,然后进展译码,可得六个微命令信号,剩下的a,c,d,g四个微命令信号可进展直接控制,其整个控制字段组成如下:

01e01b

直接控制10f10i

acdg11h11j

4位2位2位

10.设有一运算器数据通路如图2所示。

假设操作数a和b〔补码〕已分别放在通用存放器R1和R2中,ALU有+,-,M〔传送〕三种操作功能。

(1)指出相容性微操作和相斥性微操作。

(2)用字段直接译码法设计适用此运算器的微指令格式。

〔1〕相斥性微操作有如下五组:

移位器〔R,L,V〕

ALU〔+,-,M〕

A选通门的4个控制信号

B选通门的7个控制信号

存放器的4个输入和输出控制信号

相容性微操作:

A选通门的任一信号与B选通门控制信号

B选通门的任一信号与A选通门控制信号

ALU的任一信号与加1控制信号

五组控制信号中组与组之间是相容性的

〔2〕每一小组的控制信号由于是相斥性的,故可以采用字段直接译码法,微指令格式如下:

a

b

c

d

e

f

XXX

XX

XXXX

3

2

1

4

001MDR→A001PC→B01+01R1+10001Pcout

010R1→A010R1→B10-10L0010Pcin

011R2→A011R1→B11M11V0011R1out

100R3→A100R2→B0100R1in

101R2→B0101R2out

110R3→B0110R2in

111R3→B0111R3out

1000R3in

【例】CPU的地址总线16根(A15—A0,A0为低位),双向数据总线8根(D7—D0),控制总线中与主存有关的信号有MREQ(允许访存,低电平有效),R/W(高电平为读命令,低电平为写命令)。

主存地址空间分配如下:

0—8191为系统程序区,由只读存储芯片组成;

8192—32767为用户程序区;

最后(最址)2K地址空间为系统程序工作区。

上述地址为十进制,按字节编址。

现有如下存储器芯片:

EPROM:

8K×

8位(控制端仅有CS);

SRAM:

16K×

1位,2K×

8位,4K×

8位,8K×

8位.请从上述芯片中选择适当芯片设计该计算机主存储器,画出主存储器逻辑框图,注意画出选片逻辑(可选用门电路及3∶8译码器74LS138)与CPU的连接,说明选哪些存储器芯片,选多少片。

【解】主存地址空间分布如下列图。

根据给定条件,选用EPROM:

8位芯片1片。

8位芯片3片,2K×

3∶8译码器仅用Y0,Y1,Y2,Y3和Y7输出端,且对最后的2K×

8位芯片还需加门电路译码。

主存储器的组成与CPU连接逻辑图如下列图: