计算机组成原理课程设计硬布线控制器的设计与实现Word文档下载推荐.docx

《计算机组成原理课程设计硬布线控制器的设计与实现Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《计算机组成原理课程设计硬布线控制器的设计与实现Word文档下载推荐.docx(18页珍藏版)》请在冰豆网上搜索。

指令格式

SWC

SWB

SWA

KRR

读寄存器堆方式

1

KRD

读双端口存储器方式

KWE

写双端口存储器方式

KLD

加载寄存器堆方式

PR

启动程序方式

机器指令名称

助记符

R7

R6

R5

R4

R3

R2

R1

R0

加法

ADDRd,Rs

Rd+Rs->

Rd

RS1

RS0

RD1

RD0

减法

SUBRd,Rs

Rd-Rs->

乘法

MULRd,Rs

Rd*Rs->

逻辑与

ANDRd,Rs

Rd&

Rs->

存数

STARd,[Rs]

Rd->

[Rs]

取数

LDARd,[Rs]

[Rs]->

Rd

无条件转移

JMP[Rs]

PC

条件转移

JCD

C=1

PC+D->

D3

D2

D1

D0

停机

STP

暂停运行

X

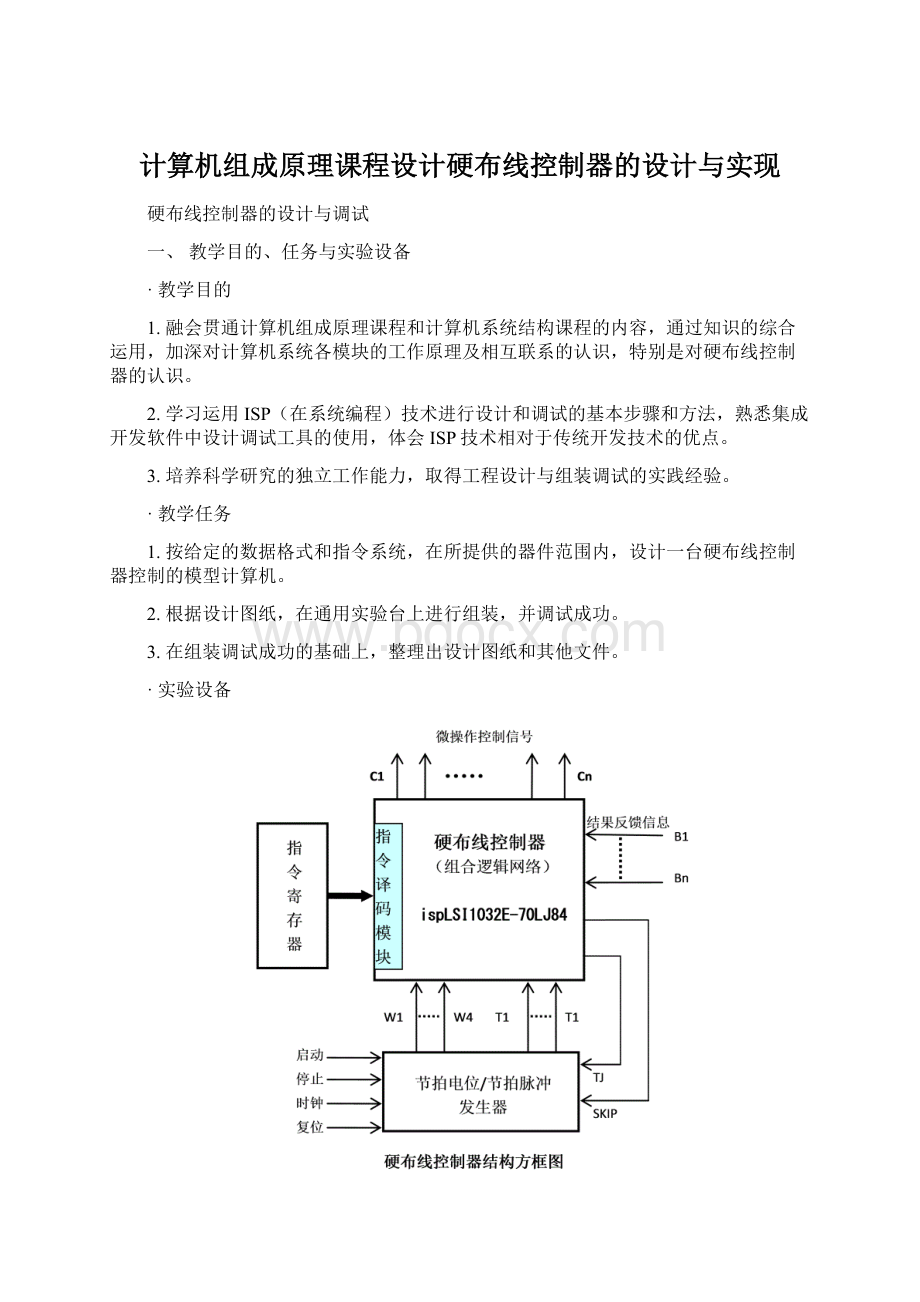

老师提供的控制台指令流程图:

在这个控制台里,我们将控制台指令KRR,KRD,KWE,KLD,PR分别拆分为KRR1,KRR2,KRD1,KRD2,KWE1,KWE2,KLD1,KLD2和PR1,PR2。

每个小指令分别占用W1-W4四个节拍。

分2次执行完成。

控制信号

信号作用

信号有效条件

C

在加法运算和减法运算时产生的进位信号

T4上升沿

ALU_BUS

允许运算结果送往数据总线

LDDR1

M1=0时DR1接收寄存器堆A端口数据

T3下降沿

M1=1时DR1接收数据总线DBUS数据

LDDR2

M2=0时DR2接收寄存器堆B端口数据

M2=1时DR2接收数据总线DBUS数据

WRD

控制双端口寄存器堆RF的写操作

1且T2上升沿

RS_BUS#

控制RF的B端口数据是否能送DBUS上

LDER

将DBUS上的数据打入暂存寄存器ER

1且T4上升沿

SW_BUS#

将SW7-SW0数据送往DBUS

CEL#

选中双端口存储器RAM左端口

LRW

允许RAM左端口读操作

1且T3上升沿

允许RAM左端口写操作

0且T3上升沿

CER

RAM右端口读出数据并放到指令总线INS上

禁止右端口操作

LDAR1

将DBUS数据打入地址寄存器AR1

AR1_INC

AR1的值加1

LDAR2

M3=0时AR2的数据从程序计数器PC打入

1且T2下降沿

M3=1时AR2的数据从DBUS打入

LDR4

M4=1时R4的数据从DBUS打入

M4=0时R4的数据从IR0-IR3打入

PC_ADD

ALU2完成PC和IR低4位相加即PC+D

PC_INC

PC+1

LDPC

程序计数器PC接收来自DBUS的地址

LDIR

将来自RAM的指令打入指令寄存器IR

S2,S1,S0

选择运算器ALU的运算类型

控制台控制信号作用:

三、设计方案

设计硬布线控制器的控制流程,也就是解决Mi、Im、Bj如何起作用的问题。

设计微程序控制器时可以使用流程图,设计硬布线控制器同样可以使用流程图。

微程序控制器的控制信号以微指令周期为时间单位,硬布线控制器以节拍为时间单位,两者本质上是一样的,1拍和1个微指令周期都是从时序T1的上升沿到

T4的下降沿的一段时间。

在微程序控制流程图中,1个执行框代表1个微指令周期,而在硬布线控制流程图中,1个执行框就代表1拍。

执行一条机器指令所需的微指令数目,在硬布线控制器中相当于机器指令所需的节拍数。

决定执行一条指令需要的节拍数,要根据所有指令而定。

既不能只考虑某些需要最多节拍的指令,也不能只考虑节拍数最少的指令,一般要根据大多数机器指令所需的节拍数而定,设计才比较合理。

在本实验中,由于选用4拍对大多数指令就够用,所以节拍发生器产生4个节拍信号(W1—W4)。

统一用4拍执行1条机器指令后,对于所需节拍较少的的指令,例如JMP指令只用2拍(忽略中断),剩下2拍就无事可做了。

这在可行性上当然没有问题,但在性能上就打了折扣,因为多余的节拍都浪费掉了。

为减少浪费,在时序电路中加入了一个控制信号SKIP的输入,该信号的作用是使节拍发生器在任意状态下直接跳到最后1拍(W4)。

这样,设计控制流程时,在所需节拍较少的的指令流程的适当位置使SKIP控制信号有效,多余的节拍就可以跳过,从而提高了性能。

机器指令选用四拍以后,将一条机器指令的执行化为占用两条(或者更多)机器指令的节拍,执行一条指令就可以占用W1、W2、W3、W4、W1、W2、W3、W4。

为了区分一条指令的两个不同阶段,我们加了个ST内部信号作为标志位,当ST=0时,标志执行指令的前四个节拍,当ST=1时,标志执行指令的后四个节拍。

注意到只有CLR#到来后的第四拍时ST信号才发生翻转,所以又设了一个SSTO信号作为ST信号的触发信号。

具体实现ST-SSTO模块如下:

我们增加了一个标志位RUN,由于按CLR#按钮复位后,实验系统的时序停止在T4,W4,ST的值为0,这样SSTO=!

ST&

W4的值为1.按QD启动按钮后,由于立即产生T1信号,在T1的上升沿使ST置1,在第一组W1,W2,W3,W4时,ST的值为1,这是我们不希望看到的。

增加了标志位RUN后,按CLR#按钮复位,使RUN为0。

由于SSTO=!

ST*W4*RUN,因此复位后的SSTO=0.按QD启动按钮,在T1的上升沿,使RUN=1。

根据SSTO的布尔表达式,在W1,W2,W3时,SSTO=0,直到W4时,才使SSTO=1,由于ST:

=CLR#*SSTO#CLR*ST,在W4过后的下一个T1的上升沿,才使ST置1,从而将控制台操作的两种状态区分开来。

根据控制台指令设计出的硬布线控制器:

逻辑状态表:

根据硬布线指令流程图画出状态表,然后根据表格,列写出每个信号的逻辑表达式,并写出ABEL语言的源程序:

(状态表在此文档最后可见。

去下载横版:

本来是有这个版本的,可以在打印出来的时候添加到中间空白的这一页,只可以我上传的那张表,XX未审核通过,说我的文档质量太低了,虽然我设置的是免费。

算了,自己用Excel改一下吧。

)

四、

设计的实现(ABEL-HDL)

ABEL语言源代码如下:

MODULEComputeDECLARATIONS

"

输入管脚

SWC,SWB,SWAPIN3..5;

IR7,IR6,IR5,IR4PIN6..9;

MF,T1,W1,W2,W3,W4,C,CLRPIN10..17;

输出管脚

ALU_BUS,AR1_INC,CEL,CER,LDAR1,LDAR2,LDDR1,LDDR2,LDER,LDIR,LDPC,LDR4,LRWPIN29..41;

PC_INC,PC_ADD,RS_BUS,SW_BUS,WRD,SKIP,TJ,M1,M2,M3,M4,S0,S1,S2PIN45..58;

自定义

MF1,SSTONODEISTYPE'

COM'

;

RUN,STNODEISTYPE'

REG'

tKRR,tKRD,tKWE,tKLD,tPRNODEISTYPE'

KRR1,KRD1,KWE1,KLD1,PR1,KRR2,KRD2,KWE2,KLD2,PR2NODEISTYPE'

ADD,SUB,MUL,AND,LDA,STA,JMP,JC,STPNODEISTYPE'

CLK=.C.;

EQUATIONS

MF1=!

CLR&

MF#T1&

CLR;

RUN:

=CLR;

RUN.CLK=MF1;

ST:

=CLR&

SSTO#CLR&

ST;

ST.CLK=MF1;

SSTO=!

RUN&

W4;

指令译码部分

tKRR=SWC&

!

SWB&

SWA;

tKRD=!

SWC&

tKWE=!

tKLD=!

tPR=!

KRR1=!

tKRR;

KRR2=ST&

KRD1=!

tKRD;

KRD2=ST&

KWE1=!

tKWE;

KWE2=ST&

KLD1=!

tKLD;

KLD2=ST&

PR1=!

tPR;

PR2=ST&

ADD=PR2&

(!

IR7)&

IR6)&

IR5)&

IR4);

SUB=PR2&

(IR4);

MUL=PR2&

(IR5)&

AND=PR2&

LDA=PR2&

(IR6)&

STA=PR2&

JMP=PR2&

(IR7)&

JC=PR2&

STP=PR2&

数据通路管脚译码

ALU_BUS=(ADD#SUB#MUL#AND)&

W3#(STA&

W4);

AR1_INC=(KRD2#KWE2)&

CEL=!

((KRD2#KWE2#KLD2#KRR2)&

W1#(W3&

LDA)#(W4&

STA));

CER=(KLD2#KRR2)&

W2#(W1&

PR2);

LDAR1=W4&

(KRR1#KRD1#KWE1#KLD1)#(W2&

LDA)#(W2&

STA);

LDAR2=W4&

(KRR1#KLD1)#(PR2&

W1);

LDDR1=W2&

(ADD#SUB#MUL#AND);

LDDR2=LDDR1#(W2&

LDER=W3&

(KLD2#ADD#SUB#MUL#AND#LDA);

LDIR=CER;

LDPC=W4&

(PR1#JMP#(JC&

C));

LDR4=LDPC;

LRW=W1&

KRD2#W3&

LDA;

M1=!

LDDR1;

M2=!

LDDR2;

M3=W4&

(KRR1#KLD1);

M4=W4&

(PR1#JMP);

PC_INC=W1&

PR2;

PC_ADD=W4&

JC&

C;

RS_BUS=!

(W2&

(LDA#STA)#W4&

(KRR2#JMP));

SW_BUS=!

(W1&

(KWE2#KLD2#KRR2)#(W3&

KLD2)#(W4&

ST));

S0=SUB#STA;

S1=ADD#SUB;

S2=MUL;

SKIP=W1&

ST#(W1&

(KRD2#KWE2))#(W2&

(KRR2#STA))#W2&

(JMP#JC#STP);

TJ=W1&

KRD2#W2&

KLD2#W4&

(tKRR#tKWE#tKLD)#W4&

STP;

WRD=W4&

END

对程序进行编译,无误后下载到芯片。

连线,调试,验收

连线按照ABEL程序里面对管脚的定义连线

寄存器和内存单元内容:

寄存器

存入内容

内存单元

60H

24H

61H

83H

计算结果:

内容

0A7H

五、本次设计的体会

这是我们计算机专业做的第一个硬件和软件结合的课程设计,个人认为,这是最好的一个课程设计安排,将学习道德东西用起来,才是最好的结果,锻炼了我们的动手能力和思考能力。

硬布线控制器在课本上没有详细讲解,但却是以前的CPU使用的布线方式,想要深入学习硬件知识,了解这些东西是很有必要的。

微程序控制器的出现是为了代替硬布线控制器,如果没有对微程序控制器的工作方式和原理的理解,不可能设计出硬布线控制器的控制逻辑。

所以这次实验,我们对计算机的工作原理有了更进一步的了解,尤其是指令系统的工作原理,各个部件的工作之间的协调和配合等。

这次课程设计大大锻炼了我们的动手能力,由于是手工接线,任何一条线出现问题都会影响到整个系统的执行,幸好我们都很细心的连线,在这方面没出问题,也让我感觉到认真的去做一件事情的确不是那么的容易。

分析也变得尤为重要。

不仅如此,设计过程中团队的合作精神也得到了锻炼,任何一个项目的完成,都需要大家的通力合作。

实验中需要将所编程序下载到芯片中,这就使我们对现今硬件设计软件化的主流方向有了实践层次的理解,并让我们掌握了一些简单的设计实现方法。

总之,本次实验是一次难得的学习与发挥的机会,也是我最喜欢的一个课程设计,在实验让我体会到了思考与创造的乐趣。

参考文献:

1.《计算机组成原理》白中英老师编写

2.本学期的五次实验指导书

OUTPUT

ST=0

ST=1

KRR1

KRD1

KWE1

KLD1

PR1

KRR2

KRD2

KWE2

KLD2

W4

W1

W2

W3

M1

M2

M3

M4

S0

S1

S2

W1,W3

SKIP

TJ

W2,W4

SSTO

ST=1PR2

PR2

ADD

SUB

MUL

AND

LDA

STA

JMP

JC

W4&