s3c6410寄存器定义Word下载.docx

《s3c6410寄存器定义Word下载.docx》由会员分享,可在线阅读,更多相关《s3c6410寄存器定义Word下载.docx(49页珍藏版)》请在冰豆网上搜索。

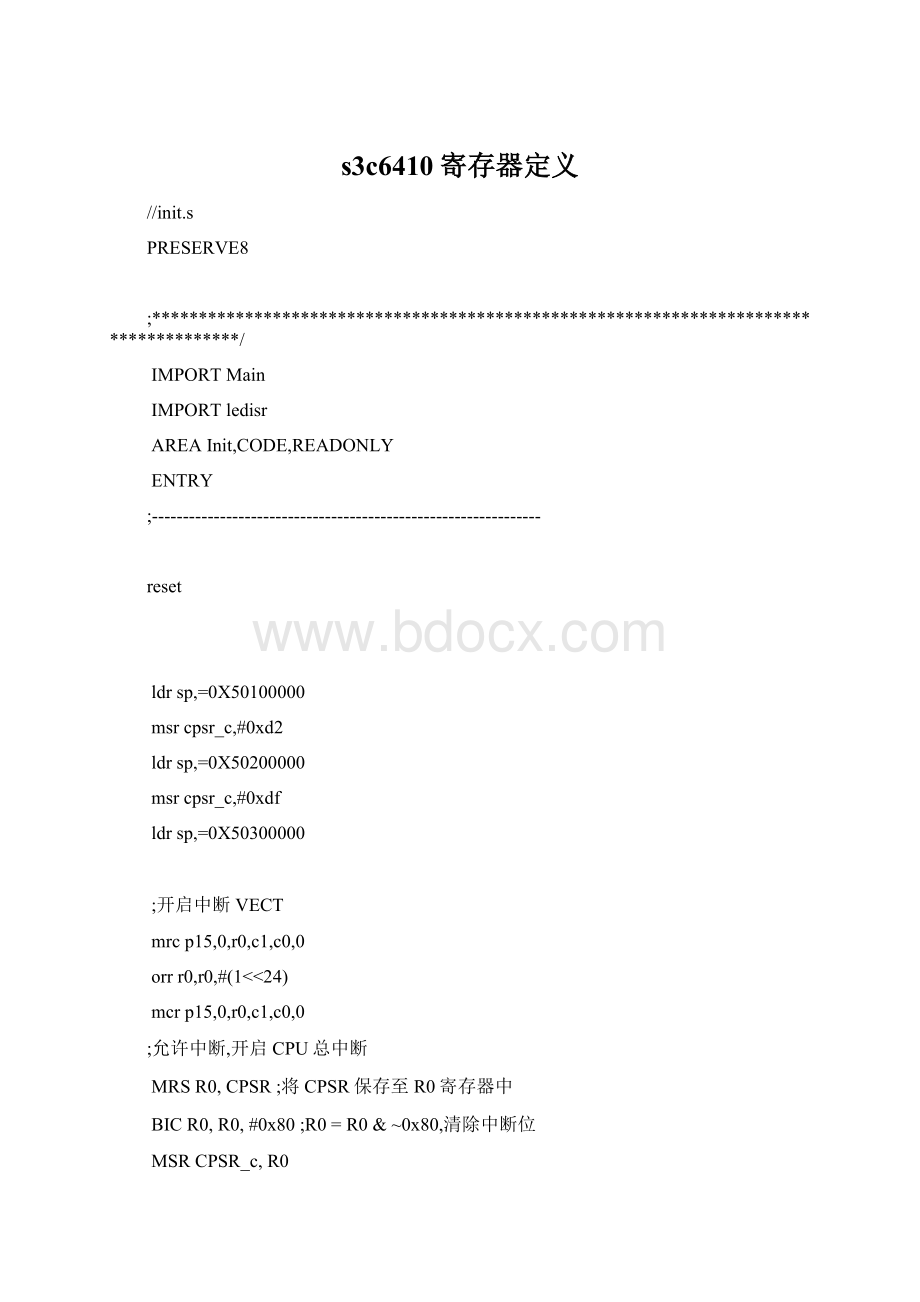

将CPSR保存至R0寄存器中

BICR0,R0,#0x80;

R0=R0&

~0x80,清除中断位

MSRCPSR_c,R0

blMain

END

//main.c

#include"

s3c6410.h"

#definekeyconGPNCON_REG

#definekeyGPNDAT_REG

#defineledconGPMCON_REG

#defineledGPMDAT_REG//gpm0~3

voiddelay(void);

voidledisr(void)__irq;

voiddelay(void)

{

unsignedinti=20000000;

while(i--);

}

voidMain(void)

ledcon|=0xf;

led=0;

keycon&

=1<

2;

keycon|=0x2;

EINT0CON0&

3;

EINT0CON0|=0x6;

EINT0MASK&

=~(0x1);

VIC0VECTADDR[0]=(int)ledisr;

VIC0INTSELECT&

=~(1<

0);

VIC0INTENABLE|=1<

0;

while

(1)

{

led|=0xf;

}

voidledisr(void)__irq

led&

=~(0xf);

delay();

EINT0PEND=1;

VIC0ADDRESS=0;

//s3c6410.h

/*

form\Linux-3.0.1\uboot_sourcecode\uboot1.1.6-2012-09-25\uboot1.1.6\include

*/

#ifndef__S3C6410_H__

#define__S3C6410_H__

#ifndefCONFIG_S3C6410

#defineCONFIG_S3C64101

#endif

#defineS3C64XX_UART_CHANNELS3

#defineS3C64XX_SPI_CHANNELS2

#define__REG(x)(*(volatileunsigned*)(x))//copyfromhardware.h

#ifndef__ASSEMBLY__

typedefenum{

S3C64XX_UART0,

S3C64XX_UART1,

S3C64XX_UART2,

S3C64XX_UART3,

}S3C64XX_UARTS_NR;

//#include<

s3c64x0.h>

#defineBIT00x00000001

#defineBIT10x00000002

#defineBIT20x00000004

#defineBIT30x00000008

#defineBIT40x00000010

#defineBIT50x00000020

#defineBIT60x00000040

#defineBIT70x00000080

#defineBIT80x00000100

#defineBIT90x00000200

#defineBIT100x00000400

#defineBIT110x00000800

#defineBIT120x00001000

#defineBIT130x00002000

#defineBIT140x00004000

#defineBIT150x00008000

#defineBIT160x00010000

#defineBIT170x00020000

#defineBIT180x00040000

#defineBIT190x00080000

#defineBIT200x00100000

#defineBIT210x00200000

#defineBIT220x00400000

#defineBIT230x00800000

#defineBIT240x01000000

#defineBIT250x02000000

#defineBIT260x04000000

#defineBIT270x08000000

#defineBIT280x10000000

#defineBIT290x20000000

#defineBIT300x40000000

#defineBIT310x80000000

#defineROM_BASE00x00000000/*baseaddressofrombank0*/

#defineROM_BASE10x04000000/*baseaddressofrombank1*/

#defineDRAM_BASE00x40000000/*baseaddressofdrambank0*/

#defineDRAM_BASE10x50000000/*baseaddressofdrambank1*/

/*S3C6400devicebaseaddresses*/

#defineELFIN_DMA_BASE0x75000000

#defineELFIN_LCD_BASE0x77100000

#defineELFIN_USB_HOST_BASE0x74300000

#defineELFIN_I2C_BASE0x7f004000

#defineELFIN_I2S_BASE0x7f002000

#defineELFIN_ADC_BASE0x7e00b000

#defineELFIN_SPI_BASE0x7f00b000

#defineELFIN_HSMMC_0_BASE0x7c200000

#defineELFIN_HSMMC_1_BASE0x7c300000

#defineELFIN_HSMMC_2_BASE0x7c400000

#defineELFIN_CLOCK_POWER_BASE0x7e00f000

/*Clock&

PowerControllerformDirac3*/

#defineAPLL_LOCK_OFFSET0x00

#defineMPLL_LOCK_OFFSET0x04

#defineEPLL_LOCK_OFFSET0x08

#defineAPLL_CON_OFFSET0x0C

#defineMPLL_CON_OFFSET0x10

#defineEPLL_CON0_OFFSET0x14

#defineEPLL_CON1_OFFSET0x18

#defineCLK_SRC_OFFSET0x1C

#defineCLK_DIV0_OFFSET0x20

#defineCLK_DIV1_OFFSET0x24

#defineCLK_DIV2_OFFSET0x28

#defineCLK_OUT_OFFSET0x2C

#defineHCLK_GATE_OFFSET0x30

#definePCLK_GATE_OFFSET0x34

#defineSCLK_GATE_OFFSET0x38

#defineAHB_CON0_OFFSET0x100

#defineAHB_CON1_OFFSET0x104

#defineAHB_CON2_OFFSET0x108

#defineSELECT_DMA_OFFSET0x110

#defineSW_RST_OFFSET0x114

#defineSYS_ID_OFFSET0x118

#defineMEM_SYS_CFG_OFFSET0x120

#defineQOS_OVERRIDE0_OFFSET0x124

#defineQOS_OVERRIDE1_OFFSET0x128

#defineMEM_CFG_STAT_OFFSET0x12C

#definePWR_CFG_OFFSET0x804

#defineEINT_MASK_OFFSET0x808

#defineNOR_CFG_OFFSET0x810

#defineSTOP_CFG_OFFSET0x814

#defineSLEEP_CFG_OFFSET0x818

#defineOSC_FREQ_OFFSET0x820

#defineOSC_STABLE_OFFSET0x824

#definePWR_STABLE_OFFSET0x828

#defineFPC_STABLE_OFFSET0x82C

#defineMTC_STABLE_OFFSET0x830

#defineOTHERS_OFFSET0x900

#defineRST_STAT_OFFSET0x904

#defineWAKEUP_STAT_OFFSET0x908

#defineBLK_PWR_STAT_OFFSET0x90C

#defineINF_REG0_OFFSET0xA00

#defineINF_REG1_OFFSET0xA04

#defineINF_REG2_OFFSET0xA08

#defineINF_REG3_OFFSET0xA0C

#defineINF_REG4_OFFSET0xA10

#defineINF_REG5_OFFSET0xA14

#defineINF_REG6_OFFSET0xA18

#defineINF_REG7_OFFSET0xA1C

#defineOSC_CNT_VAL_OFFSET0x824

#definePWR_CNT_VAL_OFFSET0x828

#defineFPC_CNT_VAL_OFFSET0x82C

#defineMTC_CNT_VAL_OFFSET0x830

#defineAPLL_LOCK_REG__REG(ELFIN_CLOCK_POWER_BASE+APLL_LOCK_OFFSET)

#defineMPLL_LOCK_REG__REG(ELFIN_CLOCK_POWER_BASE+MPLL_LOCK_OFFSET)

#defineEPLL_LOCK_REG__REG(ELFIN_CLOCK_POWER_BASE+EPLL_LOCK_OFFSET)

#defineAPLL_CON_REG__REG(ELFIN_CLOCK_POWER_BASE+APLL_CON_OFFSET)

#defineMPLL_CON_REG__REG(ELFIN_CLOCK_POWER_BASE+MPLL_CON_OFFSET)

#defineEPLL_CON0_REG__REG(ELFIN_CLOCK_POWER_BASE+EPLL_CON0_OFFSET)

#defineEPLL_CON1_REG__REG(ELFIN_CLOCK_POWER_BASE+EPLL_CON1_OFFSET)

#defineCLK_SRC_REG__REG(ELFIN_CLOCK_POWER_BASE+CLK_SRC_OFFSET)

#defineCLK_DIV0_REG__REG(ELFIN_CLOCK_POWER_BASE+CLK_DIV0_OFFSET)

#defineCLK_DIV1_REG__REG(ELFIN_CLOCK_POWER_BASE+CLK_DIV1_OFFSET)

#defineCLK_DIV2_REG__REG(ELFIN_CLOCK_POWER_BASE+CLK_DIV2_OFFSET)

#defineCLK_OUT_REG__REG(ELFIN_CLOCK_POWER_BASE+CLK_OUT_OFFSET)

#defineHCLK_GATE_REG__REG(ELFIN_CLOCK_POWER_BASE+HCLK_GATE_OFFSET)

#definePCLK_GATE_REG__REG(ELFIN_CLOCK_POWER_BASE+PCLK_GATE_OFFSET)

#defineSCLK_GATE_REG__REG(ELFIN_CLOCK_POWER_BASE+SCLK_GATE_OFFSET)

#defineAHB_CON0_REG__REG(ELFIN_CLOCK_POWER_BASE+AHB_CON0_OFFSET)

#defineAHB_CON1_REG__REG(ELFIN_CLOCK_POWER_BASE+AHB_CON1_OFFSET)

#defineAHB_CON2_REG__REG(ELFIN_CLOCK_POWER_BASE+AHB_CON2_OFFSET)

#defineSELECT_DMA_REG__REG(ELFIN_CLOCK_POWER_BASE+SELECT_DMA_OFFSET)

#defineSW_RST_REG__REG(ELFIN_CLOCK_POWER_BASE+SW_RST_OFFSET)

#defineSYS_ID_REG__REG(ELFIN_CLOCK_POWER_BASE+SYS_ID_OFFSET)

#defineMEM_SYS_CFG_REG__REG(ELFIN_CLOCK_POWER_BASE+MEM_SYS_CFG_OFFSET)

#defineQOS_OVERRIDE0_REG__REG(ELFIN_CLOCK_POWER_BASE+QOS_OVERRIDE0_OFFSET)

#defineQOS_OVERRIDE1_REG__REG(ELFIN_CLOCK_POWER_BASE+QOS_OVERRIDE1_OFFSET)

#defineMEM_CFG_STAT_REG__REG(ELFIN_CLOCK_POWER_BASE+MEM_CFG_STAT_OFFSET)

#definePWR_CFG_REG__REG(ELFIN_CLOCK_POWER_BASE+PWR_CFG_OFFSET)

#defineEINT_MASK_REG__REG(ELFIN_CLOCK_POWER_BASE+EINT_MASK_OFFSET)

#defineNOR_CFG_REG__REG(ELFIN_CLOCK_POWER_BASE+NOR_CFG_OFFSET)

#defineSTOP_CFG_REG__REG(ELFIN_CLOCK_POWER_BASE+STOP_CFG_OFFSET)

#defineSLEEP_CFG_REG__REG(ELFIN_CLOCK_POWER_BASE+SLEEP_CFG_OFFSET)

#defineOSC_FREQ_REG__REG(ELFIN_CLOCK_POWER_BASE+OSC_FREQ_OFFSET)

#defineOSC_CNT_VAL_REG__REG(ELFIN_CLOCK_POWER_BASE+OSC_CNT_VAL_OFFSET)

#definePWR_CNT_VAL_REG__REG(ELFIN_CLOCK_POWER_BASE+PWR_CNT_VAL_OFFSET)

#defineFPC_CNT_VAL_REG__REG(ELFIN_CLOCK_POWER_BASE+FPC_CNT_VAL_OFFSET)

#defineMTC_CNT_VAL_REG__REG(ELFIN_CLOCK_POWER_BASE+MTC_CNT_VAL_OFFSET)

#defineOTHERS_REG__REG(ELFIN_CLOCK_POWER_BASE+OTHERS_OFFSET)

#defineRST_STAT_REG__REG(ELFIN_CLOCK_POWER_BASE+RST_STAT_OFFSET)

#defineWAKEUP_STAT_REG__REG(ELFIN_CLOCK_POWER_BASE+WAKEUP_STAT_OFFSET)

#defineBLK_PWR_STAT_REG__REG(ELFIN_CLOCK_POWER_BASE+BLK_PWR_STAT_OFFSET)

#defineINF_REG0_REG__REG(ELFIN_CLOCK_POWER_BASE+INF_REG0_OFFSET)

#defineINF_REG1_REG__REG(ELFIN_CLOCK_POWER_BASE+INF_REG1_OFFSET)

#defineINF_REG2_REG__REG(ELFIN_CLOCK_POWER_BASE+INF_REG2_OFFSET)

#defineINF_REG3_REG__REG(ELFIN_CLOCK_POWER_BASE+INF_REG3_OFFSET)

#defineINF_REG4_REG__REG(ELFIN_CLOCK_POWER_BASE+INF_REG4_OFFSET)

#defineINF_REG5_REG__REG(ELFIN_CLOCK_POWER_BASE+INF_REG5_OFFSET)

#defineINF_REG6_REG__REG(ELFIN_CLOCK_POWER_BASE+INF_REG6_OFFSET)

#defineINF_REG7_REG__REG(ELFIN_CLOCK_POWER_BASE+INF_REG7_OFFSET)

#defineAPLL_LOCK(ELFIN_CLOCK_POWER_BASE+APLL_LOCK_OFFSET)

#defineMPLL_LOCK(ELFIN_CLOCK_POWER_BASE+MPLL_LOCK_OFFSET)

#defineEPLL_LOCK(ELFIN_CLOCK_POWER_BASE+EPLL_LOCK_OFFSET)

#defineAPLL_CON(ELFIN_CLOCK_POWER_BASE+APLL_CON_OFFSET)

#defineMPLL_CON(ELFIN_CLOCK_POWER_BASE+MPLL_CON_OFFSET)

#defineEPLL_CON0(ELFIN_CLOCK_POWER_BASE+EPLL_CON0_OFFSET)

#defineEPLL_CON1(ELFIN_CLOCK_POWER_BASE+EPLL_CON1_OFFSET)

#defineCLK_SRC(ELFIN_CLOCK_POWER_BASE+CLK_SRC_OFFSET)

#defineCLK_DIV0(ELFIN_CLOCK_POWER_BASE+CLK_DIV0_OFFSET)

#defineCLK_DIV1(ELFIN_CLOCK_POWER_BASE+CLK_DIV1_OFFSET)

#defineCLK_DIV2(ELFIN_CLOCK_POWER_BASE+CLK_DIV2_OFFSET)

#defineCLK_OUT(ELFIN_CLOCK_POWER_BASE+CLK_OUT_OFFSET)

#defineHCLK_GATE(ELFIN_CLOCK_POWER_BASE+HCLK_GATE_OFFSET)

#definePCLK_GATE(ELFIN_CLOCK_POWER_BASE+PCLK_GATE_OFFSET)

#defineSCLK_GATE(ELFIN_CLOCK_POWER_BASE+SCLK_GATE_OFFSET)

#defineAHB_CON0(ELFIN_CLOCK_POWER_BASE+AHB_CON0_OFFSET)

#defineAHB_CON1(ELFIN_CLOCK_POWER_BASE+AHB_CON1_OFFSET)

#defineAHB_CON2(ELFIN_CLOCK_POWER_BASE+AHB_CON2_OFFSET)

#defineSELECT_DMA(ELFIN_CLOCK_POWER_BASE+SELECT_DMA_OFFSET)

#defineSW_RST(ELFIN_CLOCK_POWER_BASE+SW_RST_OFFSET)

#defineSYS_ID(ELFIN_CLOCK_POWER_BASE+SYS_ID_OFFSET)

#defineMEM_SYS_CFG(ELFIN_CLOCK_POWER_BASE+MEM_SYS_CFG_OFFSET)

#defineQOS_OVERRIDE0(ELFIN_CLOCK_POWER_BASE+QOS_OVERRIDE0_OFFSET)

#defineQOS_OVERRIDE1(ELFIN_CLOCK_POWER_BASE+QOS_OVERRIDE1_OFFSET)

#defineMEM_CFG_STAT(ELFIN_CLOCK_POWER_BASE+MEM_CFG_STAT_OFFSET)

#definePWR_CFG(ELFIN_CLOCK_POWER_BASE+PWR_CFG_OFFSET)

#defineEINT_MASK(ELFIN_CLOCK_POWER_BASE+EI