4104Muon子鉴别器读出电子学3文档格式.docx

《4104Muon子鉴别器读出电子学3文档格式.docx》由会员分享,可在线阅读,更多相关《4104Muon子鉴别器读出电子学3文档格式.docx(8页珍藏版)》请在冰豆网上搜索。

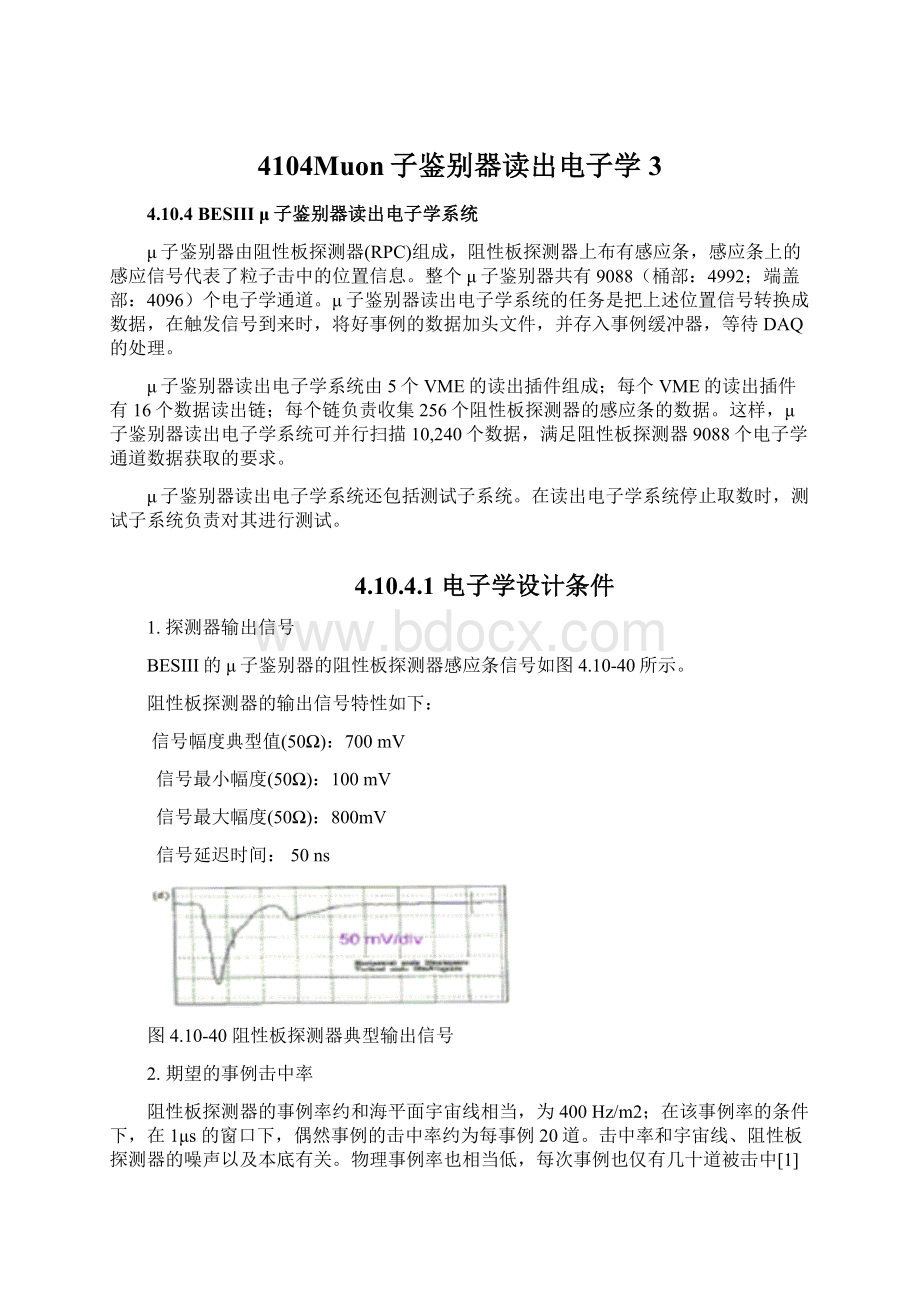

BESIII的μ子鉴别器的阻性板探测器感应条信号如图4.10-40所示。

阻性板探测器的输出信号特性如下:

信号幅度典型值(50Ω):

700mV

信号最小幅度(50Ω):

100mV

信号最大幅度(50Ω):

800mV

信号延迟时间:

50ns

图4.10-40阻性板探测器典型输出信号

2.期望的事例击中率

阻性板探测器的事例率约和海平面宇宙线相当,为400Hz/m2;

在该事例率的条件下,在1μs的窗口下,偶然事例的击中率约为每事例20道。

击中率和宇宙线、阻性板探测器的噪声以及本底有关。

物理事例率也相当低,每次事例也仅有几十道被击中[1]。

μ子鉴别器的阻性板探测器是低噪声和低事例占有率的探测器。

事例击中率为0.10~0.25Hz/cm2。

3.死时间

前端电子学读出板使用流水线技术,无死时间。

4.甄别阈值要求

所有电子学通道的阈值相同,统一可调,软件控制。

阈值调整精度为1%。

5.触发特性

触发延迟时间:

6.4μs

触发脉冲最大晃动:

0.2μs

平均触发率:

4kHz

6.测试

所有电子学通道的测试信号相同,测试脉冲幅度的精度为1%。

根据以上设计条件,同时根据阻性板探测器通道数大的特点,μ子鉴别器读出电子学系统必须在权衡合理造价的条件下,寻求最佳的性能价格比的设计方案。

4.10.4.2μ子鉴别器读出电子学系统结构

从系统功能来说,μ子鉴别器电子学系统可分为数据读出、甄别阈控制和系统测试等三个部分。

而就它的物理结构而言,μ子鉴别器电子学系统由放置在探测器附近的1个9U的VME机箱和4个电源机箱组成。

在探测器上方中间,放置VME系统机箱,1个系统控制插件(SystemControlModule)、1个VME读出插件(Readout)、4个扇入扇出插件(I/OModule)和14个JTAG控制插件被安置在这个机箱中。

系统控制插件从探测器主触发系统接收系统时钟和触发控制信号(L1,Check,Reset),并通过VME扩展总线将这些信号传送到I/O插件驱动输出;

接受通过VMEBUS发出的前端板阈值设置命令和TEST控制命令(系统测试控制),并通过VME扩展总线送到I/O插件驱动输出;

从VME扩展总线接收读出插件送来的FULL信号,驱动后送主触发系统。

扇入扇出插件(I/O插件)负责驱动时钟和触发控制信号,送到所有的前端板(FEC);

从FEC接收串行数据输出和FECBufferFull信号并传送到读出插件。

每个数据链一个I/O接口;

每个I/O插件配置12个I/O接口,4个插件共48个I/O接口,满足系统36-40个数据链的要求。

同时,鉴于大的RPC探测器的放电脉冲对FEC中FPGA芯片功能的可能损坏,在扇入扇出插件(I/O插件)中设有FPGA功能实时核对的数据模式(DataPattern)的输入/输出线,以便在探测到FPGA功能损坏的情况下,及时对FGPA功能数据的重新装载。

读出插件负责所有的数据链数据读出和压缩、子事例组建,并存放到缓冲区中,申请DAQ读出子事例数据;

与FEC交换FULL信号控制数据链的数据传输;

根据主触发的控制信号进行L1的检查和复位,并向主触发提供BufferFULL信号和RERR信号;

完成数据读出和压缩的控制逻辑,包括FEC读出控制、VME读出控制、L1计数(TriggerNumber)/复位等操作。

每个muon子事例的数据为600bytes,总数据率为2.4MB/s,可以在一个VME机箱中读出(事例率估算见后4.10.4.3)。

受VME插件面积所限,一个VME插件可能放不下所有的读出模块,则需要多个读出插件,分别压缩后,采用CBLT的方式读出。

阻性板探测器读出电子学系统的整体结构框图请参见图4.10-41。

一个前端板可以并行地读入16个感应条上的数据,并将该数据存入可串行输出的移位寄存器中。

16个前端板用菊花链的形式组成一个数据链,用LVDS信号串行地把256个感应条的位置信息传送到I/O插件后送入VME读出插件中。

数据链的数据经分别压缩后,在数据链缓冲器中暂存;

将所有数据链的压缩数据存入VME读出插件的子事例缓冲器中,等待DAQ的处理。

(每个数据链包括256道数据,系统共36-40个数据链,表示了4096+4992个感应条的位置信息;

40个数据链最多可表示10240个感应条的位置信息,组成了一个µ

子事例的数据,可以满足BESIIIRPC9088个通道的要求。

)

当测试命令传送到VME的测试信号发生器(在系统控制插件中)时,测试信号发生器将其转换为串行的DAC控制时序并通过I/O插件送到FEC中,对FEC中控制TEST信号的DAC进行设置,产生与测试命令相对应的测试模拟信号。

测试信号被加载到每个通道的比较器的输入端,测试通道电路的好坏。

JTAG控制插件负责从VMEBUS接收FEC的FPGA配置命令,并转换为JTAG控制时序,驱动后送到FEC;

FEC采用串行配置方式,每个JTAG控制接口负责4个FEC的JTAG配置,总共需要40×

4个JTAG控制接口(14个插件)。

图4.10-41阻性板探测器读出电子学系统整体结构示意图

甄别阈设置电路的方法与上述测试方法相似。

甄别阈设置命令将由甄别阈控制器发出,经前端板的DAC变换后,形成相应的电平,加载到比较器的甄别阈设置端,达到设置甄别阈的目的。

4.10.4.3

数据读出部分的电路

1.前端读出板电路(FEC)

前端读出板电路的任务是并行读出阻性板探测器感应条上的信号,并保存6.4μS的时间,等待触发信号的出现。

在6.4μS时,如果有触发信号出现,则表示该保存的信号是好事例数据,该数据将传送到的VME读出插件中去;

如果没有触发信号到来,则清除该保存的信号,再次等待阻性板探测器感应条的信号。

当感应条信号又一次到来时,则再次保存该信号,等待触发信号的出现。

前端板电路安装在探测器的内部。

前端读出板电路的原理框图请参见图4.10-42。

RPC探测器感应条的模拟信号,由双绞线扁平电缆并行引出,并加载到前端板的甄别器(比较器)的信号输入端。

信号经甄别器甄别后,变为数字逻辑信号。

16个通道的数据,存放在FPGA中的FIFO中,等待触发信号的出现。

当触发信号出现时,数据由FPGA中的移位寄存器串行成一个16位的数据流,以便和上一块16个通道的前端板链接。

在FPGA芯片中,还使用了一个16个输入的”或”门,在触发信号出现时,将该“或”门的输出作为FASTOR信号提供给触发系统使用,以便快速地判断μ子的情况(图中未画出)。

FPGA芯片的逻辑示意图请参见图4.10-43。

图4.10-42前端板电路框图

图4.10-43前端板FPGA逻辑示意图

由图4.10-43可知,我们在FPGA中使用了流水线的技术,避免了系统的死时间。

FPGA芯片中共设置了两级缓冲器。

第一级缓冲器(FIFO)作流水线工作的缓冲器使用,其深度应该等于触发延迟时间内到达数据的个数和触发信号向后晃动的时间内到达数据个数之和。

因为LVDS数据经18m传输线传输至VME读出插件的链数据缓冲器所需要较长的时间,为避免在此传输过程中再次出现触发信号而导致数据的丢失,所以在FPGA中设置了第二级缓冲器。

关于第二级缓冲器深度设置及其对系统死时间影响的估算,请参见“附录一缓冲器深度的估算”的章节。

RPC经常会因为束流损失或其它原因而产生大的放电,造成FEC线路或其中的元件损坏,特别是FPGA芯片会由于这种放电而功能失效;

同时,FPGA放置在探测器的内部,也可能由于辐射的影响,产生某些逻辑功能的失效。

为防止这种情况的产生,在VME前端板中,加入了大电荷保护。

当发现FPGA功能失效时,立即重载FPGA的源码,以避免数据的丢失。

2.VME读出插件

在FEC的数据被传送到远端的VME读出插件时,首先进行事例数据压缩,存入链数据缓冲器。

一个VME读出插件共有40个链(最大数据缓冲器,可以并行地接受40数据链的数据输入。

在每个数据链的数据传送完毕后,40个链数据缓冲器的数据将转存到子事例缓冲器中,同时加入触发号和运行号等数据头信息,等待DAQ的读入。

图4.10-44VME读出插件方框图

一个VME读出插件的框图如图4.10-44所示。

图中的联动开关是为测试设置的。

当联动开关置于“取数”挡时,数据经压缩后存入数据链事例缓冲器;

当联动开关置于“测试”挡时,数据经串并转换后存入数据链事例缓冲器。

事实上,此处的联动开关可以使用多路器来实现。

1)数据量的估算和事例压缩格式

μ子鉴别器的阻性板探测器是一个低事例占有率的探测器。

根据Babar实验μ子鉴别的阻性板探测器给出的每次事例也仅有几十道被击中[1]的数据,可以估算BESIIIμ子鉴别器的数据量。

所谓按前端读出板的压缩方法,事实上是只要某一块前端读出板上任何一道有数据,就把该前端读出板上的数据全部存储起来。

由图4.10-45可知,625前端读出板(16通道×

625=10,000通道)的地址可用10位编码来表示,前端读出板上的16个通道的数据可用16位数据码来表示。

图4.10-45两种数据压缩格式

零压缩的方法则是去掉数据中的数据0,仅留下数据1,并把该数据地址存储起来。

在这种压缩方法中,前端读出板的地址为10位编码,板上16个通道的地址编码为4位,2位备用,共用16位地址编码来表示一个数据。

设BESIII阻性板探测器一个事例最大的数据量为100个阻性板探测器被击中;

设每个被击中的阻性板探测器有5个感应条上有感应信号输出。

由于按前端读出板压缩的方法是连续的数据都被记录在一个板的数据位上,所以100个被击中的阻性板探测器,只要按被击中阻性板探测器的数量来计算其数据总量即可。

设被100个被击中的阻性板探测器中,有50个阻性板探测器的感应条信号只出现在一个前端读出板中,另50个则在两个读出板之间。

对于前者,由于其感应条信号只出现在1块前端读出板上,所以只要用1个前端读出板的地址来记录其压缩的数据即可,其数据量为:

50×

4bytes=200bytes

而对于后者,则必须用2个读出板的地址来表示其压缩的数据,其数据量为:

50×

4bytes×

2=400bytes

按前端读出板的压缩方法表示的100个阻性板探测器的数据总量为600bytes。

按好事例触发率4kHz来计算,按前端读出板方法压缩方法的数据速率为2.4Mbytes/秒。

如果按每道平均击中的概率相同来计算,一个VME读出插件(2048道)的数据量为:

(0.6kbyte/event÷

10,000)×

2048≈123bytes/event

由于按0压缩的方法表示的数据是按1数据的地址来存储的,所以200个被击中阻性板探测器感应条的数量应为:

200×

5=1000条

数据总量为

2bytes×

500=1Kbytes

(1kbytes/event÷

2048≈204.8bytes/event

0数据压缩方法的数据速率约为按前端读出板压缩方法数据速率的2倍。

本方案使用按前端读出板压缩的方法来压缩数据。

2)链数据缓冲器深度估算

按以上估算,图4.10-44中的一个链数据缓冲器(ChainDataBuffer)中的数据量为:

123byte/event÷

16≈8byte/event

事实上,由于使用了按板压缩的方法,一个数据即为4个字节(32位),此处使用的是4字节为一个单元,共2个单元组织成一个组(bank)。

为保证数据读出和写入的操作不对系统死时间作贡献,即防止在数据从数据链缓冲器导入到子事例缓冲器的时间内,再来触发信号时丢失好事例数据,此处的链数据缓冲器的深度为6个组(bank),即2×

4byte为1组(bank),共设置6组。

在这种设置的情况下,在4kHz触发速率的条件下,运行8小时仅损失1.97个事例。

这种损失可以忽略不计。

链数据缓冲器深度设置的估算请参见“附录一—缓冲器深度的估算”。

3)子事例缓冲器深度