八位七段数码管动态显示电路设计Word格式.docx

《八位七段数码管动态显示电路设计Word格式.docx》由会员分享,可在线阅读,更多相关《八位七段数码管动态显示电路设计Word格式.docx(14页珍藏版)》请在冰豆网上搜索。

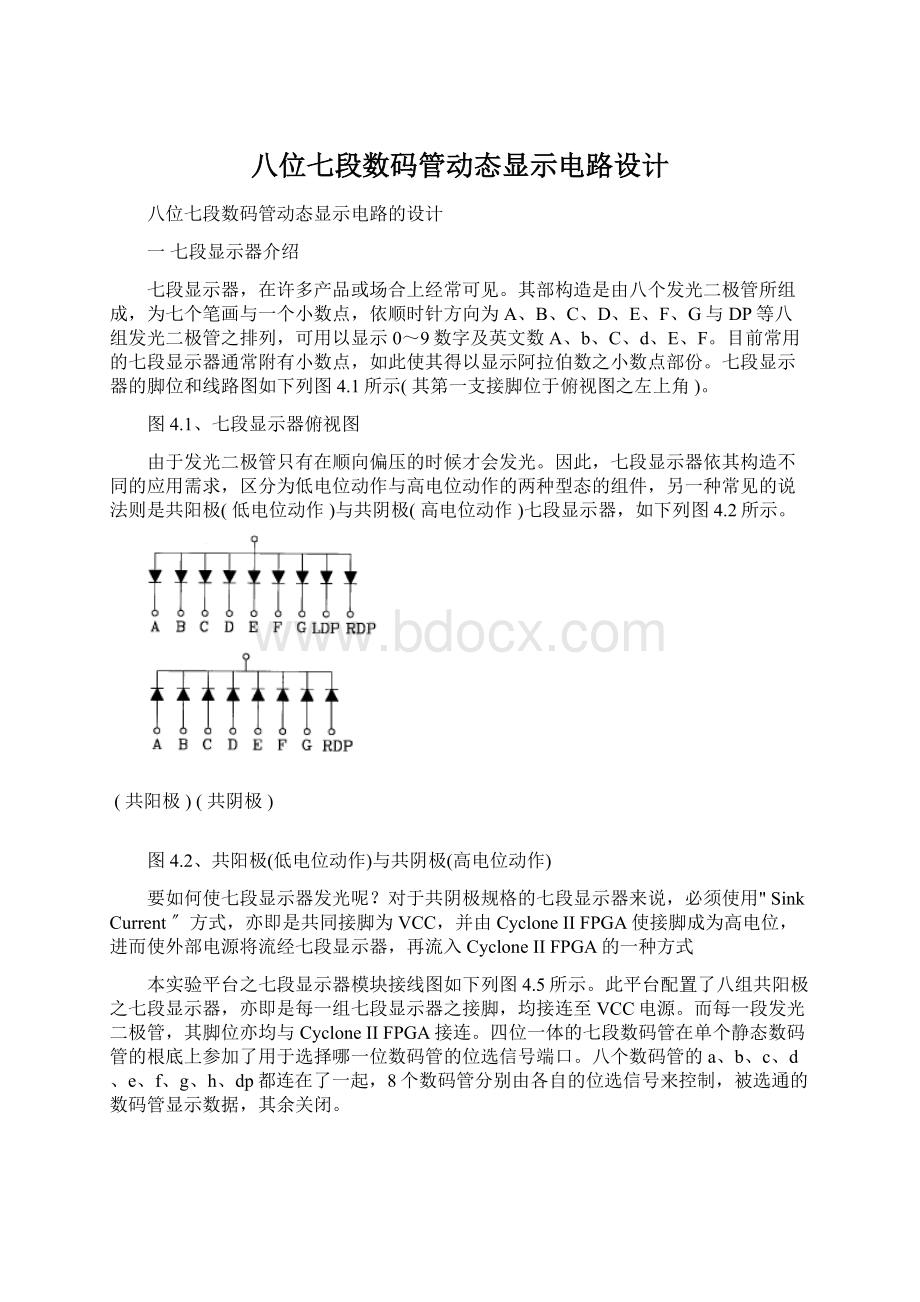

表4.1、共阳极七段显示器显示数字编码

资料

DP

G

F

E

D

C

B

A

16进制

1

C0

F9

2

A4

3

B0

4

99

5

92

6

82

7

F8

8

80

本实验要求完成的任务是在时钟信号的作用下,通过输入的键值在数码管上显示相应的键值。

在实验中时,数字时钟选择1KHZ作为扫描时钟,用四个拨动开关做为输入,当四个拨动开关置为一个二进制数时,在数码管上显示其十六进制的值。

实验箱中的拨动开关与FPGA的接口电路,以及拨动开关FPGA的管脚连接在实验一中都做了详细说明,这里不在赘述。

数码管显示模块的电路原理如图4-2所示,

图4-2数字时钟信号模块电路原理

三实验步骤

〔本实验用VHDL文本语言实现八位七段数码管动态显示,当然也可用Quartus的图形输入法实现八位七段数码管动态显示〕

1.下面我们建立一个八位七段数码管动态显示的VHDL工程

1)选择开场>

程序>

Altera>

QuartusII5.1,运行QUARTUSII软件。

或者双击桌面上的QUARTUSII的图标运行QUARTUSII软件,出现如图1-3所示。

图1-3QUARTUSII软件运行界面

2)选择软件中的菜单File>

NewProjectWizard,新建一个工程。

如图1-4所示。

图1-4新建工程对话框

3〕点击图1-4中的NE*T进入工作目录,工程名的设定对话框如图1-5所示。

第一个输入框为工程目录输入框,用户可以输入如e:

/eda等工作路径来设定工程的目录,设定好后,所有的生成文件将放入这个工作目录。

第二个输入框为工程名称输入框,第三个输入框为顶层实体名称输入框。

用户可以设定如E*P1,一般情况下工程名称与实体名称一样。

使用者也可以根据自已的实际情况来设定工程名和顶层文件名。

注:

本处的顶层文件名必须和程序的实体名一致,否则编译会出错。

图1-5指定工程名称及工作目录

4〕点击NE*T,进入下一个设定对话框,按默认选项直接点击NE*T进展器件选择对话框。

如图1-6所示。

这里我们以选用CycloneII系列芯片EP2C35F672C8为例进展介绍。

用户可以根据使用的不同芯片来进展设定。

图1-6器件选择界面

首先在对话框的左上方的Family下拉菜单中选取CycloneII,在中间右边的Speedgrade下拉菜单中选取8,在左下方的Availabledevices框中选取EP2C35F672C8,点击NE*T完成器件的选取,进入EDATOOL设定界面如图1-7所示。

图1-7EDATOOL对话框

5〕按默认选项,点击Ne*t出现新建工程以前所有的设定信息,如图1-8所示,点击Finish完成新建工程的建立。

图1-8新建工程信息

2、建立VHDL设计文件

1〕在创立好设计工程后,选择File>

NEW…菜单,出现图1-9所示的新建立计文件类型选择窗口。

这里我们以建立VHDL设计文件为例进展说明。

图1-9新建立计文件选择窗口

2〕在New对话框〔图1-9〕中选择DeviceDesignFiles页下的VHDLFile,点击OK按钮,翻开图形编辑器对话框,如图1-10所示。

图中标明了常用的每个按钮的功能

3〕在文本编辑器中输入如下VHDL程序:

--下面是引用库-------------------------------------

libraryieee;

--库函数

useieee.std_logic_1164.all;

--定义了std_logic数据类型及相应运算

useieee.std_logic_arith.all;

--定义了signed和unsigned数据类型、相应运算和相关类型转换函数

useieee.std_logic_unsigned.all;

--定义了一些函数,可以使std_logic_vector类

--型被当作符号数或无符号数一样进展运算

--------------------------------------------------------------------

--下面是构造实体

entitye*p4is--e*p4为实体名

port(clk:

instd_logic;

--定义动态扫描时钟信号

key:

instd_logic_vector(3downto0);

--定义四位输入信号

ledag:

outstd_logic_vector(6downto0);

--定义七位输出信号

del:

outstd_logic_vector(2downto0)--定义八位数码管位置显示信号

);

ende*p4;

--完毕实体

architecturewhbkrcofe*p4is--whbkrc为构造体名

begin--以begin为标志开场构造体的描述

process(clk)--进程,clk变化时启动进程

variabledount:

std_logic_vector(2downto0);

--变量,计数

begin

ifclk'

eventandclk='

1'

then--检测时钟上升沿

dount:

=dount+1;

--计数器dount累加

endif;

del<

=dount;

--片选信号

endprocess;

--完毕进程

process(key)--进程,key变化时启动进程

casekeyis

when"

0000"

=>

ledag<

="

0111111"

;

--七段数码管显示0

0001"

0000110"

--1

0010"

1011011"

--2

0011"

1001111"

--3

0100"

1100110"

--4

0101"

1101101"

--5

0110"

1111101"

--6

0111"

0000111"

--7

1000"

1111111"

--8

1001"

1101111"

--9

1010"

1110111"

--R

1011"

1111100"

--b

1100"

0111001"

--C

1101"

1011110"

--d

1110"

1111001"

--E

1111"

1110001"

--F

whenothers=>

null;

endcase;

--完毕进程

endwhbkrc;

--完毕构造体

关于VHDL,我们以上面八位七段数码管显示程序为例来解释VHDL的语法构成,以使大家对VHDL有个整体的把握。

一个VHDL程序有三局部构成,其为:

1.库和包library〔设计资源〕;

2.实体entity〔外部端口〕

3.构造体architecture〔部构造〕

①库和包library〔设计资源〕的介绍

1.1useieee.std_logic_1164.all;

1.2useieee.std_logic_arith.all;

--定义了signed和unsigned数据类型、相应运算

--和相关类型转换函数

1.3useieee.std_logic_unsigned.all;

--定义了一些函数,可以使std_logic_vector

--类型被当作符号数或无符号数一样进展运算

本程序中用到3个库函数包:

如下:

补充:

当使用库时,需要说明使用的库名称,同时需要说明库中包集合的名称及围;

每个实体都应独立进展库的说明;

库的说明应该在实体之前;

经过说明后,实体和构造体就可以自动调用库中的资源;

②实体entity〔外部端口〕

outstd_logic_vector(2downto0)--定义八位数码管位置显示信

实体说明主要描述对象的外貌,即对象的输入和输出〔I/O〕的端口信息,它并不描述器件的具体功能。

在电路原理图上实体相当于元件符号。

CLKdel(2…0)

Key〔3..0〕ledag(7…0)

图4-9

实体e*p4中描述如上图4-9输入和输出〔I/O〕的端口信息

③构造体architecture〔部构造〕

构造体具体指明了该设计实体的行为,定义了该设计实体的功能,规定了该设计实体的数据流程,指派了实体中部元件的连接关系。

4〕点击保存按钮,弹出如下选项,将其名命名为e*p1,如下列图

5〕对设计文件进展编译

QUARTUSII编译器窗口包含了对设计文件处理的全过程。

在QUARTUSII软件中选择processin>

startpilation菜单项,就会自动编译,出现QUARTUSII的编译器窗口,如下列图所示

如果文件有错,在软件的下方则会提示错误的原因和位置,以便于使用者进展修改直到设计文件无错。

整个编译完成,软件会提示编译成功,

3管脚分配

在前面选择好一个适宜的目标器件〔在这个实验中选择为EP2C35F672C8〕,完成设计的分析综合过程,得到工程的数据文件以后,需要对设计中的输入、输出引脚指定到具体的器件管脚,指定管脚称为管脚分配或管脚锁定。

这里介绍两种方法进展管脚锁定。

1〕点击Assignments菜单下面的AssignmentEditor,进入到引脚分配窗口。

如图1-15所示。

图1-15进入引脚分配界面

首先将要分配管脚的信号放置在To下方。

双击To下方的"

New"

,如图1-15所示则会出现如图1-16所示界面。

图1-16信号选择对话框

选择NodeFinder…进入如图1-17所示的NodeFinder对话框界面。

按图1-17中样例设置参数。

在Filter窗口选择Pins:

all,在Named窗口中输入"

*〞,点击List在NodesFound窗口出现所有信号的名称,点击中间的按钮则SelectedNodes窗口下方出现被选择的端口名称。

双击OK按钮,完成设置。

进入管脚分配窗口,如图1-18所示。

图1-17NodeFinder对话框

图1-18管脚分配

在图1-18中以锁定端口key[0]的管脚为例,其它端口的管脚锁定与其根本一致。

选择端口key[0]的对应AssignmentName待其变为蓝色,双击之,出现下拉菜单项选择取如图1-18所示的Location〔Acceptswildcards/groups〕选项。

选择端口key[0]的对应Value栏,待其变为蓝色,依照表1-2所示的硬件与FPGA的管脚连接表〔或附录〕,输入对应的管脚名AC22,按回车键,软件将自动将其改为PIN_AC22,同时蓝色选择条会自动跳转到Value栏的下一行,这说明软件已经将输入端口key[0]分配到FPGA的AC22引脚上,如图1-19所示。

图1-19给key[0]端口进展管脚分配

用同样的方法,依照表4-2和所示的硬件与FPGA的管脚连接表〔或附录〕,对其它端口进展管脚分配,如图1-20所示。

图1-20所有引脚全局部配完毕后的软件窗口

端口名

使用模块信号

对应FPGA管脚

说明

CLK

数字信号源

N2

时钟为1KHZ

KEY0

拨动开关K1

AC22

二进制数据输入

KEY1

拨动开关K2

AD23

KEY2

拨动开关K3

AB8

KEY3

拨动开关K4

AA9

LEDAG0

数码管A段

V17

十六进制数据

输出显示

LEDAG1

数码管B段

W16

LEDAG2

数码管C段

W15

LEDAG3

数码管D段

L10

LEDAG4

数码管E段

V14

LEDAG5

数码管F段

V13

LEDAG6

数码管G段

W12

DEL0

位选DEL0

U12

DEL1

位选DEL1

V20

DEL2

位选DEL2

V21

表4-2端口管脚分配表

值得注意的是,当管脚分配完之后一定要进展再进展一次全编译,以使分配的管脚有效。

4、对设计文件进展仿真

1〕创立一个仿真波形文件,选择QUARTUSII软件File>

New,进展新建文件对话框。

如图1-24所示。

选取对话框的OtherFile标签页,从中选取VectorWaveformFile,点击OK按钮,则翻开了一个空的波形编辑器窗口,如图1-25所示。

图1-24新建文件对话框图1-25波形编辑器

2〕设置仿真完毕时间,波形编辑器默认的仿真完毕时间为1µ

S,根据仿真需要,可以自由设置仿真的完毕时间。

选择QUARTUSII软件的Edit>

EndTime命令,弹出线路束时间对话框,在Time框办输入仿真完毕时间,点击OK按钮完成设置。

3〕参加输入、输出端口,在波形编辑器窗口左边的端口名列表区点击鼠标右键,在弹出的右键菜单中选择InsertNodeorBus…命令,在弹出的InsertNodeorBus对话框如图1-26所示界面中点击NodeFinder…按钮。

图1-26InsertNodeorBus对话框

在出现的NodeFinder界面中,如图1-27所示,在Filter列表中选择Pins:

*〞,点击List在NodesFound窗口出现所有信号的名称,点击中间的

按钮则SelectedNodes窗口下方出现被选择的端口名称。

双击OK按钮,完成设置,回到图1-26所示的InsertNodeorBus对话框,双击OK按钮,所有的输入、输出端口将会在端口名列表区显示出来,如图1-28所示。

图1-27NodeFinder对话框

图1-28在波形编辑器中参加端口

4〕编辑输入端口波形,即指定输入端口的逻辑电平变化,在如图1-28所示的波形编辑窗口中,选择要输入波形的输入端口如clk端口,在端口名显示区左边的波形编辑器工具栏中有要输入的各种波形,其按钮说明如图1-29所示。

根据仿真的需要输入波形。

以添加输入端口波形clk为例来讲解如何操作:

在添加完输入,输出端口后,在每个端口的左边会出现I或者O字样,分别代表输入,输出,我们只需要添加输入端口波形,首先单击Edit--→EdnTime左边第一行输入10,第二行输入us,完毕后单击OK,完成了整个仿真时间的设置。

然后用波形编辑工具选中Clk的0到40ns后,然后单击

高电平,该段波形高电平1,用同样的方法编辑其他时段的波形和其他输入端口的波形,参照图1-30编辑输入端口波形。

输入波形的时间不能过小,最好能到达每段波形最小间隔40ns,否则很可能由于延时造成结果的不如意。

完成后如图1-30所示。

最后选择软件的File>

Save进展保存。

图1-29波形编辑器工具栏

\

图1-30编辑输入端口波形

5〕指定仿真器设置,在仿真过程中有时序仿真和功能仿真之分,在这里介绍功能仿真。

在QUARTUSII软件中选择Tool>

SimulatorTool命令,翻开仿真器工具窗口,如图1-31所示。

图1-31仿真器工具窗口

图1-31

按图1-31上的提示,首先产生功能仿真网表文件,点击产生功能仿真网表的按钮GenerateFunctionalSimulationNetlist,产生功能仿真网表,然后点击开场仿真的START按钮开场进展仿真,直到仿真进度条为100%完成仿真。

点击仿真报告窗口按钮Report,观察仿真波形。

如图1-32所示。

图1-32仿真波形

5、从设计文件到目标器件的加载

完成对器件的加载有两种形式,一种是对目标器件进展加载文件,一种是对目标器件的配置芯片进展加载。

这里我们介绍对目标器件EP2C35F672C8进展加载的方法。

1〕使用下载电缆将PC机与实验系统连接起来。

2〕选择QUARTUSII软件的Tool>

Programmer命令,进展编程器窗口,如图1-33所示,如果没有设置编程硬件,则编程硬件类型为NoHardware,需要对编程硬件进展设置。

点击HardwareSetup…编程硬件设置按钮,进展如图1-34所示的编程硬件设置对话框。

图1-33编程器窗口

图1-33

图1-34编程器硬件设置对话框

3〕点击AddHardware按钮,出现AddHardware对