TSMC工艺的版图教程范本模板Word格式.docx

《TSMC工艺的版图教程范本模板Word格式.docx》由会员分享,可在线阅读,更多相关《TSMC工艺的版图教程范本模板Word格式.docx(45页珍藏版)》请在冰豆网上搜索。

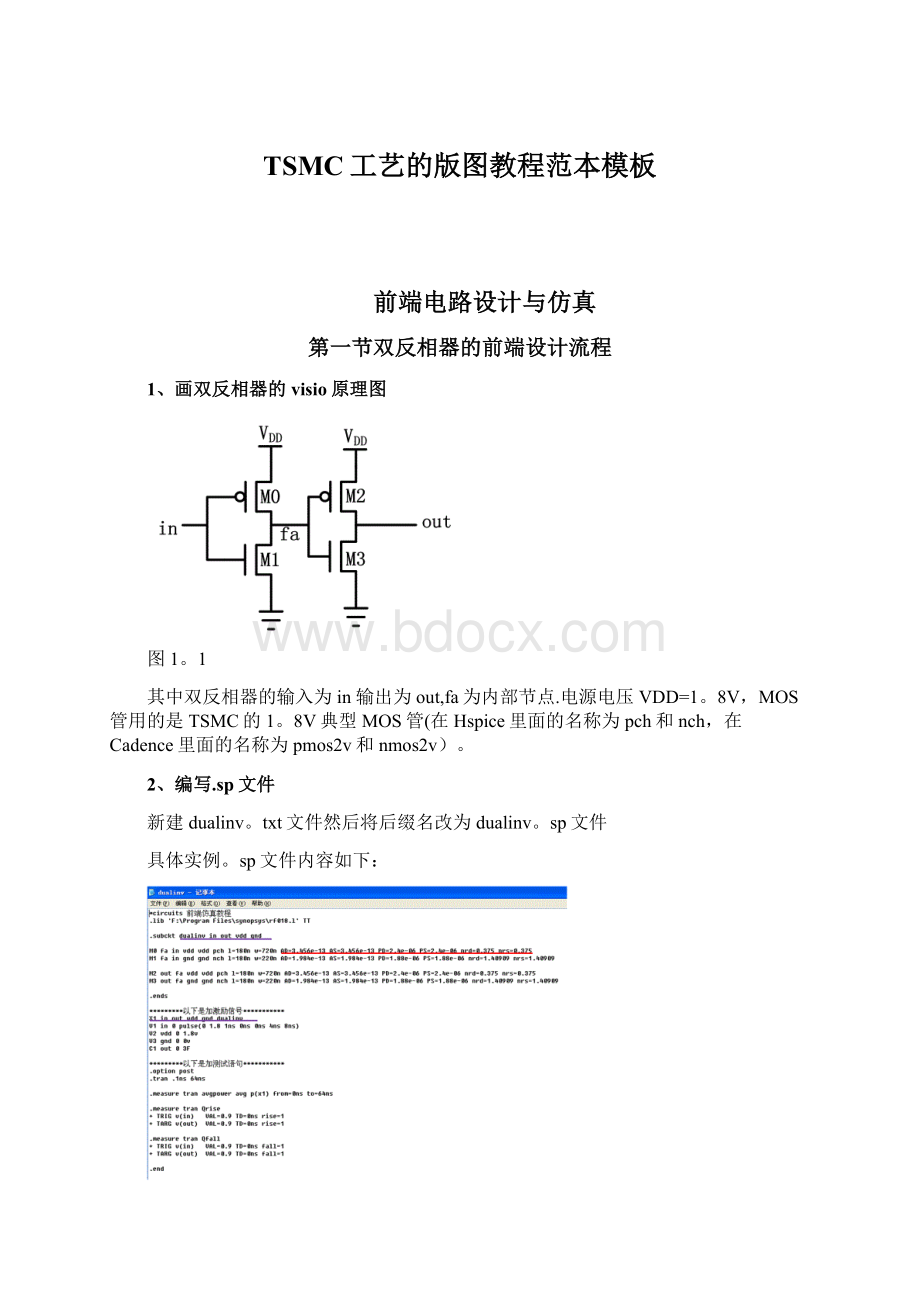

MTO文件(用记事本打开)

至此前端仿真教程结束

第二节后端电路设计

前序(打开Cadence软件)

一、开启linux系统

双击桌面虚拟机的图标

选择Poweronthisvirtualmachine

开启linux之后

在桌面右键选择OpenTerminal

输入xhostlocal:

命令按回车

之后输入suxue命令按回车,这样就进入了xue用户

1、输入命令加载calibre软件的license,按回车,等到出现以下画面再关闭Terminal窗口

2、然后桌面右键重新打开Terminal

进入学用户,开启Cadence软件,如下图

然后出现cadence软件的界面

关闭这个help窗口,剩下下面这个窗口,这样cadence软件就开启了

[如果在操作过程中关闭了cadence,只需要执行步骤2即可,步骤1加载calibre的license只在linux重启或者刚开启的时候运行一次就可以了。

]

双反相器的后端设计流程

一、schematic电路图绘制

1、注意—-—-

在Cadence中画schematic电路图时,每一个节点都需要命名,不然在参数提取之后没有命名的那些节点会被系统自动命名,导致用HSPICE查看内部节点波形时难以迅速找到自己需要的节点.

2、打开Cadence软件新建库和单元CellView

用命令icfb&打开Cadence软件后弹出以下CIW窗口

选择Flie—New-Libirary之后弹出以下窗口

这里我们新建一个名为ttest的库。

(注意:

在新建library的时候要attachtoanexistingtechfile)

点击OK以后弹出以下窗口

在technologylibrary这里选择我们的TSMC库tsmc18rf

然后点击OK

在CIW窗口的tools菜单中选择第二个librarymanager之后弹出以下窗口

我们可以看到左边Library里面有我们之间建立的ttest库,用鼠标左键选择ttest,发现它的Cell和View都是空的。

然后在该窗口的File-New—CellView新建一个单元CellView

弹出以下窗口

在窗口的Cellname中输入我们需要取的名字,这里取的是dualinv.

点击OK后自动弹出画schematic的窗口

3、画schematic电路图

点击上面的这个作图版面,在键盘上按快捷键i会出现添加器件的窗口

点击Browse后弹出以下窗口

这里选中TSMC的库tsmc18rf,在Cell中选中pmos2v,view中选中symbol

然后鼠标移到外面的画图板上,就会出现一个PMOS管,左键点击就可以放上去了,按ESC回到正常的光标状态。

同理,选中TSMC库中的nmos2v,就可以添加NMOS管。

(按快捷键M,然后再点击一下(选中)器件即可以移动器件)

接下来修改MOS管的尺寸,我们看到上述MOS管的默认尺寸都是L=180nW=2u

我们这里将PMOS管修改为W=720nNMOS管修改为W=220n

TSMC0。

18um库nmos2v和pmos2v最小的W只能设置到220nm,而不能设置到180nm)

鼠标左键选中一个器件(如M0),然后按快捷键Q(property),出现以下调整MOS管属性窗口

在w(M)的文本框中修改前面的2u修改成我们需要的720n然后点击OK即可

同理修改NMOS管的W=220n。

之后开始连线按快捷键W(wire)即可

然后添加PIN脚(即与外部信号相连的端口,从图1。

1可以看出这个双反相器电路涉及到的PIN脚有inoutvddgnd)

[注意:

由于目前的工艺是P阱衬底,所以全部NMOS管的衬底即B端要接gnd,而PMOS管的衬底可以接自己的S端或者vdd,一般只接VDD不接S]

[知识补充:

MOS管的衬底B端接S才能不引起衬偏,衬偏了会造成阈值电压增大]

按快捷键P就可以添加PIN脚

在pinname中输入名称Direction中选中pin脚的方向(其中in的direction是inputout的direction是outputgnd和vdd的direction是inputoutput)

然后按回车,光标上就会出现一个pin的光影,点击鼠标左键即可摆放

摆放pin脚之后,将PIN脚与电路相连,同样用快捷键W来连线

由于图1。

1中还有一个内部节点fa,这里我们就需要给内部节点命名.按快捷键L,出现命名窗口

在names这里输入fa,然后按回车

然后鼠标上出现fa光影,将fa移到内部需要命名的线上点击左键即可。

然后保存电路

通用,也可以用快捷键L来连接两个单元:

[这样就不用连线,却能保证两个单元连接到一起.]

在画图板左边工具栏里面选中第一个checkandsave

4、将电路图创建成为一个symbol,用于仿真电路

选择Design—CreateCellview-FromCellview弹出以下窗口

点击OK弹出以下窗口

这里主要是TopPins和BottonPins这里需要修改,修改成如下图

点击OK弹出以下电路

点击save按钮保存

这样我们就会看到在librarymanager里面就多出了一个该电路的symbol

5、用spectre仿真器仿真电路

(这里仿真一下电路主要是验证一下自己电路有没有画错,如果电路逻辑功能正确,那么基本上可以保证自己刚才画的电路是正确的)

新建一个名为dualtest的CellView单元(在LibraryManager下)

点击OK

按快捷键i添加我们之前给双反相器电路创建的symbol

然后出现下图

接下来就要给各个端口加激励信号和电源了

按I添加器件,在analoglib中首先选择直流电压Vdc,另外还要选择vpwl作为线性分段信号源。

按Q修改vdc的属性

在DCvoltage这里将电压值设置为1.8v(注意,只要填入1.8即可,不要带入单位)

同样修改vpwl的属性(这里我们设置一个3段线性信号,即6个点),如下图

此外我们还要添加一个gnd器件作为基准地信号(在analoglib中选择)

添加完器件之后如下图

电路的gnd与标准地gnd之间要添加一个0V的直流电压)

接下来连线以及给输出端添加一个PIN,如下图

然后按checkandsave保存

选择tools中的Analogenvironment

选择右边工具框中的第二个

弹出以下窗口

这里设置仿真的停止时间(该时间根据自己具体需要填写),然后点OK

接下来设置需要看波形的那些端口outputs-ToBePlotted—SelectOnSchematic

然后在要看波形的线条上单击鼠标左键点一下即可

点完之后该线条会变颜色以及闪烁,之前的Analogenvironment窗口的outputs中也会出现相应的名称

然后点击右边工具栏中得倒数第三个NetlistandRun

电路正确的话就会有波形

点击该图标是分离重叠的波形

-—-———其他快捷键—--——————-

E看symol里面的电路

Ctrl+E退出看内部电路

F让原理图居中

PPIN管脚快捷键

W连线

L命名连线

C复制

Q器件属性

M移动

U撤销

其他相关设置:

设置回退次数CIW窗口—-options——userpreference

多个器件属性一起修改,用shift选中以后然后选allselected(原先是onlycurrent)

二、版图设计

打开dualinv的schematic电路图,然后Tools——DesignSynthesis——LayoutXL

之后弹出以下对话框

点击OK后弹出

点击OK就会自动弹出画layout的版面

此时键盘上按E键,出现设置窗口

这里修改分辨率,将XSnapSpacing和YSnapSpacing修改为0。

005,方便之后的画图。

在画layout版面的菜单中选择Design——GenFromsource

然后弹出以下窗口

点击OK即可,版面上就生成与原schematic电路图相对于尺寸的MOS管,如下图

[注:

可以不genfromsource而直接在画版图的版面按快捷键I添加layout器件,再修改尺寸,这样也可以通过LVS(经过测试即使版图中MOS的编号和schematic中的不同,但是最终输出子电路中MOS管编号跟schematic是相同的)]

选择那四个绿色的方框和紫色的线,按delete删除,删除后就剩下四个MOS管。

按shift+F将MOS管转换为可视的layout结构,并用M快捷键来移动MOS管,此时整个版面上就剩下四个MOS管了,(Ctrl+F可以还原为Schematic结构)如下图

工具栏左边的放大镜可以放大和缩小,或者使用快捷键Z(放大),shift+z缩小

(按了Z键要选某一个区域才能放大,不是直接放大与缩小)

接下来开始画图:

1、画PMOS管和NMOS管相连的栅极(用LSW窗口中得POLY1来画)

选中POLY1drw然后点版图,然后按R(画方框),Q属性可以看到是dg

(在空白处)按S键,鼠标移到矩形框的边,就能修改矩形框。

修改之后让矩形框与PMOS管NMOS管的栅极对齐。

(一定要对齐,不然DRC报错)

放大可以看到他们是否对齐,

这样的是对齐的。

这样就是没对齐.

画好POLY1以后如下图

2、画金属走线

由于该电路简单,只需要一层金属即可,所以只需要LSW中的metal1

在LSW中选中METAL1drw,然后点版图,然后按P(走线),然后按F3(设置线宽为0.5),Q属性可以看到是dg

画完后如下图(注意金属要整个覆盖住MOS管的D端,接触面积大才能保证电流)

3、画POLY1和metal1之间的连接

[不同材料之间相连要打孔。

比如Metal1和poly1相连,就选M1_POLY1,Metal1和Metal2相连就选M2_M1,NMOS的衬底接触和体相连用M1_SUB,PMOS管的衬底接触和体相连用M1_NWELL]

LSW中选中poly1—drw,按P,按F3,设置为0.5宽度,画一段poly

然后在这段poly上打孔,按字母O键,弹出以下窗口

在ContactType这里选择M1_POLY1,Rows这里输入2,然后回车

(鼠标右键可以旋转器件)

将这个通孔放于之前的poly1上

然后metal1与这个通孔相连即实现了金属1层与poly1之间的连接

接下来输入信号in这里也要这样画,画好之后的整体图如下

4、画衬底接触

这里要分别画PMOS管的衬底接触和NMOS管的衬底接触。

按快捷键字母O,在ContactType这里选择M1_SUB,这个是NMOS管的衬底接触。

按快捷键字母O,在ContactType这里选择M1_NWELL,这个是PMOS管的衬底接触。

5、给PMOS管打阱

[因为现在是P阱工艺,整个画图的版面就是一个P型衬底,而NMOS管是做在P型衬底上面的,所以画NMOS管的时不需要画阱,而画PMOS管时要画nwell(即它的衬底),nwell要包围住PMOS管和它的衬底接触。

]

在LSW中选中NWELL—drw,按R,画矩形框,如下图

6、画管脚PIN

在LSW中选中metal1pin

接着点击空白处,然后按快捷键L弹出以下窗口

在Label这里输入名称(注意这个名称要与schematic图中节点的名称要相同),Height这里设置字体的高度,Font这里设置字体的样式,然后按回车,将PIN脚摆放到正确位置

7、补全其它连线

因为上图并不完整,还有很多连线没有连.[在熟悉版图画法之后这一步是放在前面做的,因为我们熟悉画法后就知道哪里是VDD、gnd、输入和输出]

画完这个7步骤以后点左边工具栏的SAVE保存,然后就可以进行后面的DRC、LVS和PEX了。

补充知识-—多层金属连线:

(以下讲解两层金属metal1和metal2的布线)

由于金属走线经常会交叉,所以单层金属是不够的,这就涉及到多层金属的布线.

metal2drw是金属层2

metal1和metal2之间用通孔M2_M1

——-————————-—-———-————————-—--————

画版图一些技巧:

1、所有的MOS管最好同方向(竖方向),不要有有横有竖.最好是PMOS管放一起(比如一起放上面),NMOS管放一起(一起放下面),不一定是按照schematic电路图上的MOS管顺序来摆放。

2、走线不要穿过MOS管,要绕过去。

3、单排衬底接触最长不要超过100um,比较敏感的管子要多加些接触(两排或多排),衬底接触少了电阻会大.一般情况我们采用单排衬底(即rows或columns=1)

4、横线用金属2,竖线用金属1,金属越宽电阻越小.我们一般取0.5u宽度。

[寄生电容与发生寄生电容的两导体面积成正比,因此线宽就0.5u够了(能承受1mA),不需要再大。

(TED)]

5、版图的PMOS管和NMOS管源极和漏极是不区分的,上下的poly1都是栅极.

6、衬底接触一般在下面画一排接触即可,对于数模混合电路某个MOS管是特别敏感的那用衬底全包围。

7、走线尽可能短,尽量画的紧凑,减少延时。

8、尽量不用POLY来走线,如果两个栅极之间具体太长,中间用金属走线。

poly的长度最多是3-5um.

9、同一层Metal之间的距离要大于最小值0。

23um,一般是设置成大于0.5um。

比如两条metal1走线之间的距离要大于0。

5um.

10、PMOS管的衬底全部接VDD,NMOS管的衬底全部接地

各种器件之间的距离:

1、PMOS管和NMOS管之间的距离一般控制在1um以上,太近DRC报错

2、两个不同电压nwell之间的距离要大于1。

4u,因此一开始要预留5um

3、Nwell和NMOS管之间的距离推荐是大于1u

4、Nwell和衬底接触以及PMOS管的距离0.5u左右

5、衬底接触和mos管距离一般设置为0。

5u

电容和电阻器件不选择analoglib里面的cap和res(这两个是理想电容电阻),电容一般选择tsmc里面的mimcap,电阻则要看电阻率等具体要求。

(TED&黄)

-————————-—-—-——————-——--—-—————

快捷键

K尺寸距离(shift+k撤销尺寸)

S修整

M移动选上后右键可旋转

Z放大(ctrl+z放大两倍,shift+z缩小两倍)

Shift选择多个器件

Shift+F显示NMOS和PMOS器件的版图

O打孔(pmos管衬底属性选择M1_NWELLnmos管选择M1_SUB金属和poly打孔属性选择M1_POLY1)

三、后端验证和提取

后端仿真首先要DRC,然后LVS,然后PEX提取寄生参数。

最后用Hspice仿真器仿真提取参数后的网表。

这里主要用到的是calibre工具

1、DRC

(上面工具栏中calibre—选择RunDRC)弹出下面窗口

RunsetFile是RUNDRC时需要填入的一些设置,方便于下次RUN,可直接取消掉

DRC主要设置rules的位置和DCRRun的路径[其余的都默认]

Rules这里选择TSMC库文件中calibre文件下的calibre。

drc

(这里的DRCRunDirectory是自己创建的一个文件夹,suxue~cd/home/xue~mkdirdrc)[这里dcr改为verify/dcr]

然后点击RunDRC弹出以下窗口

(运行完成之后的弹出的窗口)

点开看,如果是areacoverage那就是覆盖率的问题,这种错误不用理会。

[比如上图中得这8个错误是没关系的]

2、RunLVS

同样RunsetFile点取消

设置rules和input的netlist

【新】[lvs改为verify/lvs]

Inputs—Netlist这里选择Exportfromschematicviewer

点击runLVS后弹出以下窗口

如果是绿色笑脸则表示LVS通过,表示版图和schematic原理图是匹配的,说明我们的版图没有画错。

如果是红色脸蛋,表示有错误,那要点开看具体的错误说明,再排除错误.

3、RunPEX

Rules设置

[新]/home/gengliang/ic/verify/pex

Inputs——netlist设置Exportfromschematicview选上

Outputs—extractiontype选择R+C(即提取寄生电阻和电容),format这里选择hspice(用于Hspice仿真器仿真)

(如果后仿是用spectre仿真器仿真,那么format这里选择CALIBREVIEW)

[NEW]

Outputs-reports这里选上generatePEXreport和ViewreportafterPEXfinishes

[NEW]

然后runPEX

之后在/home/xue/pex文件夹下面生成三个我们需要用到的文件

dualinv。

pex。

netlist(里面是电路的网表)

list.pex(里面是各个节点的寄生参数)

dualinv.pex。

netlist。

DUALINV。

pxi(里面是一些调用子电路的命令)

在XP系统下用写字板打开可查看这三个文件的内容]

MOS场效应晶体管描述语句:

(pex输出的网表格式)

MMXDGSBMNAME〈L=val〉〈W=val>

PD=val>

〈PS=val〉〈NRD=val〉<

NRS=val>

第三节后端仿真

1、用Hspice仿真器进行后仿真

将上述三个文件复制到XP系统下面,然后新建一个dualinv.sp文件(即新建文本文档,后缀改成.sp),这样同一目录下就有四个文件,如下

将list文件中的电路复制到dualinv。

sp文件中(即蓝色框内这部分)

list文件里面那两行include"

pex"

和include"

DUALINV.pxi"

千万不要忘记复制过来.]

第一行一定要加一个“*”符号。

然后在dualinv.sp中加激励信号以及一些测试语句即可以仿真,如下

(这是dualinv.sp文件)

Hspice不区分字母大小写]

接下来用Hspice仿真器仿真这个dualinv.sp文件,然后看输出波形,看功耗延时参数,这些就已经是后端仿真的参数了。

[Attention]

1.1初始值要根据实际条件修改。

1.2

如下图:

.subcktlcff后边是lcff的端口,并不一定与前仿时自己编写的端口顺序一致,所以需要重新根据下文测试代码的顺序做相应的改变,否则会出错。

切记!

!

!

2、不同工艺角(corners)的仿真

CMOS电路在生产在存在工艺偏差,一般在四个工艺角(SS、FF、FS、SF)下对电路进行仿真。

具体操作如下:

在.sp文件加载模型这里改成相应的corner即可

3、蒙特卡罗法(Monte—Carlo)分析PVT对触发器的影响

一般的VT组合分为以下三种:

—40C2.0V;

25C1。

8V;

125C1。

6V(即电压偏差值在正负10%)

蒙特卡罗法(Monte—Carlo)分析PVT就是取不同的电压和温度组合,然后进行Monte-Carlo分析,MC分析就是随机选取器件的参数。

【要进行Monte-Carlo分析首先工艺厂商提供的仿真模型(rf018.l文件)要支持Monte—Carlo分析,即里面要有MC模型。

】具体操作如下:

温度、输入电压要变化,然后加上Monte—Coral分析。

注意红色横线部分

************************************************************

到此为止,整个后端仿真的流程演示完毕,当然这里面还有很多是不够细致的,主要是画版图这一块。

画版图是一个经验积累的过程,我上面演示的只是一个很简单的例子,这还需要大家在学习中不断积累经验。

************************************************************

其它知识

(用spectre仿真器的需要看以下步骤,用Hspice仿真器不需要看)

——————————用spectre仿真器仿真-—————

(如果format这里选择的是CALIBREVIEW)运行后弹出

直接点OK

以下是第一次运行的配置

前面是pch和nch的配置

点automappins然后点OK

电容和电阻分别选择analoglib中的cap和res

用spectre后仿真

[一定要注意,schematic和