EDA实验设计报告Word文档格式.docx

《EDA实验设计报告Word文档格式.docx》由会员分享,可在线阅读,更多相关《EDA实验设计报告Word文档格式.docx(14页珍藏版)》请在冰豆网上搜索。

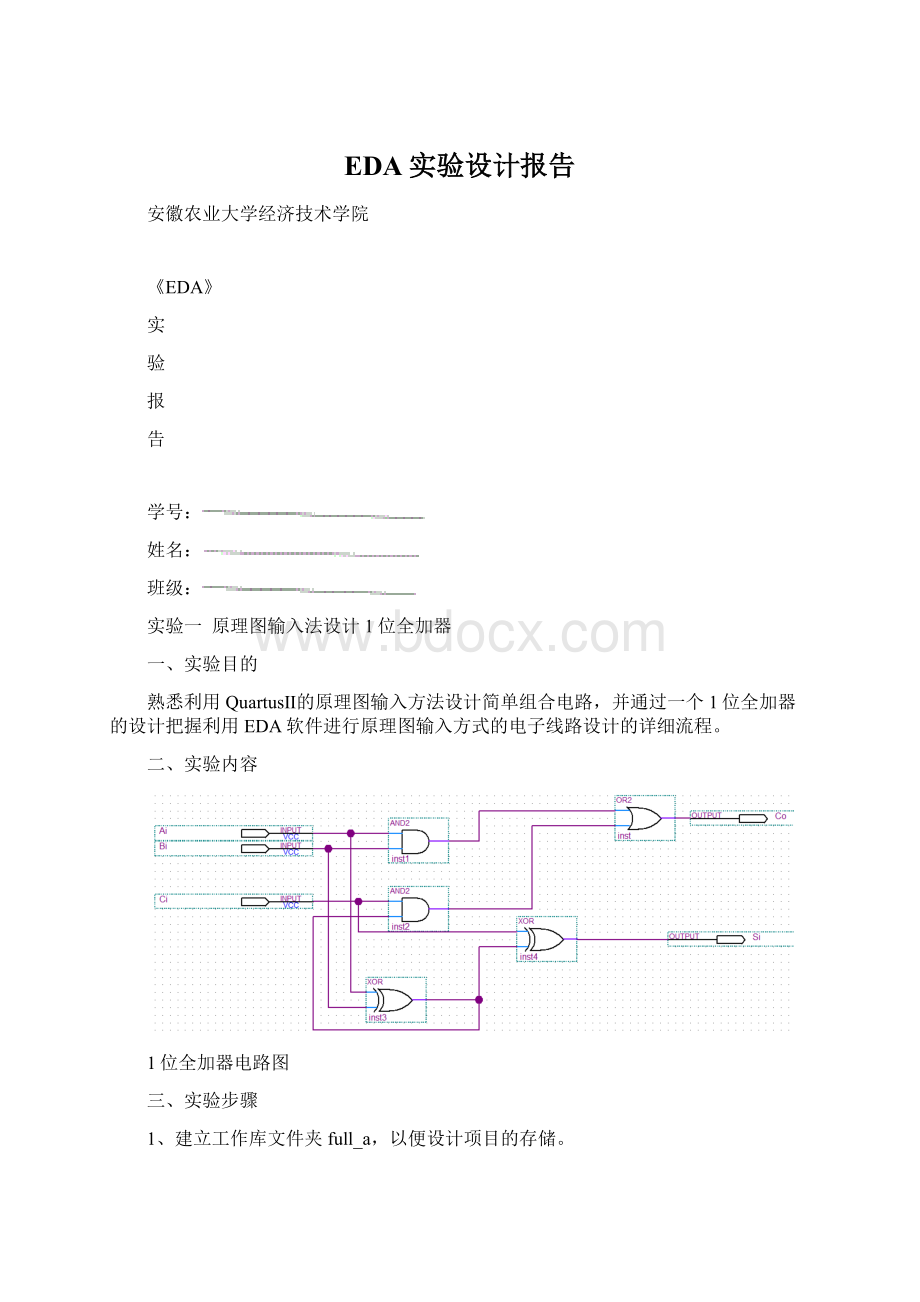

设置仿真输入信号,存盘。

7、仿真测试。

打开Processing→startsimulation开始仿真并分析结果。

四、实验结果

五、结果分析

输入

输出

CI

AI

BI

SI

CO

1

六、实验心得

通过这次实验让我学会了很多,而且在课上老师得到老师很多的帮助,这也让我对QuartusⅡ软件有了很大的认识,虽然在课上学习的时间很少但是只要自己注意一些细节,总会得到一些小小的提升,然而这样一点点的积累总会让我们能成长。

实验二四选一多路选择器的设计

1、了解VHDL进行EDA设计的基本步骤;

2、学会用QuartusⅡ进行仿真。

编写VHDL程序描述一个电路,实现以下功能:

具有5个输入端口D0、D1、D2、D3、SEL,D0、D1、D2、D3均为输入端口,位宽为1;

SEL为通道选择控制信号端,位宽为2;

Y为输出端口,位宽为1。

当SEL为“00”时,D0的数据从Y输出,SEL为“01”时,D1的数据从Y输出,SEL为“10”时,D2的数据从Y输出,SEL为“11”时,D3的数据从Y输出。

1、建立文件夹,以便设计项目的存储。

在New窗口中的DesignFiles中选择设计文件类型为VHDLFile,单击OK后进入QuartusⅡ文本编辑窗,根据要求编写VHDL程序。

选择File→SaveAs命令,找到已建立文件夹进行保存,并将文本文件进行命名**.vhd格式。

三、设计的VHDL程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYmux4IS

PORT(D0,D1,D2,D3:

INSTD_LOGIC;

SEL:

INSTD_LOGIC_VECTOR(1DOWNTO0);

Q:

OUTSTD_LOGIC);

ENDmux4;

ARCHITECYUREfuncOFmux4IS

BEGIN

IF(SEL=”00”)THEN

Q<

=D0;

IF(SEL=”01”)THEN

=D1;

IF(SEL=”10”)THEN

=D2;

ELSE

=D3;

ENDIF;

ENDPROCESS;

ENDfunc;

sel

Q

00

D0

01

D1

10

D2

11

D3

六、心得与体会

通过这次实验让我学会了很多,而且在课上老师得到老师很多的帮助,这也让我对QuartusⅡ软件有了很大的认识,虽然在课上学习的时间很少但是只要自己注意一些细节,总会得到一些小小的提升,而次让我懂得了四选一路选择器的设计过程,这对我以后的电路设计之路奠定基础。

实验三用七段LED显示8421BCD码的VHDL设计

1、实验目的

熟悉QuartusⅡ的VHDL文本设计流程,学习七段LED显示BCD码的设计、仿真。

下图为译码器逻辑图,其中A、B、C、D接拨号开关,a,b,c,d,f,e,g接数码管显示接口。

通过拨号开关改变输入二进制码,则输出数码管上显示相应的数值。

译码器真值表

数

值

A

B

C

D

a

b

c

d

e

f

g

2

3

4

5

6

7

8

9

四、设计的VHDL程序

ENTITYseg2IS

PORT(D:

INSTD_LOGIC_VECTOR(3DOWNTO0);

Y:

OUTSTD_LOGIC_VECTOR(6DOWNTO0)

);

ENDseg2;

ARCHITECTUREoneOFseg2IS

PROCESS(D)

IF(D="

0000"

)THENY<

="

1111110"

;

ELSIF(D="

0001"

0110000"

0010"

1101101"

0011"

1111001"

0100"

0110011"

0101"

1011011"

0110"

1011111"

0111"

1110000"

1000"

1111111"

1001"

1111011"

Y<

0000000"

endprocess;

ENDone;

五、实验结果

六、结果分析

结果的转换如下:

二进制

十进制

十六进制

1111110

7E

0110000

30

1101101

6D

1111001

79

0110011

33

1011011

5B

1011111

5F

1110000

70

1111111

7F

1111011

7B

七、心得与体会

实验告诉我们只有你一丝不苟的对待,才能有正真的体验,你只有认真的写程序才能有发现自己错的地方,才能更好的体会到实验的美丽所在之处,虽然现在我们可能有很多不理解的地方,重要我们抱着好学的态度终有一天我们会意想不到的收获。

实验四十进制计数器的设计

进一步熟悉QuartusⅡ的VHDL文本设计流程全过程,学习计数器的设计、仿真。

设计带有计数使能、清0控制和进位扩展输出的十进制计数器。

具有3个输入端口(CLK、RST、EN)。

CLK输入时钟信号;

RST起异步复位作用,RST=0,复位;

EN是时钟使能,EN=1,允许计数(CLK上升沿计数)。

有2个输出端口(CQ和COUT)。

CQ的位宽为4,输出计数值,从0到9;

COUT是输出进位标志,位宽为1,每当CQ为9时输出一个高电平脉冲。

1、建立文件夹CNT10B,以便设计项目的存储。

2、建立VHDL文件,编写VHDL程序,存盘。

3、建立工程文件。

4、编译VHDL文件。

5、建立波形文件CNT10B.vwf,设置仿真输入信号,存盘。

6、进行仿真(仿真时间50

),分析结果。

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNT10BIS

PORT(CLK,RST,EN:

CQ:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT:

ENDCNT10B;

ARCHITECTUREbehavOFCNT10BIS

BEGIN

PROCESS(CLK,RST,EN)

VARIABLECQI:

STD_LOGIC_VECTOR(3DOWNTO0);

IFRST='

0'

THENCQI:

ELSIFCLK'

EVENTANDCLK='

1'

THEN

IFEN='

THEN

IFCQI<

9THENCQI:

=CQI+1;

ELSECQI:

ENDIF;

IFCQI=9THENCOUT<

='

ELSECOUT<

CQ<

=CQI;

ENDPROCESS;

ENDbehav;

六、实验分析

完成了0到9数的叠加。

当en=0时,数无法完成叠加。

当res=0时,数会发生清零的现象。

七、试验总结

经过这次的eda实验,我个人得到了不少的收获,一方面加深了我对课本理论的认识另一方面也提高了实验操作能力。

现在我总结了以下的体会和经验。

这次的实验跟我们以前做的实验不同,因为我觉得这次我是真真正正的自己亲自去完成。

所以是我觉得这次实验最宝贵,最深刻的。

就是实验的过程中程序全是我们学生自己动手编写的,这样,我们就必须要弄懂实验的原理。

在这里我深深体会到哲学上理论对实践的指导作用:

弄懂实验原理,而且体会到了实验的操作能力是靠自己亲自动手,亲自开动脑筋,亲自去请教别人才能得到提高的。

实验五JK触发器的实验电路

熟练使用QuartusⅡ的VHDL文本设计,学习时序逻辑电路的设计、仿真。

编写VHDL程序描述一个JK触发器电路,实现真值表中的功能。

带异步复位/置位端的JK触发器的真值表

set

reset

clk

J

K

QB

不使用

上升沿

保持

翻转

其中,set为置位引脚,输入,低电平有效;

reset为复位引脚,输入,低电平有效;

clk是时钟引脚,输入;

J,K输入引脚。

Q,QB输出引脚。

1、建立文件夹jk_ff,以便设计项目的存储。

2、启动QuartusII软件,建立VHDL文件并存盘。

5、通过编译后,建立波形文件jk_ff.vwf,设置仿真输入信号,存盘。

四.试验程序

ENTITYjk_ffIS

PORT(set,reset,j,k,clk:

Q,QB:

BUFFERSTD_LOGIC);

ENDjk_ff;

ARCHITECTUREoneOFjk_ffIS

BEGIN

PROCESS(set,reset,j,k,clk)

IF(set='

)THEN

QB<

ELSIF(reset='

ELSIF(CLK'

)THEN

IF(j='

)AND(k='

ELSIF(j='

=NOTQ;

=NOTQB;

ENDONE;

由实验结果可得当set=0时,置位q=1,qb=0;

当reset=0时,置零q=0,qb=1;

当set=1,reset=1,且j=0,k=0时,q=q,qb=qb,

当set=1,reset=1,且j=0,k=0时,q=0,qb=1,

当set=1,reset=1,且j=0,k=0时,q=1,qb=0,

当set=1,reset=1,且j=0,k=0时,q=notq,qb=notqb;

七、实验总结

通过这次实验让我学会了很多,这次比如我向老师请教了很多关于怎样写程序,以及再写程序的过程中遇到的问题,这对我来说太重要了,对我以后如何正确写程序埋下的重要的伏笔。

我以后一定会感激现在的时光。