简单计算机系统的设计与实现报告1A.docx

《简单计算机系统的设计与实现报告1A.docx》由会员分享,可在线阅读,更多相关《简单计算机系统的设计与实现报告1A.docx(12页珍藏版)》请在冰豆网上搜索。

简单计算机系统的设计与实现报告1A

简单计算机系统的设计与实现报告1_A

一、实验目的

1.掌握简单计算机系统的基本构成与设计步骤。

2.掌握简单计算机系统的指令集。

3.掌握简单计算机的基本模块。

4.巩固EDA电路仿真和调试方法。

二、实验任务

1.阅读“简单计算机系统的设计与实现任务书”,了解基本构成和设计步骤,

拟定初步的设计思路、进度,及调试手段。

2.阅读“简单计算机系统的设计与实现任务书”,掌握要设计的简单计算机系统的指令集,练习指令编码。

A。

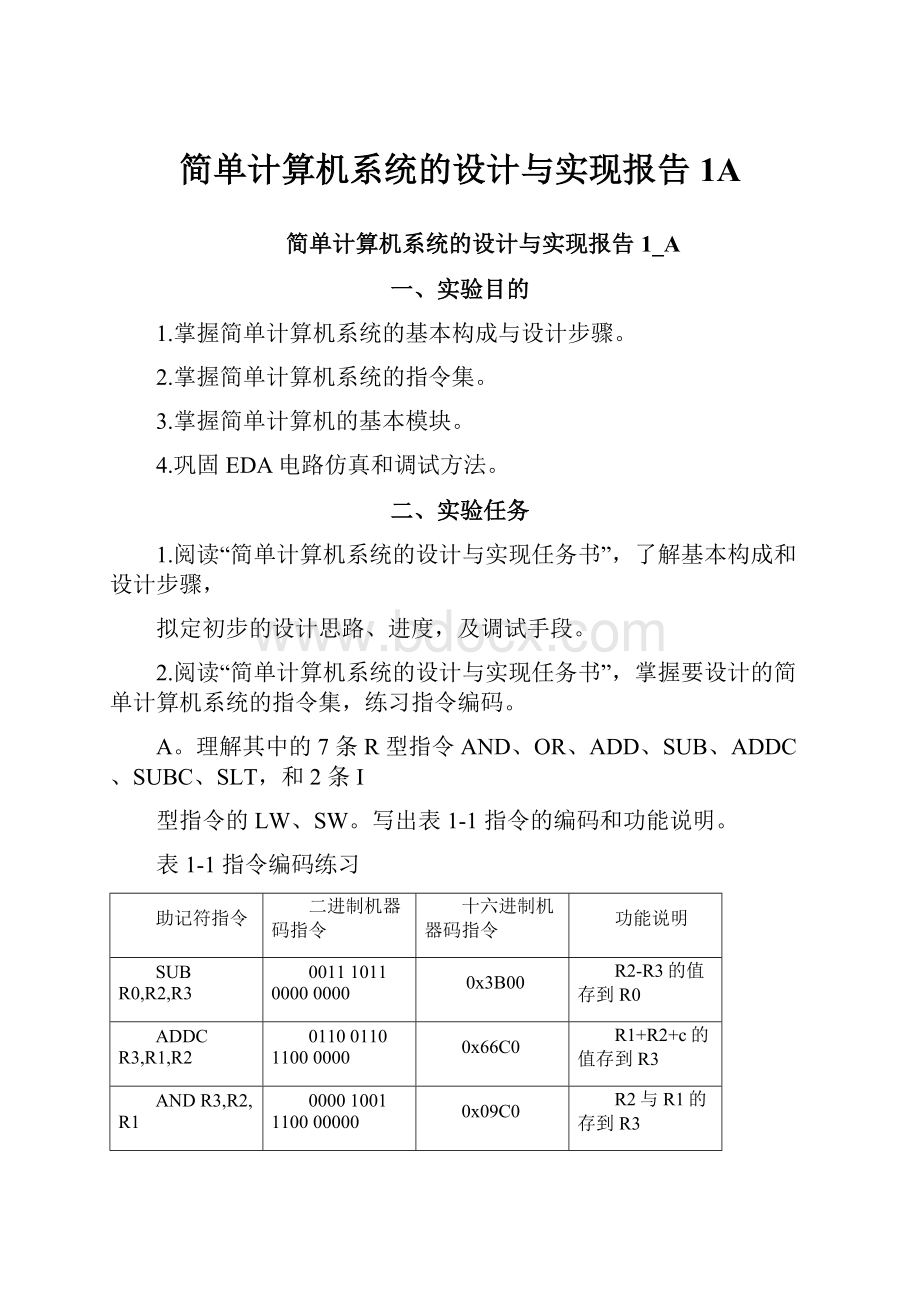

理解其中的7条R型指令AND、OR、ADD、SUB、ADDC、SUBC、SLT,和2条I

型指令的LW、SW。

写出表1-1指令的编码和功能说明。

表1-1指令编码练习

助记符指令

二进制机器码指令

十六进制机器码指令

功能说明

SUBR0,R2,R3

0011101100000000

0x3B00

R2-R3的值存到R0

ADDCR3,R1,R2

0110011011000000

0x66C0

R1+R2+c的值存到R3

ANDR3,R2,R1

00001001110000000

0x09C0

R2与R1的存到R3

ORR2,R1,R3

0001011000100010

0x1780

R1或R3的值赋给R2

LWR1,R2,0x22

1011011000100010

0xB622

R2的地址加上立即数后的地址存储的数存在R1中

SWR3,R1,0x24

1100110100100100

0xCD24

R1的地址加上立即数后的地址存储的数值存到R3中

B。

理解其中5条I型指令的ANDI、ORI、ADDI、BEQ、BNE和1条I型指令JMP。

写出表1-2指令的编码和功能说明。

表1-2指令编码练习

助记符指令

二进制机器码指令

十六进制机器码指令

功能说明

ANDIR2,R2,0

1000010100000000

0x8500

R2清零

ADDIR2,R2,0x24

1010010100100100

0xA520

将0x24存至R2

BNER3,R2,8

1110111000001000

0xEE08

R2不等于8取1

JMP0

0111000000000000

0x7000

PC归零

三、简单计算机系统的各大模块仿真

1.设计寄存器组模块

(1)模块封装

图1-1寄存器组模块的封装结构图

(2)模块说明

寄存器组模块信号说明:

输入信号:

N1[1..0]:

读通道1的寄存器号N2[1..0]:

读通道2的寄存器号

ND[1..0]:

写通道的寄存器号

DI[7..0]:

写通道的输入数据

CLK:

时钟脉冲信号,上升沿有效

REG_WE:

写允许,为1时,在CLK上升沿,将数据DI写入ND指定的寄存器;为“0”时,禁止对寄存器阵列进行写操作。

RST:

异步复位信号,清空所有寄存器的内容输出信号:

Q1[7..0]:

输出N1[1..0]指定寄存器的内容

Q2[7..0]:

输出N2[1..0]指定寄存器的内容

(3)仿真与分析

仿真波形如下图:

波形分析:

0~20us期间,模块输出了4个寄存器内存储的数值,初始默认均为0;

20us~30us向寄存器00中存入了数值229,此时可以看出,从00寄存器读到的数据变为229了;

50us左右时,又向寄存器11中存入了数值57,此时可以发现,读到的数据变成57了;

70us左右时,Q1和Q2分别输出11和00中存储的数据,即57和299;

均符合设计要求。

2.设计RAM数据存储系统模块

(1)模块封装

图1-2RAM数据存储系统模块封装结构图

(2)模块说明

RAM数据存储系统模块信号说明如下:

输入信号:

address[7..0]:

需要进行读/写操作RAM单元的地址data[7..0]:

待写入RAM中的数据

wren:

写允许信号,为1时写;为0则读

clock:

时钟脉冲信号,上升沿将数据写入或读出aclr:

异步复位信号,对q[7..0]进行清0输出信号:

q[7..0]:

输出address[7..0]指定的RAM单元的内容

(3)仿真与分析

仿真波形如下:

波形分析:

0~80ns期间,wren为1表示不停的写入数据,故输出值始终与写入的数据一致;

80ns~160ns期间,wren为0停止写入,只是读取最后一次在地址中存储的数据;

均符合设计要求。

3.设计I/O端口及其映射模块

(1)模块封装

图1-4I/O端口及其映射模块封装结构图

(2)模块说明

I/O端口及其映射模块信号说明:

输入信号:

addr[7..0]:

地址输入信号

Din[7..0]:

写入I/O端口中的数据信号

RE:

读控制信号,高电平有效WE:

写控制信号,高电平有效输出信号

Dout[7..0]:

读I/O端口时输出的数据信号

io_read:

I/O端口读控制信号,高电平有效,读0x00~0x07存储单元时有效io_write:

I/O端口写控制信号,高电平有效,写0x00~0x07存储单元时有效输入/输出信号

IO0[7..0]:

双向I/O端口0的数据信号IO1[7..0]:

双向I/O端口1的数据信号IO2[7..0]:

双向I/O端口2的数据信号IO3[7..0]:

双向I/O端口3的数据信号IO4[7..0]:

双向I/O端口4的数据信号IO5[7..0]:

双向I/O端口5的数据信号IO6[7..0]:

双向I/O端口6的数据信号

IO7[7..0]:

双向I/O端口7的数据信号

(3)仿真与分析

A。

整体仿真波形

B。

写数据仿真

可以看出向IO0写入十六进制数字86时IO0的各个输出为10000110符合要求;紧接着向IO1中写入01,输出为00000001也符合要求。

C。

读数据仿真

可以看出键盘输入43,4,155,231,148,109,41,198此时RE为1,Dout一次输出了这一系列数字,满足了设计要求。

4.设计和检测ROM程序存储模块

(1)模块封装

图1-5ROM程序存储系统模块封装结构图

(2)模块说明

ROM数据存储系统模块信号说明如下:

输入信号:

address[7..0]:

ROM单元的地址

clock:

时钟脉冲信号,在时钟的上升沿,将选中的ROM单元内容输出输出信号:

q[15..0]:

输出address[7..0]指定的ROM单元的内容

(3)仿真与分析

仿真波形如下:

波形分析:

每次上升沿读取一次数据,符合要求。

5.设计8位算术逻辑运算器ALU模块

(1)模块封装

1-6ALU模块的封装结构图

(2)模块说明

表1-3ALU的运算关系

CS[2..0]

运算名称

运算操作

与

S[7..0]=data_a[7..0]ANDdata_b[7..0]

或

S[7..0]=data_a[7..0]ORdata_b[7..0]

不带进位加

S[7..0]=data_a[7..0]+data_b[7..0]

不带借位减

S[7..0]=data_a[7..0]-data_b[7..0]

带进位加

S[7..0]=data_a[7..0]+data_b[7..0]+Carry_in

带借位减

S[7..0]=data_a[7..0]-data_b[7..0]–(1-Carry_in)

比较

Ifdata_a[7..0]输入信号:

data_a[7..0]、data_b[7..0]:

参与操作的两个8位二进制数

CS[2..0]:

存放7种运算操作的编码,编码规则自定

Carry_in:

参与运算的进/借位值输出信号:

S[7..0]:

操作后的8位结果存放在中,

Zero:

零标志

当s[7..0]为0时,zero=1;否则zero=0;

Carry_out:

进位/借位标志当加法运算过程最高位有进位时,Carry_out=1;否则Carry_out=0;当减法运算最高位产生借位时,Carry_out=0;否则,Carry_out=1

(3)仿真与分析:

仿真波形:

波形分析:

0表示与运算,01100100&11001000=01000000即64.正确;

1表示不带借位减法,200-100=100;

2表示带借位减法,200-100-(1-0)=99;

3表示比较大小,200>100输出0,zero也为0;

4表示带进位加法,100+200+1=301,去掉超出的256以后为45;

5表示不带进位加法,100+200=300,去掉超出的256以后为44;

6表示或运算,11001000or01100100=11101100即236;

7不做任何运算,输出始终为0;

6.设计标志寄存器模块

(1)模块封装

图1-7标志寄存器模块封装结构图

(2)模块说明

标志寄存器模块信号说明:

输入信号:

Flagin[7..0]:

写人标志寄存器的数据,如Carry、Zero等信息,每个标志占1位,共3位,其他5位暂时无用。

CLK:

写时钟脉冲信号,上升沿时,将Flagin上的数据写入Flagout中

Reset:

异步复位信号,对标志寄存器内容清零flagout[7..0]=0输出信号:

flagout[7..0]:

标志寄存器的数据

(3)仿真与分析

仿真波形:

波形分析:

Reset为1时,每次Clk上升沿将Flagin输出,Reset为0时,输出0;符合设计要求。

四、实验小结

此次实验为简单计算机系统设计的最初部分,主要是各个模块功能的理解与仿真,温习暑期学习的软件使用与仿真调试技巧,比较简单。

这次实验我对一个计算机的基本组成有了初步的了解,知道了许多相关的知识,了解了微机的组成。

同时,我对Quartus的仿真有了更深的了解。

此次实验遇到的问题就是软件破解,开始我安装好90后,无法正常破解,后来不得不用13版本进行完成,但是13的自带仿真无法保存波形文件,故只能靠截图来实现这一功能。