数字逻辑课程三套作业及答案资料文档格式.docx

《数字逻辑课程三套作业及答案资料文档格式.docx》由会员分享,可在线阅读,更多相关《数字逻辑课程三套作业及答案资料文档格式.docx(25页珍藏版)》请在冰豆网上搜索。

A.n

B.2n

C.2n-1

D.2n-2n

解析第九章集成计数器

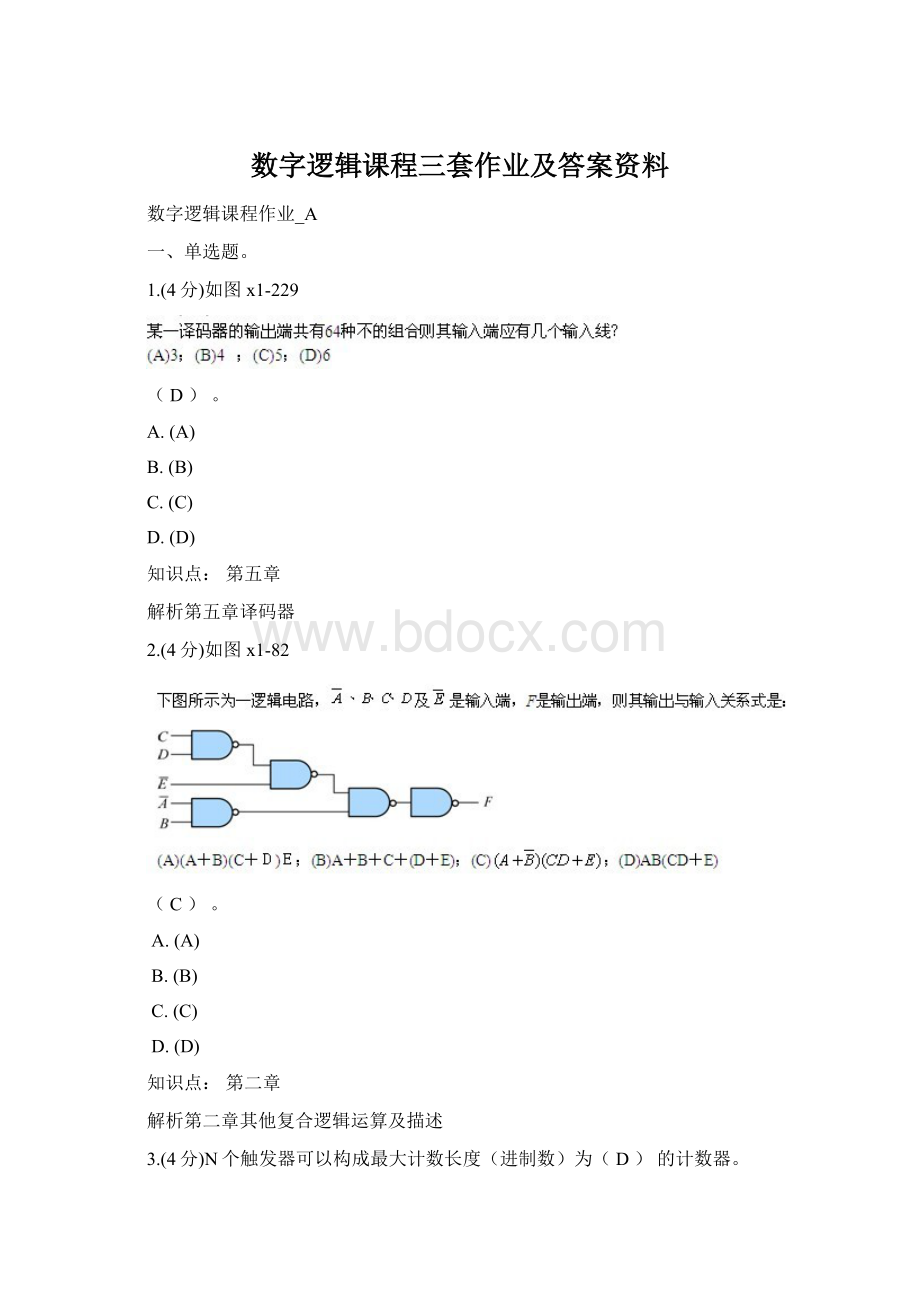

5.(4分)如图x1-293

(A)。

第十一章

解析第十一章数字系统概述

6.(4分)如图x1-317

7.(4分)EPROM是指(C)。

A、随机读写存储器

B、只读存储器

C、光可擦除电可编程只读存储器

D、电可擦可编程只读存储器

第十章

解析第十章只读存储器

8.(4分)如图x1-407

(B)。

9.(4分)为实现将JK触发器转换为D触发器,应使(A)。

J=D,K=D非

B.K=D,J=D非

C.J=K=D

D.J=K=D非

第六章

解析第六章各种触发器的比较

10.(4分)一位8421BCD码计数器至少需要(B)个触发器。

3

B.4

C.5

D.10

11.(4分)为把50Hz的正弦波变成周期性矩形波,应当选用(A)。

A、施密特触发器

B、单稳态电路

C、多谐振荡器

D、译码器

解析第六章集成触发器

12.(4分)下列描述不正确的是(A)。

a.D触发器具有两个有效状态,当Q=0时触发器处于0态

b.移位寄存器除具有数据寄存功能外还可构成计数器

c.主从JK触发器的主触发器具有一次翻转性

d.边沿触发器具有前沿触发和后沿触发两种方式,能有效克服同步触发器的空翻现象

13.(4分)如图x1-231

解析第二章逻辑代数的化简法

14.(4分)如图x1-378

解析第十一章PLA与GAL

15.(4分)微程序控制器有64条微指令,则微地址寄存器的长度是(B)位。

64

6

8

26

第一章

解析第一章数字逻辑基础

二、单选题。

1.(4分)如图x1-371

2.(4分)如图x1-31

3.(4分)如图x1-85

解析第一章二进制数的表示

4.(4分)微程序控制方法中,控制存储器一般用(B)来实现。

A.RAM

B.EPROM

C.E2PROM

D.EAROM

解析第十章通用逻辑阵列

5.(4分)如图x1-247

解析第一章数制转换

6.(4分)如图d1-42

a

b

c

d

第四章

解析第四章组合逻辑电路的分析

7.(4分)ASM流程图是设计(C)的一种重要工具。

A.运算器

B.计数器

C.控制器

D.存贮器

解析第十一章 数字系统设计概述

8.(4分)如图x1-102

第三章

解析第三章其他类型的TTL与非门电路

9.(4分)只读存储器ROM的功能是(A)。

A、只能读出存储器的内容,且掉电后仍保持

B、只能将信息写入存储器

C、可以随机读出或存入信息

D、只能读出存储器的内容,且掉电后信息全丢失

10.(4分)A/D分类:

⑴逐次逼近型,⑵并联比较型,⑶双积分型,⑷电压频率变换型,其中工作速度最快的是(B)。

逐次逼近型

并联比较型

双积分型

电压频率变换型

第八章

解析第八章9数/模和模/数转换器

数字逻辑课程作业_B

1.(4分)如图x1-248

(C)。

解析第二章真值表化简法

2.(4分)ROM不能用于(C)。

函数运算表

B.存入程序

存入采集的动态数据

D.字符发生器

3.(4分)存储8位二进制信息要(D)个触发器。

2

B.3

C.4

D.8

解析第六章触发器的特点和分类

4.(4分)如图x1-80

(B)。

5.(4分)如图x1-299

解析第四章逻辑函数的实现

6.(4分)BCD码(01010010)转换为十进制数为(C)。

A:

38

B:

82

C:

52

D:

28

解析第一章码制

7.(4分)JK触发器,若J,K端在一起,即J=K,则该触发器变为(D)触发器。

RS

不变

D

T

解析第五章触发器/同步JK触发器

8.(4分)如图x1-361

9.(4分)如图x1-16

(D)。

10.(4分)如图h-d-1-6

A

B

C

解析第三章逻辑代数基础/常用的公式和定理

11.(4分)用n个触发器构成的计数器,可得到的最大计数模是(C)。

(A)n

(B)2n

(C)2n

(D)2n-1

解析第六章触发器电路结构和工作原理

12.(4分)当用异步I/O输出结构的PAL设计逻辑电路时,它们相当于(A)。

组合逻辑电路

B.时序逻辑电路

C.存储器

D.数模转换器

解析第十章可编程逻辑阵列

13.(4分)如图x1-239

解析第四章组合逻辑电路分析

14.(4分)欲将容量为256×

1的RAM扩展为1024×

8,则需要控制各片选端的辅助译码器的输入端数为(B)。

4

B.2

C.3

解析第十章地址译码方法

15.(4分)如图x1-369

解析第五章数据选择器

1.(4分)只读存储器ROM在运行时具有(A)功能。

读/无写

无读/写

C.读/写

D.无读/无写

2.(4分)如图x1-215

解析第三章TTL与非门电路

3.(4分)如图h-d-1-9

4.(4分)如图d1-11,电路实现的逻辑功能F=(C)。

(A)AB

(B)0

(C)A+B

(D)1

5.(4分)一个触发器可记录一位二进制代码,它有(C)个稳态。

B.1

C.2

D.3

E.

E.4

6.(4分)如图x1-95

(A)。

解析第二章逻辑函数的化简法

7.(4分)如图x1-370

A.(A)

解析第二章逻辑函数的两种标准形式

8.(4分)如图x1-247

9.(4分)如图x1-301

解析第三章MOS集成逻辑门电路

10.(4分)一位十进制计数器至少需要(B)个触发器

5

10

数字逻辑课程作业_C

1.(4分)以下电路中常用于总线应用的有(A)。

TSL门

B.OC门

C.漏极开路门

D.CMOS与非门

2.(4分)如图x1-119

(C)。

3.(4分)如图x1-256

(A)。

4.(4分)为把50Hz的正弦波变成周期性矩形波,应当选用(A)。

5.(4分)要使TTL与非门工作在转折区,可使输入端对地外接电阻RI(C)。

>RON

B.<ROFF

C.ROFF<RI<RON

D.>ROFF

6.(4分)如图x1-222

(D)。

7.(4分)如图x1-236

8.(4分)如图x1-255

(B)。

9.(4分)十进制数62对应的十六进制数是(A)。

(3E)16

(36)16

(38)16

(3D)16

解析第一章数字逻辑基础/不同数制间的转换

10.(4分)用n个触发器构成计数器,可得到的最大计数模是(C)。

2n

D.2n-1

11.(4分)请判断以下哪个电路不是时序逻辑电路(C)。

A、计数器

B、寄存器

C、译码器

D、触发器

第七章

解析第七章时序逻辑电路的结构

12.(4分)以下电路中可以实现线与功能的有(D)。

与非门

B.三态输出门

C.传输门

漏极开路门

13.(4分)相邻两组编码只有一位不同的编码是(D)。

2421BCD码

8421BCD码

余3码

格雷码

解析第一章数字逻辑基础/几种常用数制

14.(4分)如图x1-333

15.(4分)已知F=!

(ABC+CD),下列组合中,(D)可以肯定使F=0。

A=0,BC=1

B.B=1,C=1

C=1,D=0

BC=1,D=1

1.(4分)如图x1-378

2.(4分)如图x1-95

3.(4分)如图x1-80

4.(4分)如图h-d-1-9

5.(4分)欲设计0,1,2,3,4,5,6,7这几个数的计数器,如果设计合理,采用同步二进制计数器,最少应使用(B)级触发器。

6.(4分)要使J—K触发器在时钟脉冲作用下的次态与现态相反,J—K的取值应为(B)。

A、00

B、11

C、01

D、01或10

解析第六章时钟JK触发器的结构,功能

7.(4分)如图x1-138

8.(4分)如图x1-40

9.(4分)一位十进制计数器至少需要(B)个触发器。

10.(4分)如图x1-105