整理以太网控制器MAC设计Word文件下载.docx

《整理以太网控制器MAC设计Word文件下载.docx》由会员分享,可在线阅读,更多相关《整理以太网控制器MAC设计Word文件下载.docx(36页珍藏版)》请在冰豆网上搜索。

以太网最初是由Xerox公司在70年代提出的,1982年DEC、Intel和Xerox制定了DIX标准,即10Mbps普通以太网标准。

1983年,IEEE

组织公布了IEEES02.3标准,10Mbps以太网得到了国际的认可,标志着以太网标准的正式成立,同时也标志着符合国际标准的以太网技术的面世。

1995年IEEE通过了IEEE802.3u标准,标志着100Mbps快速以太网时代的到来。

随着网络用户的日益增加,10Mbps带宽在一些环境下不能满足人们对信息传输速率要求。

因此快速以太网推出得到了广泛的推广。

快速以太网是在10Mbps普通以太网上基础上发展起来的,它在保持帧格式,介质访问控制的前提下,工作速率比普通以太网快10倍。

IEEE802.3u快速以太网标准是IEEE802.3标准的补充,并且兼容10Mbps以太网。

10Mbps和100Mbps以太网组网方便,价格低廉,性能高效在局域网中受到了广泛应用。

1998年通过了IEEE802.3z标准,以太网的运行速度达到1Gbps,目前已出现了10Gbps的以太网。

与传统的CAN、RS.485等相比较,以太网速度更快、通用性更好,而且能直接与因特网相连,具有更大范围的远程访问。

相对于新兴的USB,IEEEl394等总线,以太网在传输距离和控制软件的通用性上有明显的优势。

近几年随着深亚微米集成电路工艺技术的飞速发展,SoC(SystemonaChip)已经成为IC界关注的焦点,单一芯片上能够容纳更多的逻辑单元成为芯片设计发展的必然趋势。

将所有的功能块集成在一个单独的芯片上可以大幅度降低系统成本,减少系统的面积和功耗,提高系统的可靠性。

SoC已经渗透到通信、多媒体、计算机控制以及其它一些数字领域,以太网技术在嵌入式系统中的开发应用,已成为当前嵌入式领域研究的技术热点之一。

嵌入式以太网在工业控制、商业领域、交通行业、家庭自动化等有着良好的应用前景,同时嵌入式设备以其价格低廉、体积小以及实时性使得嵌入式系统的网络化开发有着通用处理器无法比拟的优点。

嵌入式系统的网络化,使得SoC有了更广泛的应用范围。

在嵌入式系统的网络化开发过程中,首先要解决嵌入式设备与以太网络的连接问题,即网络芯片的设计。

常见的具有网络功能的芯片有两类,一类是专用的以太网芯片,集成了MAC控制器和PHY,例如REALTEK8019AS、8039AS,这类芯片一般用于网卡、路由器等设备,另一类是用控制、工业领域的具有网络功能的SoC芯片,例如,PHILIPSLPC2400,这类芯片通常集成了MAC控制器,但由于Pmr的模拟电路特性及设计工艺的兼容性问题,这类芯片一般都使用外置的PHY芯片来实现对以太网的支持。

在嵌入式领域,通信技术的发展要求对网络的支持越来越广泛,所以研究和设计一个用于嵌入式SoC芯片的以太网MAC控制器,具有相当的实际意义。

当今,以太网已经极大地影响我们的生活,嵌入式系统上的开发应用,已经成为当前嵌入式研究领域的技术热点之一,一方面,与传统的RS-485.CAN等相比较,以太网更加高速、通用,而且还可以直接与Internet相连接,提供更大范围的远程访问;

另一方面,相对于新兴的USB2.0、IEEE1394等总线,以太网技术在传输距离、不想成本以及控制软件的通用性上都有明显优势。

第1章课程设计的要求

1.1课程设计的目的

●了解掌握以太网控制器的工作原理

●掌握较大工程的基本开发技能

●培养综合运用Modelsim,ISE工具进行硬件开发的能力

●培养数字系统设计的基本能力

1.2课程设计的要求

●执行以太网IEEE802.3协议MAC要求的功能

●自动产生和检查32bitCRC

●在发送时自动填充长度小于规定的帧

●监测帧过长或过短

●兼容10Mbps和100Mbps两种速率

●当碰到过小的帧间隔或过长的延迟时间时自动丢弃帧

●在全双工模式下控制流量并且自动产生控制帧

●在半双工模式下进行冲突检测并且在冲突时自动重传

●完成对发送/接收的状态解析

●容纳128个缓冲描述符的内部RAM和存储帧的内部RAM

●发送和接收帧时的异步双口FIFO

●发送帧模块:

处理所有有关帧发送的操作

●接收帧模块:

处理所有有关帧接收的操作

●控制模块:

在全双工的工作模式下,处理所有有关数据流控制的操作

●状态模块:

要写入到缓冲描述符或其他模块要调用的不同的状态

●寄存器模块:

所有要在MAC层操作中用到的寄存器

第2章课程设计的内容

2.1设计思路

本文主要阐述基于FPGA对IEEE802.3快速以太网MAC层功能的实现。

采用自顶向下、分块设计的思路,逐个实现MAC主要功能模块,诸如发送模块、接收模块、MAC控制模块以及物理层和主机接口模块等,按照IP核的标准进行设计。

同时考虑到对主机和PHY总线连接,MAC内部都采用8位数据线,32位地址线,而在和PHY接口连接时采用4位数据通道。

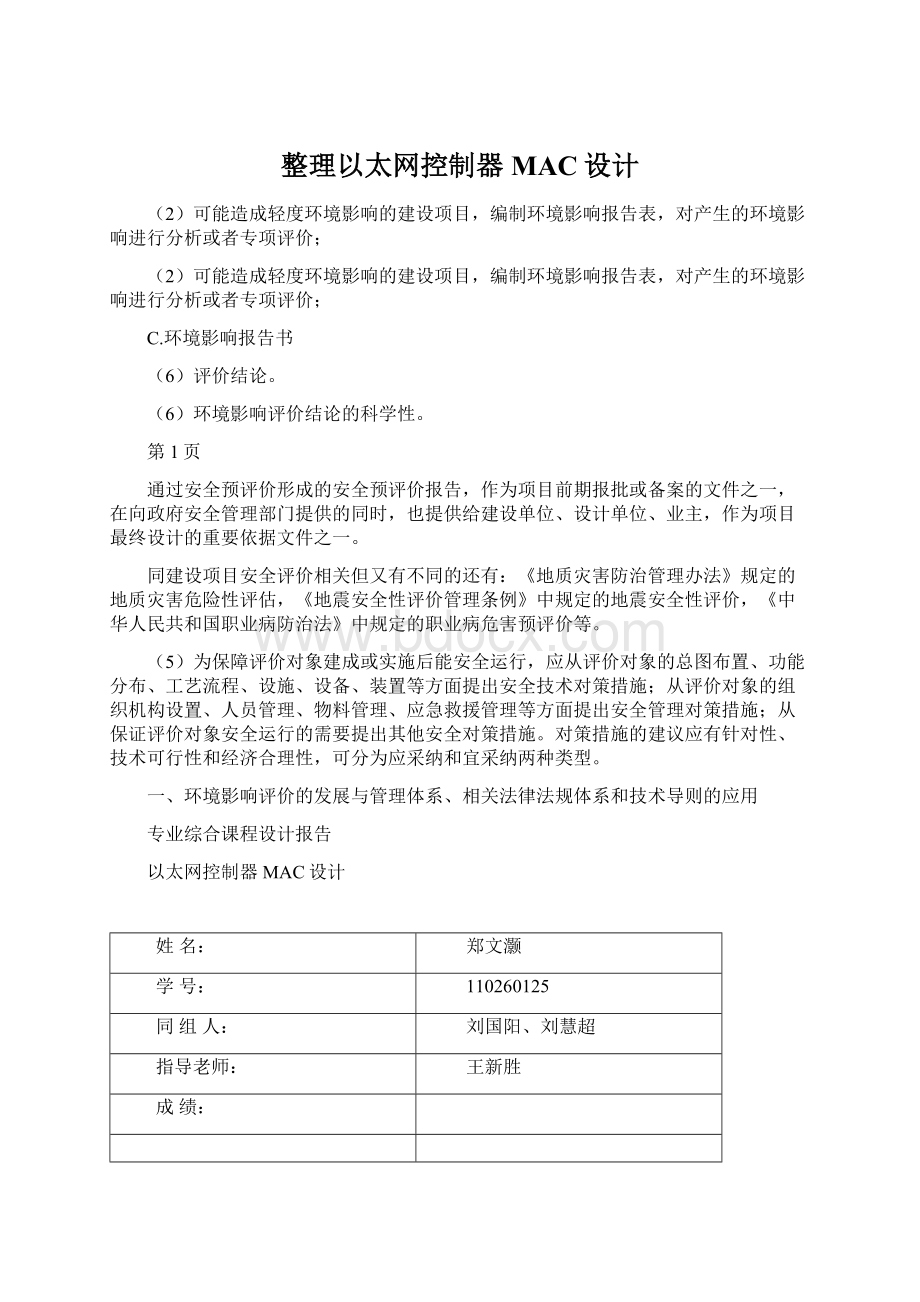

MAC层主体框架如图2-1所示,主要模块有:

MII模块、MAC控制模块、接收帧模块、发送帧模块、状态模块、寄存器模块、存储模块、主机总线接口模块,以及用于时钟同步、复位和寄存器输出的模块。

图2-1MAC控制器结构框图

这里,有必要说一下IEEE802.3帧格式,如图2-2所示。

图2-2IEEE802.3帧格式

1)Pre(Preamble):

前导码,7字节0x55信号,接收站点通过该字段知道接收到数据帧信息,

并使网络两端的物理层达到稳定同步状态。

2)SFD(Start.of-FrameDelimiter):

定界符,表示一个有效帧的开始,1字节的0xD5。

当接收

站收到定界符时表示一帧数据的开始。

3)DA(DestinationAddress):

目的地址,69节。

DA字段用于识别需要接收帧的站点。

目的

地址可以分为单播地址,多播地址和广播地址。

单播地址是一个站点的特定的地址,当发送地址为

单播地址只有这个地址的站点才能接收。

多播地址是一个组地址,当发送目的地址为多播地址时,

这一组站点才能接收。

广播地址,当发送目的地址为广播地址时,这个广播域的地址都可以接收。

广播地址为特殊的组播地址,地址全为1。

4)SA(SourceAddress):

源地址,69节。

SA字段用于识别发送帧的站点。

5)Length/Type:

长度/类型,29节。

如果是采用可选格式组成帧结构时,该字段既表示包含

在帧数据字段中的MAC数据大小,也表示帧类型。

6)Data(Pad):

数据和填充域,是一组n(46≤n≤1500)字节的任意值序列。

由于CSMA/CD

算法的限制,以太网帧必须不小于64字节,如果小于该字节长度,则要进行数据填充以达到最小帧

长度。

帧长度最长为1518字节。

7)FCS(FrameCheckSequence):

帧校验,49节。

该序列包括32位的循环冗余校验值,由发

送MAC方生成,在接收时用同样的算法进行校验,用来判断这帧数据是不是在发送过程中产生错

误。

被校验的范围包括目的地址域,源地址域,长度/类型域,数据域和填充域。

2.2功能模块分析

2.2.1寄存器模块

eth_registers是MAC层的寄存器模块。

所有的寄存器都是32位宽度,但是具体用到的则由寄存器实际所需宽度所决定,其余位填0.每个寄存器都有两个参数:

宽度和Reset值。

Reset值定义寄存器清零后设置的默认值。

寄存器模块共有23个寄存器。

通过访问寄存器并对寄存器内容进行读写操作便可完成一些状态监测和功能选择。

2.2.2接收帧模块

接收帧模块eth_rxethmac.v的任务就是接收帧数据。

外部的以太网PHY芯片将串行数据传送至MII模块,最后成为一个个nibble(MRxD[3:

0])发送到接收模块里去,同时还有“数据有效”的掩码位MRxDV.然后发送模块就把这些nibble聚集成字节byte的形式,再和一些表示数据开始和结束的信号一起发送到主机总线接口。

接收模块还需要实现的功能包括有移除接收到的帧的前导码、帧起始定界符,产生用于地址识别并发送到HASH表内,对所有接收到的包进行CRC校验。

图2-3是该模块的整体结构框图。

图中“计数匹配信号”表示当计数器达到一些特定值时,将相应特征信号触发输出为1。

图2-1接收模块整体框图

接收模块有下列子模块组成:

Ø

eth_crc——CRC(循环冗余校验码)模块

eth_rxaddrcheck——地址识别模块

eth_rxcounters——与数据包接收有关的计数器模块

eth_rxstatem——接收模块状态机

除了上述的子模块,接收模块还用到下列逻辑信号:

产生CRCHash值和HashGood信号位,用于地址识别模块

锁存从PHY芯片接收到的数据RxData_d

目的地址广播Broadcast或者组播Multicast信号

产生信号RxValid、RxStartFrm、RxEndFrm,表征数据传输的有效性

HugEn,是否允许接收大包。

定义与寄存器PACKETLEN、r_IFG,是否允许最小帧间隔,用于计数器模块的判决条件

r_Pro、r_Bro、r_Iam和寄存器MAC、HASH0、HASH1,用于地址识别。

HASH0和HASH1是哈希算法的算法表

接收数据帧的核心是各个状态之间的转换,如图2-4所示为接收模块状态转换图。

图2-2接收模块状态转换图

通过状态机得出接收逻辑输出信号如下:

判断广播帧:

在Data0状态,当计数器ByteCnt为1,锁存的数据位0xff即目的地址第一字节全为1,为广播帧,Broadcast置为1。

判断组播帧:

在Data0状态,当计数器ByteCnt为1,锁存的数据字节最低位为1,为组播帧,Multicast置为1.

设定开始接收位:

Data0状态,当计数器ByteCnt为1或允许CRC延迟,计数器DlyCrcCnt==3,经两次时钟同步设置信号RxStartFrm为1。

设定结束接收位:

当计数器ByteCnt大于2,若MRxDV从1变0,数据状态或者接收的数据超过了最大帧限制状态时,出现这两种情况表明接收帧结束,经始终同步设置标志位RxEndFrm为1。

判断接收数据有效:

Data0状态,当计数器ByteCnt不等于零表明接收数据都是有效的,标致信号RxValid经两次时钟同步置为1。

四位/八位转换:

在数据状态,如果接收数据有效,将从MII接口接收到的四位nibbleMRxD[3:

0]依次填入RxData[7:

0]数据的高四位和第四位。

目的地址识别模块:

eth_rxaddrcheck子模块,地址识别模块的功能是决定在接收一个数据帧的时候是否接受。

MAC层的设计思路是开始接受所有的帧而后判断接收帧的目的地址,将在该子模块里面被检查。

帧接收需要以下一些条件:

寄存器MODER里的Pro位被置位,所有的帧都被接收。

如果该位被清零,那就必须检查每个接收帧的目的地址。

如果寄存器MODER里的Bro位被置位,那么所有包括广播地址的帧将被拒绝接收,二球,此时Pro位必须清零。

MAC——MAC私人地址

在接收组播帧时,出于安全上的考虑,除了要检查MAC地址以外,还要采用哈希算法进行加密和解密,主要是针对组播的情况。

如前所述,无论待接收的帧的目的地址是否匹配,包接收都会先开始进行。

一旦接收到目的地址之后,就要检查是否和之前所述的任一条件匹配。

如果不匹配的话那么接收的整个包都将被抛弃,信号RxAbort被置位为1。

该包也就不会写入到内存中,并且在接收缓冲FIFO里被擦除。

CRC模块:

该模块eth_crc通过对32位CRC的值进行检验,判决接收进来的数据包的正确性和有效性。

该模块同样产生CRC校验值,并用于发送模块。

CRC发送和检查的具体描述如下:

在发送者发送数据之后,发送4字节该数据包的CRC,表明该数据包查过了4个字节。

接收者接收该数据包(包括CRC数据)并以此得出新的CRC值。

如果新的CRC值不为0,表明接收到的数据和发送的数据有了差异,置信号CrcError为1。

2.2.3发送帧模块

发送模块eth_txethmac负责发送数据帧。

发送模块从主机的总线接口得到需要被发送的字节形式的数据。

该模块也要接受表征开始数据帧发送的输入信号TxStartFrm以及结束数据帧发送的信号TxEndFrm。

图2-5是发送模块的整体框图,图中“计数匹配信号”表示当计数器达到一些特定值是,将相应特征信号触发输出为1。

图2-1发送模块整体框图

该模块由下列四个子模块组成:

eth_crc——CRC模块,产生32-bitCRC校验码写在数据域之后

eth_random——当碰到冲突(Collision),后退程序在执行的时候需要产生随机的延时,用于CSMA/CD算法

eth_txcounters——在数据帧发送的时候需要用到的些许计数器

eth_txstatem——发送模块状态机

该模块同时设置了不同的信号组,想主机和以太网PHY芯片两边分别告知相关的发送操作状态,完成、重试、忽略、错误等。

连接到以太网PHY芯片的信号、功能设计如下:

MTxD[3:

0],发送数据,将通过PHY发送至以太网,其输出类型有:

✧在状态Data0,输出发送数据低四位TxData[3:

0],在状态Data1,输出发送数据高四位TxData[7:

4]

✧在状态FCS,依次输出校验码{Crc[28],Crc[29],Crc[30],Crc[31],}

✧在状态Jam,输出0x9

✧在状态Preamble,如果NibCnt等于15,输出0xd,其他则输出0x5

✧空闲时,MTxD[3:

0]输出为0

MtxEn,发送使能信号。

告知PHY数据MTxD有效并且发送程序马上就要开始。

在状态Preamble、Data0、Data1、PAD、FCS、Jam下MtxEn信号均置为1输出。

发送错误标志MtxErr,在信号TooBig或者信号UnderRun被触发为1。

连接到上层主机总线模块的信号有:

TxDone,发送数据包完成信号

TxRetry,发送数据包重试信号

TxAbort,发送数据包忽略信号

除以上信号,发送模块还输出其他信号作为模块控制,包括对CSMA/CD算法的调度和使用。

具体输出逻辑信号定义如下:

WillTransmit,输出至eth_rxethmac模块,通知接收者发送者要开始发送数据了。

在状态Preamble、Data0、Data1、PAD、FCS、Jam以及开始前导码的标识StartPreamble,在时钟同步下置为1

ResetCollision,冲突reset信号。

将异步的冲突检测进行同步,该信号用于对同步触发器reset。

在状态Preamble、Data0、Data1、PAD、FCS几个状态下,该信号在时钟同步下置为1

ColWindow,冲突窗口。

在该窗口内每个冲突都被认为是合法的冲突,数据帧将被重新发送。

在没有检测到冲突并且ByteCnt小于有效窗口打下的情况下,若状态处于Data1,或者FCS、PAD,则该信号清零。

Reset时该信号位1

RetryCnt[3:

0],重试发送次数的计数器。

在冲突状态还没有退回,计数器ByteCnt等于7且冲突窗口有效,或者执行退回操作且计数到达随机设定的时间,就在时钟同步下对计数器加1

Data_Crc[3:

0],Enable_Crc,Initialize_Crc,用于CRC的产生。

Data_Crc

[3:

0]从高到低在分别对应发送数据nibble从低位到高位

随机数模块:

eth_random是发送模块中的随机函数子模块。

当有冲突发生时,所有相关的站都继续发送一小段时间以保证让所有的站都能发现冲突,这个过程称为堵塞。

发送模块首先发送jam形式的码0x99999999,然后停止发送数据。

在重发开始之前,模块先执行后退操作。

后退以后,站从头开始处理并尝试重发帧。

如果帧发送遭遇冲突次数达到16,它将被丢弃。

后退范围被重置,上报此事件,而站继续处理发送队列中下一帧。

任何传送尝试的后退时间都是一个随机变量,由随机数模块产生的时间长度其实是伪随机的,采用二进制的指数算法,其取值范围随重发次数指数型增长。

发送模块状态机:

eth_txstatem是发送模块的状态转换子模块,共有11个状态,如图2-6所示。

其中FullD信号表示全双工模式,IPGT和IPGR2分别表示全双工、双工模式下帧间隔的最大时间。

图2-2发送模块状态转换图

在对系统复位之后,首先触发的状态时StateDefer。

在此之后状态机进入帧间隔状态StateIPGA,然后再进入空闲状态StateIdle。

发送模块通常从该状态开始。

当发送者无事时,状态机就停留在idle状态等待发送请求信号。

总线接口通过设置信号TxStartFrm触发为1表示请求发送,该信号保持两个时钟周期,信号MtxEn被触发为1,通知以太网PHY芯片开始发送帧。

与此同时数据线MTxD[3:

0]被设为前导码的值0x5。

在前导码之后,发送数据帧间隔符0xd。

然后状态机进入到StateData0状态,信号TxUsedData被触发为1,通知主机总线提供下一个数据字节。

8位数据的低四位被发送,然后状态机进入到StateData1状态,同时发送数据字节的高四位。

状态机在data0和data1之间反复切换直到数据包发送完毕。

当还有最后一个字节要发送的时候,主机总线设置TxEndFrm触发为1。

在数据发送完毕之后,发送状态中会有如下可能性:

如果发送数据的长度大于等于最小帧长MINFL,而且允许CRC校验,那么状态机就进入到StateFCS,然后状态机进入状态StateDefer

如果发送数据的长度大于等于最小帧长MINFL,不允许进行CRC校验,那么状态机就直接进入到StateDefer状态

如果发送数据的长度小于MILFL,并且允许进行扩展填充码,那么状态机就要进入到StatePAD,然后进入到StateFCS状态,接着进入到状态StateDefer

如果发送数据的长度小于MINFL,不允许进行扩展填充码但允许CRC校验,那么状态机就进入到StateFCS,接着进入到状态StateDefer

2.2.4MAC控制模块

控制模块eth_maccontrol是执行实时数据流量控制的模块,仅工作在100Mbps速率下的全双工模式。

该模块由下列两个子模块组成:

eth_transmitcontrol,负责产生控制帧并发送

eth_receivecontrol,负责发现、解析控制帧

全双工模式通过控制操作码PAUSE实现流量控制。

当主机不能继续接受传送过来的数据包,接受FIFO就将要填满,在FIFO溢出之前,上层主机发送PAUSE控制帧至数据发送者,该控制帧请求发送者停止发送数据一段特定时间。

发送流量控制在子模块eth_transmitcontrol完成。

当MAC接收到了一个PAUSE控制帧,就依照接收到的PAUSE时间长度值启动PAUSE计时器。

每经过1个时隙计时器减1。

当计时器减至0,MAC发送模块重新开始发送。

由子模块eth_receivecontrol完成。

当控制帧被发送时,填充码padding和CRC将自动产生。

图2-7是MAC控制模块的整体框图,发送MAC帧模块产生控制帧,控制主模块通过信号CtrlMux来判决是发送控制帧还是直接发送从主机过来的数据帧到发送模块。

在发送时如果没有收到PAUSE帧,则MAC控制模块部产生任何影响。

图2-1MAC控制模块框图

2.2.5MII模块

eth_mii模块是一个提供MAC层和外部以太网PHY芯片相连接的接口。

从功能上看它可以分为两个部分:

一个是和物理层PCS子层相连接的接口信号eth_mii模块;

另一个是MII管理模块eth_miim,主要功能室设置和读写物理层PHY,进行寄存器的配置设定或从中读取数据。

图2-1MII模块整体框图

2.3HDL代码阐述

顶层模块:

`include"

eth_defines.v"

timescale.v"

moduleeth_top

(

//WISHBONEcommon

wb_clk_i,wb_rst_i,wb_dat_i,wb_dat_o,

//WISHBONEslave

wb_adr_i,wb_sel_i,wb_we_i,wb_cyc_i,wb_stb_i,wb_ack_o,wb_err_o,

//WISHBONEmaster

m_wb_adr_o,m_wb_sel_o,m_wb_we_o,

m_wb_dat_o,m_wb_dat_i,m_wb_cyc_o,

m_wb_stb_o,m_wb_ack_i,m_wb_err_i,

`ifdefETH_WISHBONE_B3

m_wb_cti_o,m_wb_bte_o,

`endif

//TX

mtx_clk_pad_i,mtxd_pad_o,mtxen_pad_o,mtxerr_pad_o,

//RX

mrx_clk_pad_i,mrxd_pad_i,mrxdv_pad_i,mrxerr_pad_i,mcoll_pad_i,mcrs_pad_i,

//MIIM

mdc_pad_o,md_pad_i,md_pad_o,md_padoe_o,

int_o

//Bist

`ifdefETH_BIST

/