quartus modelsim 时序分析 非常好 图文式 指导Word格式.docx

《quartus modelsim 时序分析 非常好 图文式 指导Word格式.docx》由会员分享,可在线阅读,更多相关《quartus modelsim 时序分析 非常好 图文式 指导Word格式.docx(15页珍藏版)》请在冰豆网上搜索。

6.2b时序仿真所需的.vo及.sdo文件。

这里我们先使用EDA工具对工程进行综合,综合通过后进行如下操作。

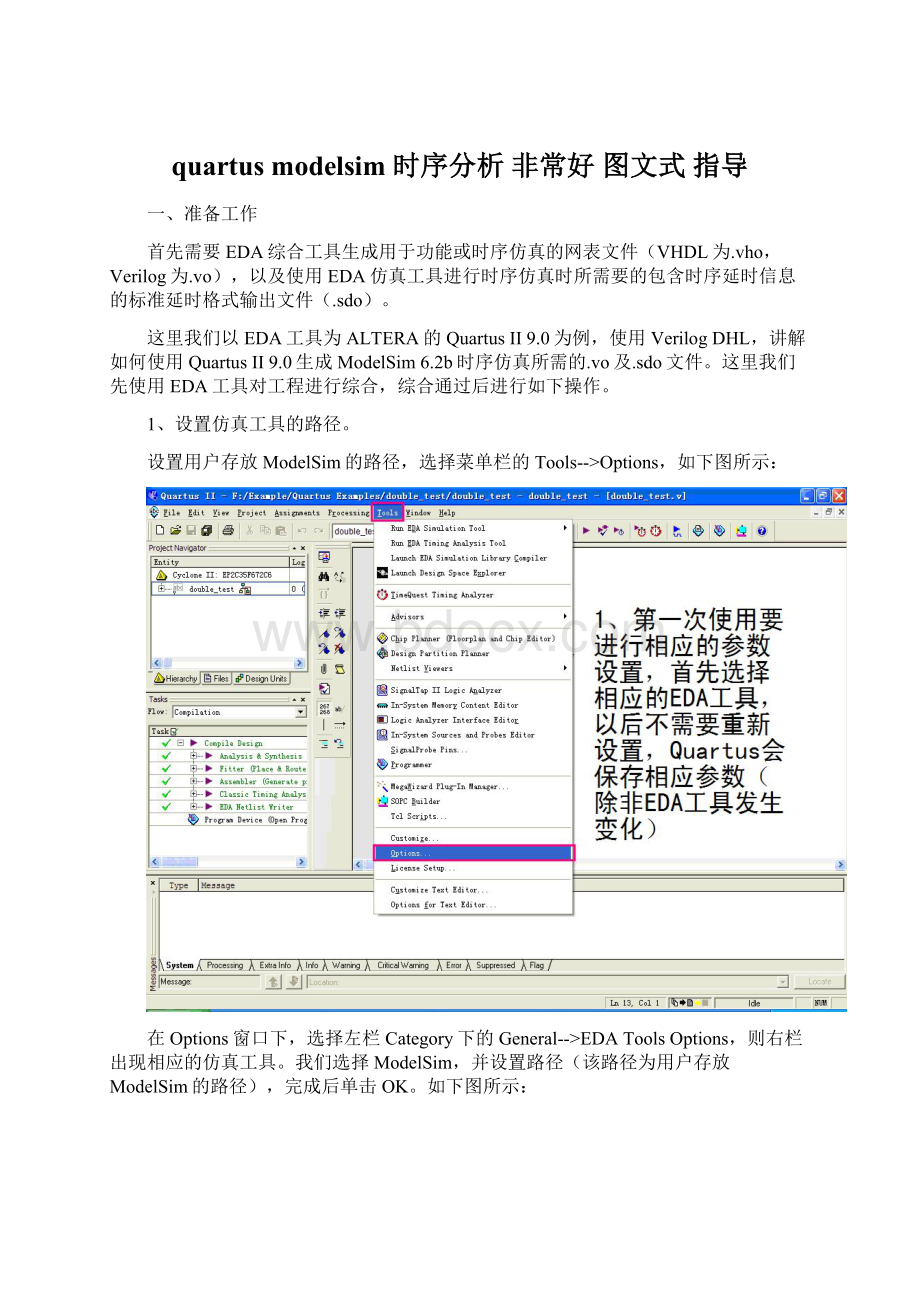

1、设置仿真工具的路径。

设置用户存放ModelSim的路径,选择菜单栏的Tools-->

Options,如下图所示:

在Options窗口下,选择左栏Category下的General-->

EDA

Tools

Options,则右栏出现相应的仿真工具。

我们选择ModelSim,并设置路径(该路径为用户存放ModelSim的路径),完成后单击OK。

如下图所示:

2、设置生成文件存放的位置。

选择菜单栏的Assignments-->

Settings,如下图所示:

此时我们进入相应的状态栏,选择左栏Category下的EDA

Options-->

Simulation,在Tool

name选择ModelSim,其他Format

for

output

netlist选择Verilog,其它使用默认参数。

完成后单击OK。

如下如所示:

至此,再次进行综合,在工程路径下的simulation/modelsim将生成后仿真(也称时序仿真)所需的网表文件(.vo)及延时文件(.sdo)。

二、ModelSim进行时序仿真

1、打开ModelSim,修改存放编译后库文件的位置。

选择菜单栏File-->

Change

Directory,如下图所示。

第一次需要编译,以后只需要调用该库文件就行,不需要重新编译(前提是使用该库支持,后面将介绍我们编译的库支持资源)。

2、建立库文件。

在Workspace窗口中Library的空白处单击鼠标的右键,选择New-->

Library,如下图所示:

3、输入相应的库文件名字。

在Library

Name输入库文件的名字,用户可自由输入,这里我们输入sim,并选择a

new

library

and

a

logical

mapping

to

it,单击OK,如下图所示:

4、开始编译EDA工具的资源。

在Workspace选择用户之前建立的库文件(我们选择sim),并选择菜单栏的Compile-->

Compile,如下图所示:

5、选择需编译资源的目录。

由于我们使用的是ALTERA的资源,EDA工具为Quartus。

选择Quartus安装目录下的quartus-->

eda-->

sim_lib。

6、选择相应的器件及使用语言。

文件名:

我们可以选择部分需要的器件,也可以选择全部器件的资源,这里我们选择全部器件的资源,日后用户无论使用什么器件都只需要调用该文件就行,不需要重新编译,若用户使用的器件资源,在本次编译中没有编译,则需重新选择器件资源进行编译。

文件类型:

选择用户编译的语言,可以使Verilog

HDL或者VHDL,同器件资源选择一样,日后若是同一种语言,不需要重新编译库文件,调用该库文件就行。

这里我们选择Verilog

Files。

确定文件名跟文件类型后,点击Compile进行编译。

7、建立工程并添加文件。

编译完成后,建立工程并添加网表(以Verilog为例.vo)及激励文件(以Verilog为例.v),并选择菜单栏的Simulate-->

Start

Simulation。

这里我们以倍频时钟为例,如下图所示:

8、选择激励。

在Start

Simulation窗口中选择激励,准备仿真。

在Design-->

work目录下,如下图所示:

9、添加库文件。

Simulation窗口中选择Libraries,单击Add,添加我们之前编译的库文件(我们选择sim),单击OK,如下图所示:

10、添加延时文件。

Simulation窗口中选择SDF,选择包含延时信息的文件(.sdo),在Browse选择路径,在Apply

Region输入实例化的名字(.v及.sdo都是由EDA工具生成)。

完成后单击OK进行仿真。

10、仿真结果。

从wave中可以看到波形图,仿真结果包含延时信息。

下载地址: