8位ALU算术逻辑单元verilog语言Word文件下载.docx

《8位ALU算术逻辑单元verilog语言Word文件下载.docx》由会员分享,可在线阅读,更多相关《8位ALU算术逻辑单元verilog语言Word文件下载.docx(12页珍藏版)》请在冰豆网上搜索。

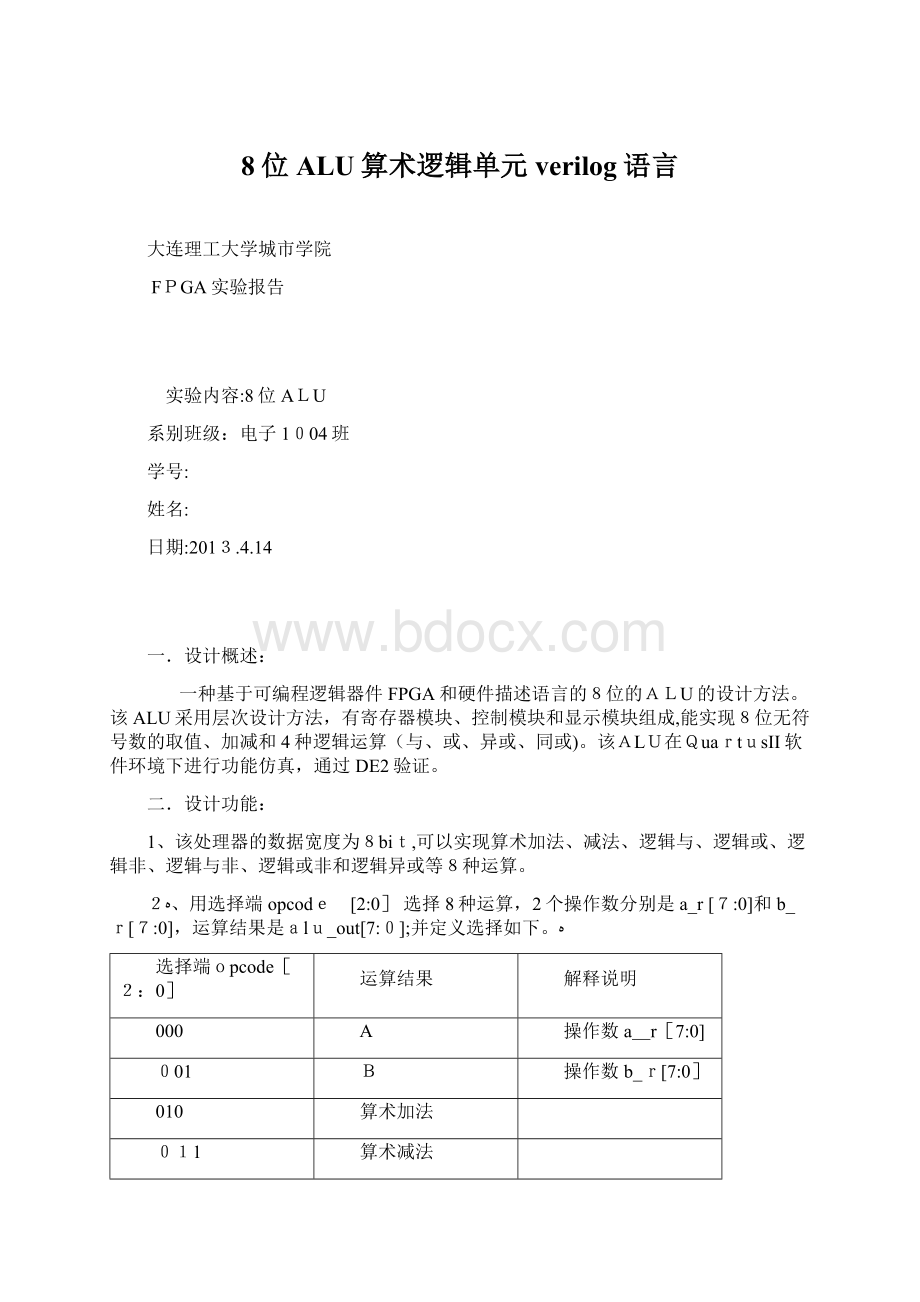

ﻩ2)寄存器A,第二个脉冲来时锁存数据A,并在数码管上显示。

3)寄存器B,第三个脉冲来时锁存数据B,并在数码管上显示。

4)8位ALU,第四个脉冲来时进行运算,并锁存结果alu_out。

5)结果显示器,将结果显示通过DE2上的数码管显示。

四.程序分析:

主程序模块:

modulealu8(clk,clk_r,rst,a,b,alu_out,opcode,sw_ab,HEX1, HEX0,HEX7, HEX6, HEX5,HEX4);

input clk,rst,clk_r;

input[7:

0]sw_ab;

input[2:

0]opcode;

output[6:

0] HEX1,HEX0,HEX7,HEX6, HEX5, HEX4;

output [7:

0]a;

output[7:

0] b;

output[7:

0]alu_out;

regaU1(.clk(clk),.rst(rst),.sw_ab(sw_ab),.a_r(a),.clk_r(clk_r),.HEX7(HEX7),.HEX6(HEX6));

regbU2(.clk(clk),.rst(rst),.sw_ab(sw_ab),.b_r(b),.clk_r(clk_r),.HEX5(HEX5),.HEX4(HEX4));

alurU3(.clk(clk),.rst(rst),.a_r(a),.b_r(b),.alu_out(alu_out),.opcode(opcode));

digitalU4(.clk_r(clk_r),.rst(rst),.alu_out(alu_out),.HEX1(HEX1),.HEX0(HEX0));

endmodule

第一位数A模块:

modulerega (clk,clk_r,rst,sw_ab,a_r,HEX7,HEX6);

input[7:

0]sw_ab;

inputclk,clk_r,rst;

0]a_r;

reg[7:

0]a_r;

outputreg[6:

0]HEX7,HEX6;

reg[3:

0]cnt;

always@(posedgeclkornegedge rst)

if(!

rst)cnt<=1'd0;

elseif(cnt==5)cnt<

=1'

d0;

elsecnt<=cnt+1'

d1;

always@(posedgeclkornegedgerst)

ﻩif(!

rst)a_r=0;

else if(cnt==1)a_r=sw_ab;

elsea_r=a_r;

parameter seg0=7'b1000000,

seg1=7'b1111001,seg2=7'

b0100100,seg3=7'

b0110000,seg4=7'

b0011001,seg5=7'b0010010,seg6=7'

b0000010,

seg7=7'

b1111000,seg8=7'

b0000000,seg9=7'

b0010000,sega=7'

b0001000,segb=7'

b0000011,segc=7'

b1000110,

segd=7'

b0100001,sege=7'b0000110,segf=7'

b0001110;

always@(posedgeclk_r)

case(a_r[3:

0])

4'

h0:

HEX6[6:

0]=seg0;

h1:

HEX6[6:

0]=seg1;

4'h2:

HEX6[6:

0]=seg2;

h3:

HEX6[6:

0]=seg3;

4'h4:

HEX6[6:

0]=seg4;

h5:

HEX6[6:

0]=seg5;

4'

h6:

HEX6[6:

0]=seg6;

h7:

0]=seg7;

4'h8:

HEX6[6:

0]=seg8;

h9:

HEX6[6:

0]=seg9;

ha:

0]=sega;

4'hb:

HEX6[6:

0]=segb;

hc:

HEX6[6:

0]=segc;

hd:

HEX6[6:

0]=segd;

4'he:

HEX6[6:

0]=sege;

hf:

HEX6[6:

0]=segf;

default:

HEX6[6:

0]=seg0;

endcase

always@(posedgeclk_r)

case(a_r[7:

4])

h0:

HEX7[6:

0]=seg0;

h1:

HEX7[6:

0]=seg1;

h2:

HEX7[6:

0]=seg2;

h3:

HEX7[6:

0]=seg3;

h4:

HEX7[6:

0]=seg4;

h5:

HEX7[6:

0]=seg5;

h6:

HEX7[6:

0]=seg6;

h7:

HEX7[6:

0]=seg7;

h8:

HEX7[6:

0]=seg8;

4'h9:

HEX7[6:

0]=seg9;

4'ha:

HEX7[6:

0]=sega;

hb:

0]=segb;

0]=segc;

hd:

HEX7[6:

0]=segd;

he:

HEX7[6:

0]=sege;

hf:

HEX7[6:

0]=segf;

default:

HEX7[6:

0]=seg0;

endcase

endmodule

第二位数B模块:

moduleregb(clk,clk_r,rst,sw_ab,b_r,HEX5,HEX4);

input[7:

0]sw_ab;

inputclk,clk_r,rst;

output [7:

0]b_r;

reg[7:

0]b_r;

outputreg[6:

0] HEX5,HEX4;

reg[3:

0] cnt;

always@(posedgeclkornegedgerst)

rst)cnt<

=1'

d0;

else if(cnt==5) cnt<

d0;

elsecnt<=cnt+1'

d1;

always@(posedgeclkornegedgerst)

ﻩif(!

rst)b_r=0;

elseif(cnt==2)b_r=sw_ab;

elseb_r=b_r;

parameter seg0=7'

b1000000,

seg1=7'

b1111001, seg2=7'b0100100,seg3=7'

b0110000,seg4=7'

b0011001,seg5=7'

b0010010,seg6=7'b0000010,

seg7=7'b1111000,seg8=7'

b0000000,seg9=7'

b0010000,sega=7'b0001000,segb=7'

b0000011,segc=7'b1000110,

segd=7'

b0100001,sege=7'b0000110,segf=7'

b0001110;

always@(posedge clk_r)

case(b_r[3:

0])

HEX4[6:

0]=seg0;

h1:

HEX4[6:

0]=seg1;

4'h2:

HEX4[6:

0]=seg2;

h3:

HEX4[6:

0]=seg3;

4'h4:

HEX4[6:

0]=seg4;

HEX4[6:

0]=seg5;

4'h6:

HEX4[6:

0]=seg6;

0]=seg7;

h8:

HEX4[6:

0]=seg8;

4'h9:

HEX4[6:

0]=seg9;

0]=sega;

HEX4[6:

0]=segb;

hc:

HEX4[6:

0]=segc;

hd:

HEX4[6:

0]=segd;

he:

HEX4[6:

0]=sege;

hf:

HEX4[6:

0]=segf;

default:

HEX4[6:

0]=seg0;

always@(posedgeclk_r)

case(b_r[7:

h0:

HEX5[6:

0]=seg0;

h1:

HEX5[6:

0]=seg1;

4'h2:

HEX5[6:

0]=seg2;

4'h3:

HEX5[6:

0]=seg3;

h4:

HEX5[6:

0]=seg4;

h5:

HEX5[6:

0]=seg5;

4'h6:

HEX5[6:

0]=seg6;

4'h7:

HEX5[6:

0]=seg7;

HEX5[6:

0]=seg8;

h9:

0]=seg9;

HEX5[6:

0]=sega;

HEX5[6:

0]=segb;

HEX5[6:

4'hd:

HEX5[6:

0]=segd;

he:

HEX5[6:

0]=sege;

4'hf:

HEX5[6:

0]=segf;

default:

HEX5[6:

0]=seg0;

endcase

endmodule

运算模块:

modulealur(clk,rst,alu_out,a_r,b_r,opcode,zero);

output [7:

0]alu_out;

outputzero;

input [7:

0]a_r,b_r;

input[2:

0]opcode;

input clk,rst;

0]alu_out;

reg [3:

0]cnt;

parameterquA=3'

b000,quB=3'

b001,ADD=3'

b010,DEC=3'

b011,ANDD=3'

b100,XORR=3'

b101,XOR=3'b110,NXOP=3'b111;

assignzero=!

a_r;

always@(posedge clk or negedgerst)

if(!

rst) cnt<

=1'd0;

elseif(cnt==5)cnt<=1'

elsecnt<

=cnt+1'd1;

always@(posedgeclkornegedgerst)

rst)alu_out=0;

elseif(cnt==3)begin

casex(opcode)

quA:

alu_out<

=a_r;

quB:

alu_out<

=b_r;

ADD:

alu_out<

=a_r+b_r;

DEC:

alu_out<=a_r-b_r;

ANDD:

alu_out<=a_r&

b_r;

XORR:

alu_out<=a_r|b_r;

XOR:

alu_out<

=a_r^b_r;

NXOP:

alu_out<

=a_r^~b_r;

default:

alu_out<

=8'

bxxxx_xxxx;

end

elsealu_out=0;

endmodule

结果显示模块:

module digital(clk_r,rst,alu_out,HEX1,HEX0);

input [7:

0] alu_out;

inputclk_r,rst;

output reg[6:

0]HEX1,HEX0;

parameter seg0=7'

b1000000,

seg1=7'

b1111001,seg2=7'

b0100100,seg3=7'b0110000,seg4=7'b0011001,seg5=7'

b0010010,seg6=7'

b0000010,

seg7=7'b1111000,seg8=7'

b0000000,seg9=7'b0010000,sega=7'

b0001000,segb=7'

b0000011,segc=7'

b1000110,

segd=7'

b0100001,sege=7'

b0000110,segf=7'b0001110;

always@(posedgeclk_r)

case(alu_out[3:

h0:

HEX0[6:

0]=seg0;

HEX0[6:

0]=seg1;

HEX0[6:

0]=seg2;

h3:

HEX0[6:

0]=seg3;

HEX0[6:

0]=seg4;

HEX0[6:

0]=seg5;

HEX0[6:

0]=seg6;

h7:

HEX0[6:

0]=seg7;

HEX0[6:

0]=seg8;

HEX0[6:

0]=seg9;

ha:

HEX0[6:

0]=sega;

HEX0[6:

0]=segb;

hc:

0]=segc;

4'hd:

HEX0[6:

0]=segd;

HEX0[6:

0]=sege;

hf:

HEX0[6:

default:

HEX0[6:

0]=seg0;

endcase

always@(posedgeclk_r)

case(alu_out[7:

4])

h0:

HEX1[6:

0]=seg0;

4'h1:

HEX1[6:

0]=seg1;

h2:

HEX1[6:

0]=seg2;

HEX1[6:

0]=seg3;

h4:

HEX1[6:

0]=seg4;

HEX1[6:

0]=seg5;

HEX1[6:

0]=seg6;

h7:

HEX1[6:

0]=seg7;

HEX1[6:

0]=seg8;

h9:

HEX1[6:

0]=seg9;

4'ha:

0]=sega;

HEX1[6:

4'hc:

HEX1[6:

0]=segc;

hd:

HEX1[6:

he:

HEX1[6:

0]=sege;

4'hf:

0]=segf;

default:

endcase

endmodule

五.仿真实现:

整体图:

波形图:

六.硬件实现:

1.引脚图:

2.分析结果说明:

开关0~2是算法选择,具体算法类型见设计功能第2项

开关10~17数字输入,用8位二进制数表示两个十六进制数,每四位表示一位

按键0是锁存及运算,当开关10~17输入一个数A时,按下按键0,数据就是锁存,

再输入数就是数B,而当数据B也锁存后,再次按下按键0,就会显示运算结果

按键1是复位键

七.总结:

通过这次FPGA实验课让我明白了真正的编程不像是那些C语言小程序那么简单,为了这次实验算是绞尽脑汁,最后为了读懂程序,还去专门找了Verilog语言辅导书,

不管过程再怎么复杂曲折,总算是顺利的完成了实验任务,到了现在回顾为期6周的学ﻩ习过程,也有一些时候是因为上课不认真,为后来的程序设计增加了难度,也有一些原因是因为自己本身能力不足导致设计接连失败,不得不说,也有一部分原因是因为学习实验室的器件不足,限制了实验设计的范围,也使实验难度增加。

特别要感谢老师在最后实验设计时的指导,让我的这次实验能够这么顺利的完成。