数字电路实验四 利用MSI设计组合逻辑电路二Word格式文档下载.docx

《数字电路实验四 利用MSI设计组合逻辑电路二Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《数字电路实验四 利用MSI设计组合逻辑电路二Word格式文档下载.docx(9页珍藏版)》请在冰豆网上搜索。

1.熟悉编码器.译码器数据选择器等组合逻辑功能模块的功能与使用方法。

2掌握用MSI设计组合逻辑电路的方法.

二、实验器件

1.数字电路实验箱数字万用表、示波器。

2.虚拟器件:

74LS151,74LS00.

三、实验预习

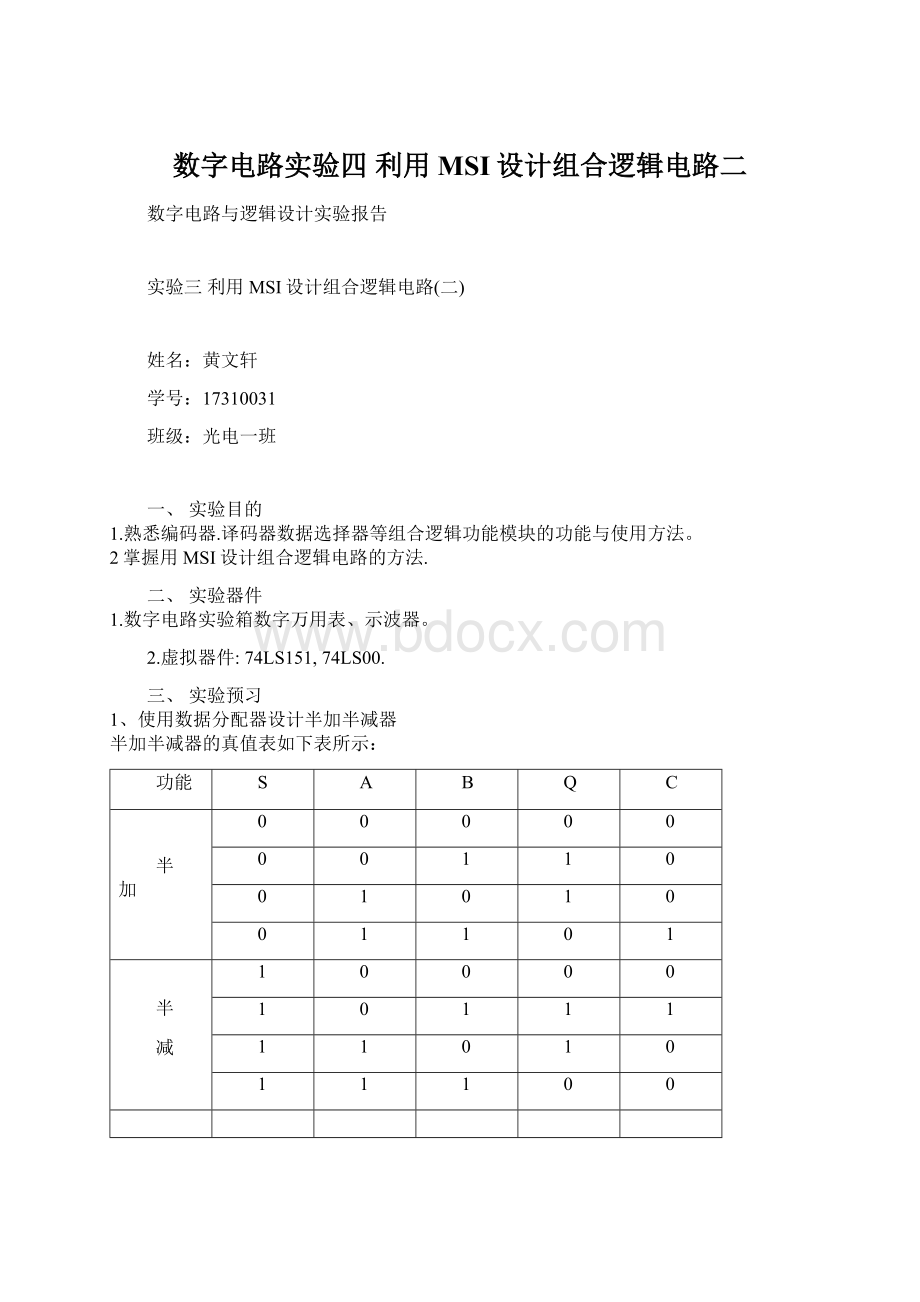

1、使用数据分配器设计半加半减器

半加半减器的真值表如下表所示:

功能

S

A

B

Q

C

半

加

1

减

考虑到数据选择器的特性是根据传入的地址选择对应的数据,所以我们可以将S、A、B作为地址输入到74LS151的S2、S1、S0选择输入端,根据真值表的要求为D0~D7的数据输入端赋值(与高/低电平相连),即可实现预期功能。

由于有两种不同的输出,我们需要两块74LS151来实现。

电路连接图如下所示:

使用Multisum仿真检验正确性,以74LS197作为动态输入观察输出波形,仿真结果如下图所示:

波形可以与真值表对应,我们判断这种电路接法是有效正确的。

二、使用74LS151设计逻辑单元

逻辑单元的真值表如下图所示:

输入

输出

S1

S0

Y

74LS151输入端有三个,而目标逻辑单元有四个输入端,我们可以借助芯片的八个数据输入端置入第四个输入。

考虑对S1、S0、A的任一状态,输出Y可以表示为Y=f(B)的函数形式,因此只需要对每个状态,把B按照对应的逻辑接在D0~D7的数据输入端即可。

每个地址对应的逻辑如下表所示:

地址输入端

Y=f(B)

——B

这样我们可以得到使用一个与非门和74LS151芯片实现的逻辑单元,其电路图如下:

同样实现了目标的逻辑功能,我们判断这种接法有效正确。

四、实验内容

1、具体内容

1AU(ArithmeticUnit,算术单元)设计,在实验箱上实现。

设计一个半加半减器,输入为S、A、B,其中S为功能选择口。

当S-0时输出A+B及进位:

当S=1时,输出A-B及借位。

使用74LS151实现,可分两次连线单独记录和/差结果、进/借位结果,或使用两块74LS151实现。

2LU(LogicUnit,逻辑单元)设计,在实验箱上实现。

用八选一数据选择器151设计一个函数发生器电路。

待静态测试检查电路工作正常后,进行动态测试。

将74LS197连接成十六进制作为电路的输入信号源,用示波器观察并记录CP、S1、S0、A、B、Y的波形

2、设计过程

①因为实验中要用到两块74LS151芯片,我们把它们命名为74LS151A和74LS151B。

将74LS151A、74LS151B的S2、S1、S0端口作为输入端S、A、B,选通输入端—E接低电平,数据输入端D0~D7接恒定电压。

74LS151A的D0、D3、D4、D7接低电平,D1、D2、D5、D6接高电平,74LS151B的D0、D1、D2、D4、D6、D7接低电平,D3、D5接高电平。

这样,74LS151A的数据输出端Z输出和\差结果Q,74LS151B的数据输出端Z就输出进\借位结果C。

②将74LS151芯片的S2、S1、S0端口作为输入端A、S1、S0,选通输入端—E接低电平,D0、D7接低电平,D3、D6接高电平,D1、D2、D4接输入端B,输入端B接入反相器(使用74LS00的一个输入端,另一输入端接高电平),反相器的输出接入D5。

这样,74LS151的数据输出端Z输出逻辑单元的运算结果Y。

五、

测试过程

①由于器件不足,这里只使用了一块74LS151芯片,分两次记录和\差结果Q和进\借位结果C。

实验接线图:

使用74LS197作为动态输入信号,记录动态输出

动态测试波形图:

和\差结果Q

波形从上到下依次是和差结果Q,动态输入Q2、Q1、Q0。

进\借位结果C

波形从上到下依次是进\借位结果C,动态输入Q2、Q1、Q0。

可以看到,实验波形与理论仿真得到的波形一致,再次证明了我们接法的正确性。

该种接法相对于前两种实现方式较容易设计(不需要对逻辑表达式化简,只需要将真值表用固定电平表示出来),但相对接线也比较复杂,使用的器件数目也较多,与其他方法互有优劣

2实验接线图:

实验波形图:

波形从上到下依次是时钟信号、输入信号B、输入信号A、功能控制信号S0、功能控制信号S1、输出运算结果Y。

从图中容易看出S1=0,S0=0时执行与门效果,S1=0,S0=1时执行或门效果,S1=1,S0=0时执行异或门效果,S1=1,S0=1时执行反相器效果。

与仿真结果也一致,判断设计出的逻辑单元正常工作。

此外,明显可以看出输出信号中含有大量的噪声信号。

分别出现在S1、S0=01时,AB:

01->

10,S1、S0=10时,AB:

10,S1、S0=11时,AB:

10->

11。

考虑到噪声产生的原因有1、输入计数器信号在每两个状态之间存在延迟2、实验中使用的一个门电路存在传输延迟,3、74LS151的选出地址切换存在延迟。

如果是74LS151芯片的状态切换引起的延迟,那么信号A、S1、S0的每次跳动都会造成一次假信号,而波形中只有三种假信号,所以我们排除这种可能。

在S1、S0=01时,AB:

10:

芯片选择的输出端从D1切换到了D5,D1=B,D5=1.波形存在一个短暂的假0信号,简单分析后我们得出:

在地址输入(AS1S0)从001变化到101之前,B就先行从1变化到0,使得D1=B=0,造成了短暂的低电平假信号。

该传输延迟应来自于串行计数器74LS197输出的Q0、Q1间的延迟(即A、B间的延迟)。

在S1、S0=10时,AB:

芯片选择的输出端从D2切换到了D6,D2=B,D6=—B.波形存在一个短暂的假0信号,简单分析后我们得出:

在地址输入(AS1S0)从010变化到110之后,由于74LS00的传输延迟,此时D6=—B还处在B=1的状态,即D6=0,这就会造成一个短暂的低电平假信号。

待B=0的信号通过门电路到达D6时,D6恢复正常状态D6=1.

在S1、S0=11时,AB:

11:

芯片选择的输出端不发生改变,两个状态选择的输出端都是D7。

波形存在一个短暂的假1信号.而实验中D7始终接低电平,该假信号理论上不应出现。

分析后,我判断是由实验时,实验箱的多个低电平引脚接在了不同的地方,D7有可能受电路的其他部分影响,不恒为低电平。

六、总结

①本实验使用了数据选择器来实现一些功能,帮助我理解了数据选择器的工作原理,也让我了解了数据选择器的高度灵活性,可广泛应用于多功能电路的设计。

②实验后分析实验数据的过程提高了我分析异常,排除故障的能力。

③实验中串行计数器的使用和门电路的存在都使得输出信号存在少许的噪声,在工程设计中应使用尽可能少的门电路,既能节约成本,又能提升电路性能。

4实验接线前设计电路时,不同的逻辑化简方法会得到完全不同的电路(如实验二中将S1,S0,A,B中哪三者作为地址输入端),其复杂度和性能也会有所不同。

因此正式实验前,应尽可能尝试所有可能的设计方案,取最优解。