eda实验报告Word格式文档下载.docx

《eda实验报告Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《eda实验报告Word格式文档下载.docx(19页珍藏版)》请在冰豆网上搜索。

fb

bin

sum

B

e

u3

cin

u2

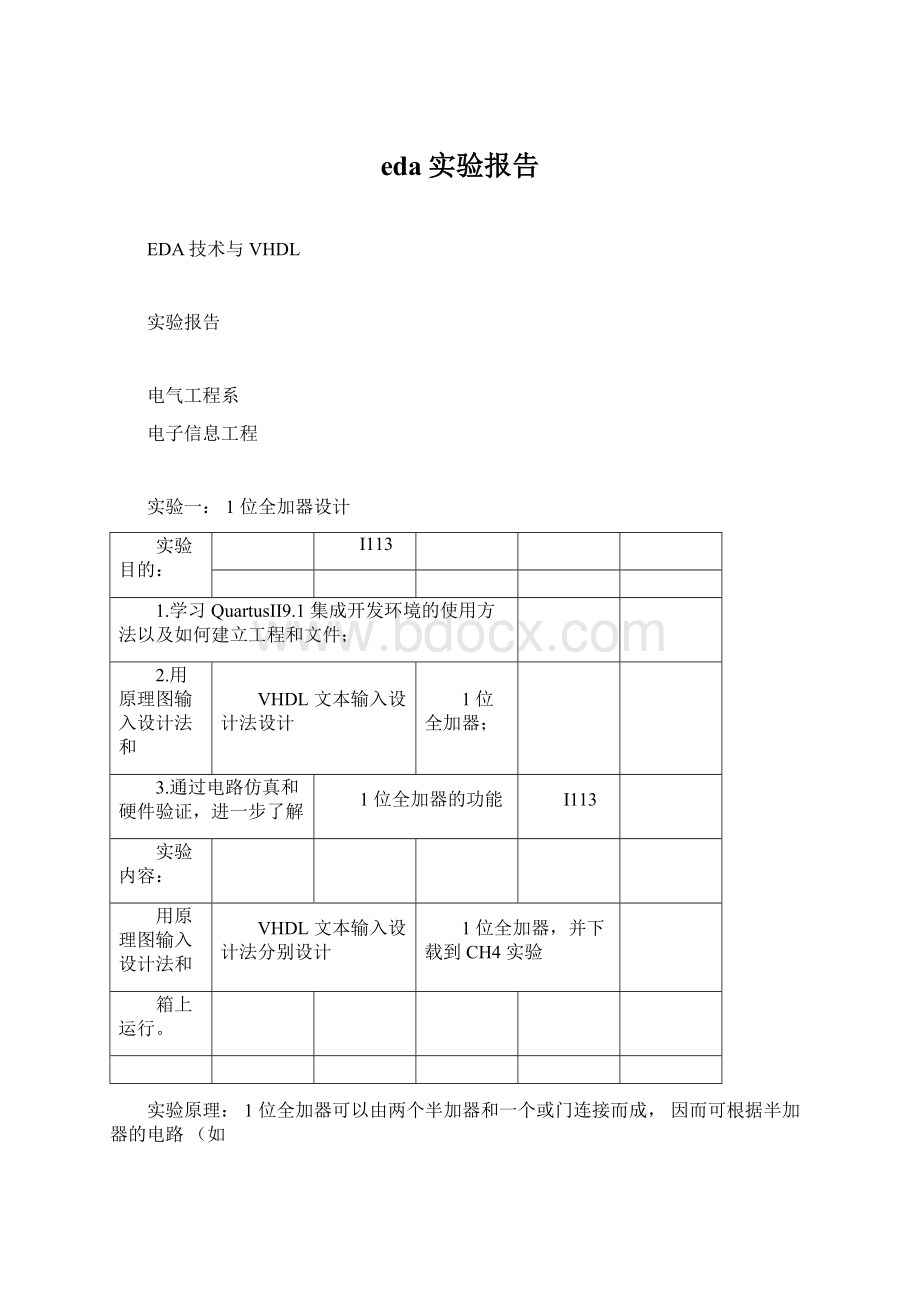

图3-2全加器f_adder电路图及其实体模块

实验步骤:

1.打开实验箱电源;

2.输入移位寄存器VHDL程序;

3.点击图标,进行分析和综合;

4.建立波形文件,进行功能仿真;

5.按接线图配置FPGA引脚;

6.点击图标,进行编译;

7.下载****.sof配置文件到EP3C16Q240C8中;

1半加器的vhdl描述有两种,我用的是下面这种,布尔函数描述法:

(1)布尔函数描述方法的VHDL源程序如下:

LIBRARYIEEE;

--半加器描述

(1):

布尔方程描述方法

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYh_adderIS

PORT(a,b:

INSTD_LOGIC;

co,so:

OUTSTD_LOGIC);

ENDENTITYh_adder;

ARCHITECTUREfh1OFh_adderis

BEGIN

so<

=NOT(aXOR(NOTb));

co<

=aANDb;

ENDARCHITECTUREfh1;

(2)或门逻辑描述:

LIBRARYIEEE;

--或门逻辑描述

ENTITYor2aIS

INSTD_LOGIC;

c:

OUTSTD_LOGIC);

ENDENTITYor2a;

ARCHITECTUREoneOFor2aIS

c<

=aORb;

ENDARCHITECTUREone;

(3)1位二进制全加器顶层设计描述:

--1位二进制全加器顶层设计描述

ENTITYf_adderIS

PORT(ain,bin,cin:

cout,sum:

ENDENTITYf_adder;

ARCHITECTUREfd1OFf_adderIS

COMPONENTh_adder--调用半加器声明语句

PORT(a,b:

co,so:

ENDCOMPONENT;

COMPONENTor2a

PORT(a,b:

ENDCOMPONENT;

SIGNALd,e,f:

STD_LOGIC;

--定义3个信号作为内部的连接线。

:

h_adderPORTMAP(a=>

ain,b=>

bin,co=>

,so=>

e);

--例化语句

h_adderPORTMAP(a=>

e,

b=>

cin,co=>

f,so=>

sum);

or2aPORTMAP(a=>

d,

f,c=>

cout);

ENDARCHITECTUREfd1;

实验结果:

实验二:

移位寄存器模块

1设计8位CPU设计中常用的移位寄存器模块

2用case语句设计并行输入输出的移位寄存器

3体会信号赋值的特性

实验内容:

编写移位寄存器的VHDL实现程序;

通过电路仿真和硬件验证,进一步了解移位寄存器的功能。

设计原理:

LibraryIEEE;

ENTITYSHIFTIS

PORT(CLK,C0:

--时钟和进位输入

MD:

INSTD_LOGIC_VECTOR(2DOWNTO0);

--移位模式控制字

D:

INSTD_LOGIC_VECTOR(7DOWNTO0);

--待加载移位的数据

QB:

OUTSTD_LOGIC_VECTOR(7DOWNTO0);

移--位数据输出

CN:

--进位输出

ENDENTITY;

ARCHITECTUREBEHAVOFSHIFTIS

SIGNALREG:

STD_LOGIC_VECTOR(7DOWNTO0);

SIGNALCY:

STD_LOGIC;

PROCESS(CLK,MD,C0)

IFCLK‘EVENTANDCLK=’1‘THEN

CASEMDIS

WHEN"

001"

=>

REG(0)<

=C0;

REG(7DOWNTO1)<

=REG(6DOWNTO0);

CY<

=REG(7);

--带进位循环左移

010"

=REG(7);

--自循环左移

011"

REG(7)<

=REG(0);

REG(6DOWNTO0)<

=REG(7DOWNTO1);

--自循环右移

100"

=REG(0);

101"

REG(7DOWNTO0)<

=

--带进位循环右移

D(7DOWNTO0);

--加载待移数

WHENOTHERS=>

REG<

=REGCY;

<

=CY;

--保持

ENDCASE;

ENDIF;

ENDPROCESS;

QB(7DOWNTO0)<

=REG(7DOWNTO0);

CN<

=CY;

--移位后输出

ENDBEHAV;

实验三:

计数器和移位寄存器设计

一、十进制加法计数器

设计带有异步复位和同步时钟使能的十进制加法计数器。

编写十进制加法计数器的VHDL实现程序;

通过电路仿真和硬件验证,了解变量的使用方法,以及“(OTHERS=>

X)”的使用方法。

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNT10IS

PORT(CLK,RST,EN:

CQ:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT:

ENDCNT10;

ARCHITECTUREbehavOFCNT10IS

PROCESS(CLK,RST,EN)

VARIABLECQI:

STD_LOGIC_VECTOR(3DOWNTO0);

IFRST='

1'

THENCQI:

=(OTHERS=>

'

0'

);

--计数器异步复位

ELSIFCLK'

EVENTANDCLK='

THEN--检测时钟上升沿

IFEN='

THEN--检测是否允许计数(同步使能)

IFCQI<

9THENCQI:

=CQI+1;

--允许计数,检测是否小于

ELSECQI:

);

--大于9,计数值清零

IFCQI=9THENCOUT<

='

;

--计数大于9,输出进位信号

ELSECOUT<

CQ<

=CQI;

--将计数值向端口输出

ENDPROCES

ENDbehav;

9

2.输入移位寄存器

VHDL程序;

1、引脚图:

二、移位寄存器设计

设计带有同步并行预置功能的8位右移移位寄存器。

CLK是移位时钟信号,DIN是8位并行预置数据端口,LOAD是并行数据预置使能信号,

QB是串行输出端口

ENTITYSHFRTIS--8位右移寄存器

PORT(CLK,LOAD:

DIN:

INSTD_LOGIC_VECTOR(7DOWNTO0);

ENDSHFRT;

ARCHITECTUREbehavOFSHFRTIS

IFLOAD='

THENREG8:

=DIN;

--由(LOAD='

)装载新数据

ELSEREG8(6DOWNTO0):

=REG8(7DOWNTO1);

QB<

=REG8(0);

--输出最低位

2.输入移位寄存器VHDL程序;

实验四:

七段数码显示译码器和数控分频器设计

一.七段数码显示译码器

学习7段数码显示译码器设计;

学习VHDL的CASE语句应用及多层次设计方法。

在QuartusII上对该例进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。

提示:

用输入总线的方式给出输入信号仿真数据,仿真波形示例下图所示。

引脚锁定及硬件测试

7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制

BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制

的,为了满足16进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实

现。

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDECL7SIS

PORT(A:

INSTD_LOGIC_VECTOR(3DOWNTO0);

LED7S:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

END;

ARCHITECTUREoneOFDECL7SIS

PROCESS(A)

CASEAIS

0000"

LED7S<

="

0111111"

;

0001"

0000110"

0010"

1011011"

0011"

1001111"

0100"

1100110"

0101"

1101101"

0110"

1111101"

0111"

0000111"

1000"

1111111"

1001"

1101111"

1010"

1110111"

1011"

1111100"

1100"

0111001"

1101"

1011110"

1110"

1111001"

1111"

1110001"

NULL;

ENDCASE;

ENDPROCESS;

二.数控分频器设计

学习数控分频器的设计、分析和测试方法。

。

根据波形图,分析VHDL中的各语句功能、设计原理及逻辑功能,详述进程P_REG和P_DIV的作用,并画出该程序的RTL电路图。

输入不同的CLK频率和预置值D,给出时序波

形。

在实验系统上硬验证。

给出不同输入值

D时,FOUT输出不同频率

数控分频器的功能就是当在输入端给定不同输入数据时,将对输入的时钟信号有不同的

分频比,数控分频器就是用计数值可并行预置的加法计数器设计完成的,方法是将计数溢出

位与预置数加载输入信号相接即可。

ENTITYDVFIS

PORT(CLK:

FOUT:

END;

ARCHITECTUREoneOFDVFIS

SIGNALFULL:

P_REG:

PROCESS(CLK)

VARIABLECNT8:

IFCLK'

EVENTANDCLK='

THEN

IFCNT8="

11111111"

CNT8:

=D;

--当CNT8计数计满时,输入数据

D被同步预置给计

--数器CNT8

FULL<

--同时使溢出标志信号FULL输出为高电平

ELSECNT8:

=CNT8+1;

--否则继续作加1计数

--且输出溢出标志信号FULL为低电平

ENDPROCESSP_REG;

P_DIV:

PROCESS(FULL)

VARIABLECNT2:

IFFULL'

EVENTANDFULL='

CNT2:

=NOTCNT2;

--如果溢出标志信号FULL为高电平,D触发器输出取反

IFCNT2='

THENFOUT<

ELSEFOUT<

ENDPROCESSP_DIV;

实验五:

单进程Moore状态机

测试单进程Moore状态机。

在QuartusII上对该例进行编辑、编译、综合、适配、仿真,给出单进程状态机的工作时序,分析本实例VHDL程序。

ENTITYMOORE1IS

PORT(DATAIN:

INSTD_LOGIC_VECTOR(1DOWNTO0);

CLK,RST:

Q:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDMOORE1;

ARCHITECTUREbehavOFMOORE1IS

TYPEST_TYPEIS(ST0,ST1,ST2,ST3,ST4);

SIGNALC_ST:

ST_TYPE;

PROCESS(CLK,RST)

IFRST='

THENC_ST<

=ST0;

Q<

CASEC_STIS

WHENST0=>

IFDATAIN="

10"

=ST1;

ELSEC_ST<

ENDIF;

Q<

WHENST1=>

11"

=ST2;

WHENST2=>

01"

=ST3;

WHENST3=>

00"

=ST4;

WHENST4=>

C_ST<

=ST0;

状态转换图:

实验六:

Mealy状态机

测试Mealy状态机。

在QuartusII上对该例进行编辑、编译、综合、适配、仿真,给出两个程序实现Mealy

状态机的工作时序,分析本实例VHDL程序。

与Moore状态机相比,mealy状态机的输出变化要领先一个周期,即一段输入信号或状

态发生变化,输出信号即发生变化。

程序一是两进程Mealy型状态机。

程序二是在程序一的基础上在COM1的进程中增加了一个IF语句,由此产生一个锁存

器,Q输出的时序是一致的,没有发生锁存后延时一个周期的现象。

测试两种实现方式的工作时序。

VHDL程序一:

ENTITYMEALY1IS

PORT(CLK,DATAIN,RESET:

OUTSTD_LOGIC_VECTOR(4DOWNTO0));

ENDMEALY1;

ARCHITECTUREbehavOFMEALY1IS

TYPEstatesIS(st0,st1,st2,st3,st4);

SIGNALSTX:

states;

COMREG:

PROCESS(CLK,RESET)BEGIN--决定转换状态的进程