项目八计数器.docx

《项目八计数器.docx》由会员分享,可在线阅读,更多相关《项目八计数器.docx(32页珍藏版)》请在冰豆网上搜索。

项目八计数器

项目八计数器

【案例导入】装箱流水线

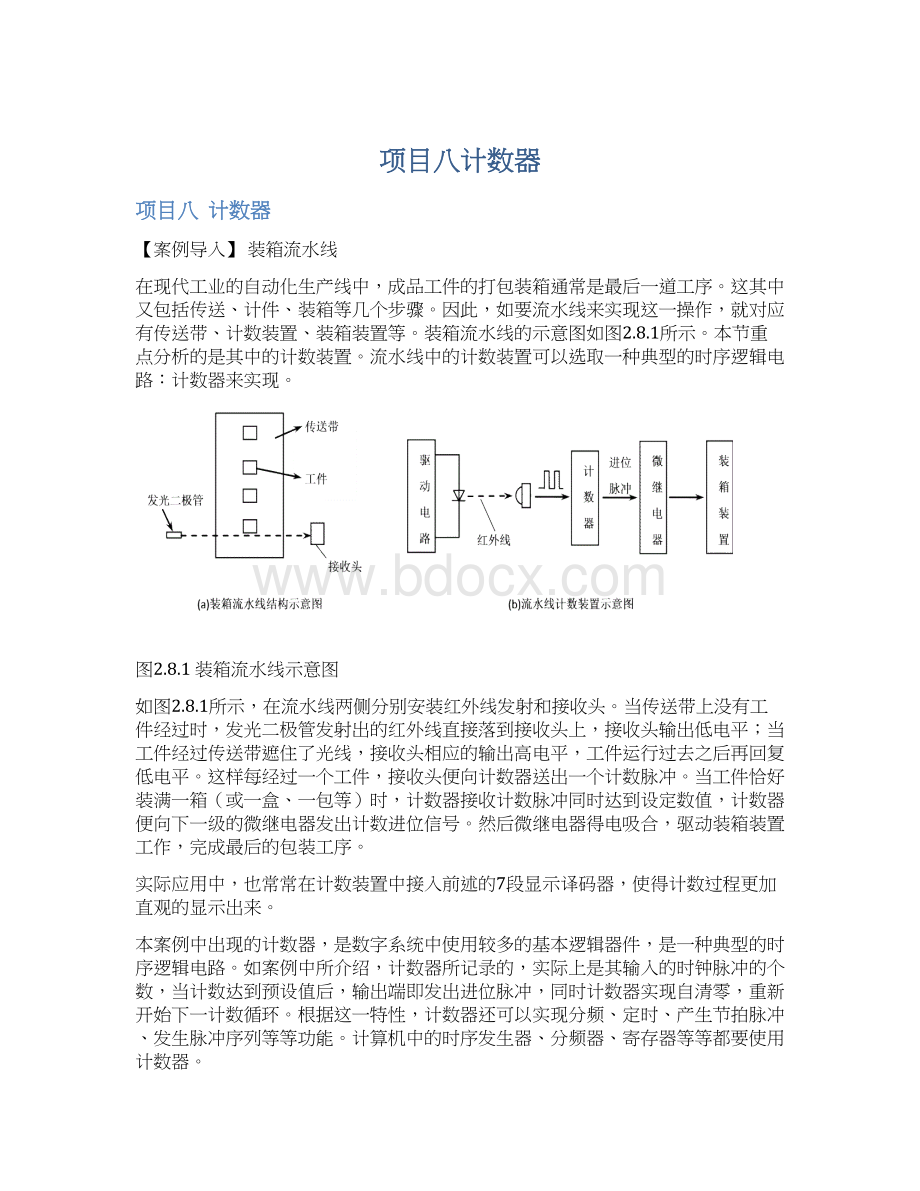

在现代工业的自动化生产线中,成品工件的打包装箱通常是最后一道工序。

这其中又包括传送、计件、装箱等几个步骤。

因此,如要流水线来实现这一操作,就对应有传送带、计数装置、装箱装置等。

装箱流水线的示意图如图2.8.1所示。

本节重点分析的是其中的计数装置。

流水线中的计数装置可以选取一种典型的时序逻辑电路:

计数器来实现。

图2.8.1装箱流水线示意图

如图2.8.1所示,在流水线两侧分别安装红外线发射和接收头。

当传送带上没有工件经过时,发光二极管发射出的红外线直接落到接收头上,接收头输出低电平;当工件经过传送带遮住了光线,接收头相应的输出高电平,工件运行过去之后再回复低电平。

这样每经过一个工件,接收头便向计数器送出一个计数脉冲。

当工件恰好装满一箱(或一盒、一包等)时,计数器接收计数脉冲同时达到设定数值,计数器便向下一级的微继电器发出计数进位信号。

然后微继电器得电吸合,驱动装箱装置工作,完成最后的包装工序。

实际应用中,也常常在计数装置中接入前述的7段显示译码器,使得计数过程更加直观的显示出来。

本案例中出现的计数器,是数字系统中使用较多的基本逻辑器件,是一种典型的时序逻辑电路。

如案例中所介绍,计数器所记录的,实际上是其输入的时钟脉冲的个数,当计数达到预设值后,输出端即发出进位脉冲,同时计数器实现自清零,重新开始下一计数循环。

根据这一特性,计数器还可以实现分频、定时、产生节拍脉冲、发生脉冲序列等等功能。

计算机中的时序发生器、分频器、寄存器等等都要使用计数器。

计数器的核心是触发器。

如前所述,一个触发器有“0”、“1”两个稳态,本身就是一个二进制的计数器。

在计数器中,有一个很重要的概念叫“模”,表示一个计数器能够记忆输入时钟脉冲的数目,又称计数容量或计数长度,其实就是指计数器电路的有效状态数,也即计数器的进制数。

若使用n个触发器构成计数器,则电路最多可以有2n个状态,因此最多可以实现2n进制计数器。

在本节案例中,假设装满一箱是8个工件,则可以选用3个触发器来构成一个8进制计数器。

流水线自0态(000状态)开始工作,每装一个工件就计入一个脉冲信号,状态改变一次。

装入8个工件后,8进制计数器自清零(回复000状态),待下一个工件到来时再进入一个工作循环。

与此同时,信号输出端发出进位脉冲,驱动后一级的电路。

计数器具体的硬件结构和工作过程在后续章节详细介绍。

【知识链接】

(一)N进制计数器

计数器的种类繁多。

按计数器有效状态数即模值的不同,可分为二进制计数器、十进制计数器和N进制计数器;按计数时是递增还是递减,可分为加法计数器、减法计数器和可逆计数器;按计数器中触发器翻转是否同步分,可分为同步计数器和异步计数器;按计数器中使用的开关元件分,可分为TTL计数器和CMOS计数器。

获得N进制计数器常用的方法通常有两种:

一是先根据需求列出状态图,再用时钟触发器和门电路进行设计。

这种方法比较繁琐,将在后续的【扩展应用】中详细介绍。

二是利用已有的集成计数器芯片来构成。

集成计数器一般都设有清零输入端和置数输入端,其中又有同步触发和异步触发之分。

例如:

清零、置数均采用同步方式的有集成4位二进制(十六进制)同步加法计数器74LS163;均采用异步方式的有集成4位二进制可逆计数器74LS193、4位二进制异步加法计数器74LS197、十进制同步可逆计数器74LS192;清零采用异步方式、置数采用同步方式的有4位二进制同步加法计数器74LS161,十进制同步加法计数器74LS160;十进制计数器74LS290则具有异步清零、异步置“9”的功能。

本书模块三中还附有十进制同步计数器的仿真应用实例。

在利用集成计数器获得N进制计数器时,应注意每种集成芯片的不同功能,选择合适的芯片,利用清零端和置数端的反馈归零来实现任意进制的计数器。

(二)常用集成计数器

1.集成4位二进制同步加法计数器:

74LS161

74LS161是集成4位二进制同步加法计数器,其工作原理与前面介绍的几种计数器并无区别,最多可以实现24=16进制功能。

为了使用和功能扩展的方便,在制作集成电路时,增加了一些辅助功能,其电路图如图2.8.2所示。

图2.8.2集成计数器74LS161

图中CP是输入计数脉冲;

是清零端,在所有引脚中优先级别最高;

是置数控制端;CTP和CTT是两个计数器工作状态控制端;D0~D3是并行输入数据端;CO是进位信号输出端;Q0~Q3是计数器状态输出端。

表2.8.1所示是集成计数器74LS161的状态表。

表2.8.174LS161的状态表

输入

输出

CTP

CTT

CP

D0

D1

D2

D3

CO

0

×

×

×

×

×

×

×

×

0

0

0

0

0

1

0

×

×

↑

d0

d1

d2

d3

d0

d1

d2

d3

1

1

1

1

↑

×

×

×

×

计数

1

1

0

×

×

×

×

×

×

保持

1

1

×

0

×

×

×

×

×

保持

0

由表2.8.1所示状态表可以清楚地看出,在实际应用中,集成电路的几个辅助功能端按照优先级别的从高到低依次是:

清零端

,置数控制端

,两个计数器工作状态控制端CTP和CTT。

集成4位二进制同步加法计数器74LS161具有以下功能:

(1)、异步清零功能

当

=0时,计数器清零,使得

。

从表中可看出,只要

=0时,其它输入信号均不起作用。

(2)、同步并行置数功能

当没有清零信号输入,即

=1时,置数信号才能起作用。

当

=0时,在CP上升沿作用下,并行输入数据d0~d3进入计数器,使

。

(3)、二进制同步加法计数功能

当

=

=1时,若两个计数器工作状态控制端CTP=CTT=1,则计数器在CP信号上升沿控制下按照8421编码进行加法计数。

(4)、保持功能

当

=

=1时,若CTP•CTT=0,也就是说两个计数器工作状态控制端至少有一个为0时,计数器将保持原状态不变。

对于进位输出信号CO,若CTT=0,则CO=0;若CTT=1,则

。

综上所述可知,表2.8.1反映了74LS161是一个具有异步清零、同步置数、可保持状态不变的4位二进制(十六进制)同步加法计数器。

这里的同步和异步都是指的受CP脉冲的同步控制和异步控制。

类似的还有集成4位二进制(十六进制)同步加法计数器74LS163,采用同步清零、同步置数方式。

其逻辑功能、计数工作原理和外引线排列与74LS161没有大的区别。

74LS160是集成十进制同步计数器,采用异步清零、同步置数方式。

2.集成4位二进制异步加法计数器:

74LS197

图2.8.3是74LS197的结构框图。

图中

是异步清零端;

是计数和置数控制端;CP0和CP1是两组时钟脉冲输入端;D0~D3是并行输入数据端;Q0~Q3是计数器状态输出端。

图2.8.3集成计数器74LS197结构框图

74LS197各个引脚的功能与前面介绍的集成4位二进制同步加法计数器74LS161的对应引脚的功能相同。

值得注意的是:

该集成电路有两组CP输入端,其内部包括两组相对独立的计数器,即为图2.8.3中的计数器A、计数器B。

若将CP加在CP0端,再把Q0与CP1连接起来,则实现了计数器A、B的级联,构成4位二进制即十六进制异步加法计数器,如图2.8.3、2.8.4所示;若将CP加在CP0端,CP1端接地或置1,则仅有计数器A工作,构成1位二进制即二进制异步加法计数器,如图2.8.3、2.8.5所示;若将CP加在CP1端,CP0端接地或置1,则仅有计数器B工作,构成3位二进制即八进制异步加法计数器,如图2.8.3、2.8.6所示。

因此,也把74LS197称为二-八-十六进制计数器。

图2.8.4用74LS197构成十六进制计数器

图2.8.5用74LS197构成二进制计数器

图2.8.6用74LS197构成八进制计数器

74LS197具有以下功能:

(1)、清零功能

当

=0时,计数器异步清零。

(2)、置数功能

当

=1、

时,计数器异步置数。

(3)、二进制异步加法计数功能

当

=1、

时,异步加法计数。

此时可以实现如前所述的二—八—十六进制功能。

由此也可知,

端的优先级要高于

端。

集成计数器74LS197状态表可参见74LS161状态表。

类似的应用还有同步十进制可逆计数器74LS190,采用同步置数。

同步十六进制可逆计数器74LS191,采用同步置数。

所谓可逆计数器,是既可实现加法计数也可实现减法计数。

3.集成十进制异步计数器:

74LS290

图2.8.7是74LS290的结构框图。

图中CP0和CP1是两组时钟脉冲输入端;Q0~Q3是计数器状态输出端;S9包括两个并行端口,是置“9”端;R0包括两个并行端口,是清零端。

图2.8.7集成计数器74LS290结构框图

表2.8.274LS290的状态简表

输入

输出

备注

R0

S9

CP

1

0

×

0

0

0

0

清零

×

1

×

1

0

0

1

置9

0

0

↓

计数

当

,

时,计数器计数。

根据不同的连接方法,74LS290可实现二进制、五进制和十进制计数,具体可以参照集成计数器74LS197。

因此,74LS290又可称为二—五—十进制计数器。

集成十进制异步计数器74LS290具有以下功能:

(1)、异步清零功能

当

时,若

,则计数器清零,并与CP无关。

(2)、异步置“9”功能

当

时,计数器置“9”,即被置成1001的状态。

置“9”功能也与CP无关,并且其优先级别高于R0。

(3)、计数功能

可实现二—五—十进制计数功能。

如令CP=CP0、Q0=CP1,则构成一十进制计数器。

(三)用常用集成计数器构成N进制计数器

1.同步清零(置数)端反馈归零法

[例2.8.1]试用74LS163构成十三进制计数器。

解:

1.写出状态SN—1的二进制代码

2.求出归零逻辑

式中

表示状态

的译码,

表示

时状态为1的各个触发器Q端的连乘。

3.画连线图

图2.8.8(a)所示为用同步清零端归零构成的十三进制同步加法计数器的连线图,D0~D3可随意处理,在此做接地处理;图2.8.8(b)所示为用同步置数端归零构成的十三进制同步加法计数器的连线图,注意此时D0~D3必须接地处理,即D0~D3接0。

图2.8.8集成计数器74LS163构成十三进制计数器

2.异步清零(置数)端反馈归零法

与方法1相比较,利用异步端归零在归零逻辑上略有不同。

利用同步端是求出

,异步端则是求出

。

究其原因,使用同步端反馈归零时,计数器从0记到

时,再计入一个脉冲,电路立即归零;而利用异步端反馈归零时,

状态再计入一个脉冲,并非马上归零,而是先转换到一个短暂的状态

,以

的译码使电路归零。

持续的时间只有大约几十纳秒,转瞬即逝而不能稳定保持,因此不构成计数器的一个有效计数状态。

因而就整个电路而言,仍构成N进制计数器,只是当

状态再计入一个脉冲后,在归零过程中,夹杂了一个

的短暂过渡状态。

但该状态必须作为归零逻辑存在,否则就无法产生异步归零信号,所以也就造成了同步端和异步端归零逻辑的差异。

[例2.8.2]试用74LS197构成十三进制计数器。

解