可消除米勒效应并提升PFC性能的折叠共源共栅结构docWord文件下载.docx

《可消除米勒效应并提升PFC性能的折叠共源共栅结构docWord文件下载.docx》由会员分享,可在线阅读,更多相关《可消除米勒效应并提升PFC性能的折叠共源共栅结构docWord文件下载.docx(9页珍藏版)》请在冰豆网上搜索。

为了解米勒效应的影响,本文将分析米勒效应是如何影响升压晶体管的输入电流的,并同时忽略时序方法。

MOSFET的内部栅极电阻(RG)(图2)可忽略不计,不在本次分析范围内。

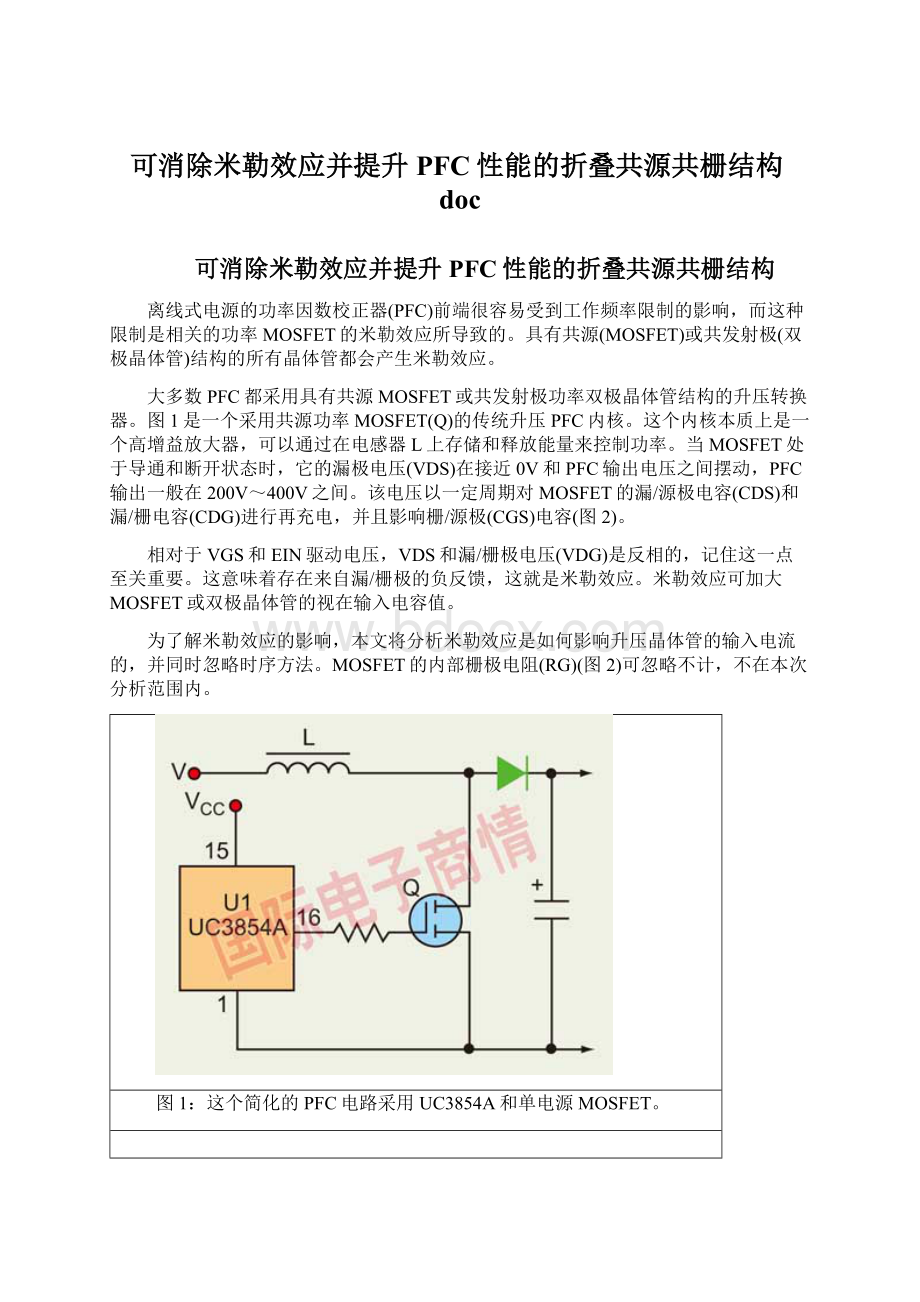

图1:

这个简化的PFC电路采用UC3854A和单电源MOSFET。

假定MOSFET为负反馈放大器,如果对其施加一个较小的步进输入(EIN),则式1成立:

dVDG=dVGS-dVDS

(1)

其中,VDG=漏/栅极电压,VGS=栅/源极电压,VDS=漏/源极电压。

它们的值都很小,因此将用这些值的微分形式进行分析,但是:

dVDS=-dID×

ZL

(2)

其中,dID=MOSFET漏极电流的变化,ZL=负载阻抗。

图2:

功率MOSFET输入电路的输入电容、电压和电流。

那么:

dID=S×

dVGS(3)

其中,S=MOSFET跨导的斜率。

将表示dID的式3代入式2,得到:

dVDS=-S×

ZL×

dVGS(4)

这里,(S×

ZL)表示MOSFET放大器的增益G,减号“-”表示负反馈,因此,

G=S×

ZL(5)

假定式5成立,则式4可表示成:

dVDS=-G×

dVGS(6)

将式6代入式1,得到dVDS的表达式:

dVDG=dVGS+G×

dVGS=dVGS×

(1+G)(7)

图3:

典型MOSFET电路的示波器曲线显示了漏极(通道1)和栅极(通道2)波形。

如图2所示,输入电流(IIN)分成以下两部分:

IGD=从MOSFET栅/漏极流过的电流

IGS=从MOSFET栅/源极流过的电流:

IIN=IGD+IGS(8)

栅/漏极电荷(QDG)的变化产生电流dIGD,因此:

IGD=dQDG/dt(9)

所以,

IGD=dQDG/dt=CDG×

dVDG/dt(10)

或者假设式7成立,可得

(1+G)×

dVGS/dt(11)

图4:

在PFC电路的MOSFET的漏极(通道1)和栅极(通道2)波形的示波器曲线中,在漏极电压减小和栅极信号增加之间明显存在一个特殊的延迟。

漏极电压的变化是由栅极信号仍为零时的谐振电路操作而引起的,因此这种变化不会影响栅极电压。

并且,

IGS=CGS×

dVGS/dt(12)

因此,

IIN=CDG×

dVGS/dt+CGS×

dVGS/dt

或者

IIN=[CGS+CDG×

dVGS/dt(13)

其中,CGS+CDG×

(1+G)=CAPP是MOSFET的视在输入电容,该电容必须由输入电流IIN进行再充电。

视在电容CAPP的值可以很高,因此输入电流的值也应该很高。

图5:

在这个共源结构中,PFC电路具有折叠共源共栅MOSFET,并采用升压控制器U1,以通过电阻器驱动低压MOSFET。

IIN=CAPP×

dVGS/dt(14)

例如,对于IXYSIXFR48N50Q,MOSFET与电路器件具有如下特性:

CGS=7nF

CDG=0.230nF

S=30

ZL=230Ω(PFCinductorinductance)

ZL=230Ω(PFC电感器的电感)

L=300µ

H(工作频率为125kHz),所以

ZL=30×

236=7000

并且

CAPP=0.230×

(1+7000)+7=1.617(µ

F)

很明显,输入电流必须在工作频率为0.15V/ns或150V/µ

s时对该电容再充电。

并且,从式14可以得到,IIN为242.5A。

实际上,当电压VGS和VDS变化时,CDG和CDS的变化量可能超过一个数量级或者更多(当电压从0上升到40V时,电容大幅降低)。

IIN的平均值可能不会很大,但是可能会出现10A~20A的瞬时电流。

MOSFET驱动器无法产生这么大的电流,这种大电流会使MOSFET的栅极驱动产生大家熟知的“高原”特性(图3)。

图6:

采用共栅结构的MOSFET的等效电路图。

因此,米勒效应使视在电容CDG的值增加N倍(N=MOSFET放大器的增益-1,可能为数千数量级)。

这个已定的负反馈将大大缩短MOSFET的开关过程,从而导致栅/源信号时序图中的“高原”现象(图3)。

米勒效应将限制升压转换器(PFC)的工作频率远低于IC和MOSFET的频率指标。

图7:

在与折叠共源共栅结构相连的MOSFET的示波器曲线上没有明显的米勒效应。

通道1是Q1的漏极波形,通道2是Q1的栅极波形。

由于升压晶体管漏/源极电压(VDS)受外部谐振电路,而不是MOSFET的栅极信号(EIN)的控制,因此在零电压下进行转换有助于避免产生米勒效应。

这个方法的可靠性非常高,它需要另一个高电压MOSFET、一个谐振电感器、两个高压二极管和少量吸收器件(snubbingcomponent),这些吸收器件可以抑制由额外的整流二极管、电感器及其杂散参数引起的寄生震荡。

功率大于800W的电源可以采用这种类型的PFC。

图4是栅极驱动和漏极电压的波形图。

图8:

折叠共源共栅结构PFC电路的示波器曲线显示了Q2的漏极波形(通道1)以及Q1的栅极波形(通道2)。

对较小的功率比应用来说,折叠共源共栅结构可能是理想选择。

这是一个容易实现并且廉价的解决方案,由于不存在米勒效应,因此该方案有助于大幅提高PFC的工作频率。

ScotLester的论文提出了一个很好的折叠共源共栅原理图电路的例子。

该论文讨论了在折叠共源共栅结构中输入和输出电压的增加,但它并没有讨论折叠共源共栅方案的一个更为重要的性能,即这种结构可以消除米勒效应,以便能工作在更高的频率上。

图5给出的折叠结构放大器采用了升压控制器U1(德州仪器公司的UC3854A可能是一个理想的选择方案),并通过电阻器R驱动一个低压和低RDS的MOSFET(Q1)。

由于高压晶体管Q2是共栅结构(图6),并且Q1连接Q2的源极,因此该共源结构具有阻抗极低的漏极负载。

在工作状态下,当负载的阻抗很低时,Q1的漏极电压摆幅仅为VCC左右。

由于Q1的电压增益很低,因此未产生米勒效应。

上面的高电压MOSFETQ2采用共栅极连接,从而消除了负反馈和米勒效应。

这就是为什么Q2的视在电容值仅等于栅/源极电容值,甚至低于栅/源极电容值(由于Q2、CDS的正反馈)的原因。

在工作期间,Q1和Q2具有导通或者截止两种状态。

当Q2漏极电压快速变化时,该电压通过电容CDG和CDS影响栅源极网络。

二极管D对Q2的源极进行箝位,当Q2截止并且Q2的漏极通过CDS上拉至源极时,将Q2的源极连接到VCC。

值得一提的是,Q2的漏极将严重影响Q2的栅极电路,从而改变VCC。

为避免这种影响,VCC电源应该具备不受上拉和下拉变化影响的能力,能吸收和提供足够大的电流。

VCC电源可以采用线性电压整流器LM78L15和运算放大器来实现,能够产生大约1A的输出电流。

安森美半导体公司的TCA0372可能是一个好的选择。

图7和图8是折叠共源共栅结构的相关波形图,这些波形显示没有出现米勒效应。

当工作频率远高于传统PFC的工作频率时,可采用这种折叠共源共栅结构。

作者:

GregoryMirsky,首席执行官,Email:

mirskiy@,MilaviaInternational

作者简介:

GregoryMirsky是MilaviaInternational首席执行官,他拥有俄罗斯列宁格勒机械学院(即现在的圣彼得堡波罗的海科技大学)硕士学位,以及俄罗斯莫斯科师范大学博士学位(PhD)。