仿真PowerDC直流压降仿真指导书Word文档格式.docx

《仿真PowerDC直流压降仿真指导书Word文档格式.docx》由会员分享,可在线阅读,更多相关《仿真PowerDC直流压降仿真指导书Word文档格式.docx(15页珍藏版)》请在冰豆网上搜索。

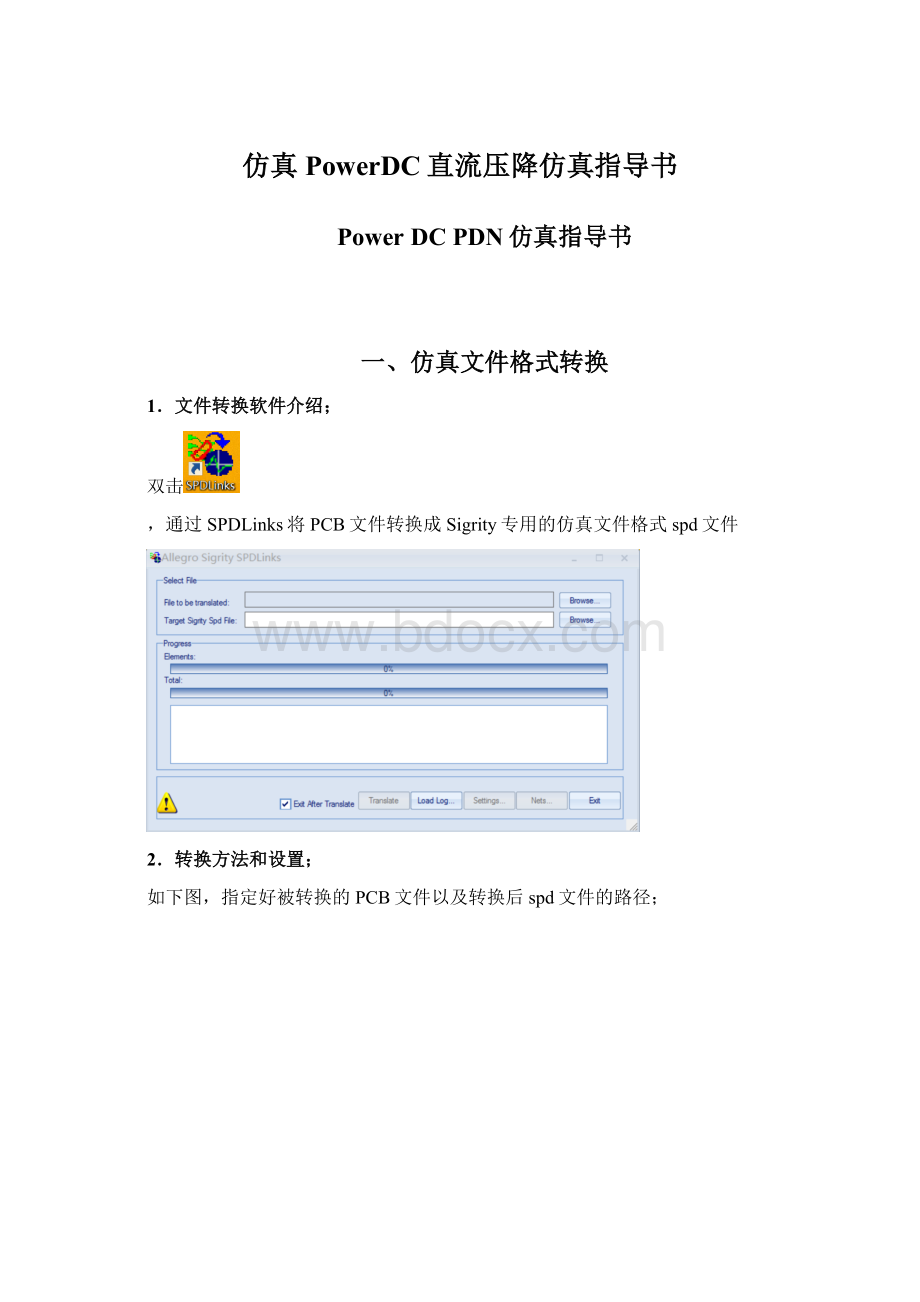

二、仿真设置

1.启动PowerDC软件

双击

,进入PowerDC主界面,点击

,创建仿真任务。

选取

模式,接下来导入仿真文件,进行仿真设置。

2.PowerDC仿真设置

2.1仿真叠层和padstack设置

Pcb转成Spd文件过程中,会将pcb的相关叠层设置一并转换过来;

因此导入spd文件后会直接生成相关的叠层,建议直接在allegro里面设置好叠层,避免后期重复设置。

ViaPlatingThicknessSetup:

edit>

padstacklibrary输入过孔镀铜厚度

2.3仿真网络设置

首先,选择需要仿真的电源网络,将其从信号网络类别转换到PowerNets类别中;

将所有GND网络(包含单点接地的GND网络)转换到GroundNets类别中,同时将除power和GND两类以外的网络全部disable掉。

2.4设置仿真端口

直流IRDrop仿真需设置源端和负载端,以便计算从源端到负载端通路上的直流压降,进而计算出通路的直流阻抗。

Sourcesink选择的原则:

BUCK电源source选择在反馈线处电容或电感处设置

LDO电源source选择在PMU出来的管脚处设置

2.4.1电流源端设置

通常源端选用自动生成的方式,在之前enable的网络中进行选择;

电压同一设置为1V,Tolerance不设置;

以此类推将需要仿真的网络全部设置好。

如自动无法产生端口,可以通过手动方式,设置电流源端口;

手动端口设置可以直接通过网络选择整体芯片自动生成端口。

2.4.2负载端设置

负载端同样采用自动生成端口的方式,在之前enable的网络中选取;

电流端口选择负载的器件,具体设置如下图;

设置完成,检查无误后保存文件后可以开始仿真。

(Model选择注意要选择equalvoltage,这样两者仿真出来的结果就跟resistancemeasurementgeneration一样)

IRDrop

中的测得的压降值得是各个pin中最坏压降。

各个pin的电压是不相等的,通过V/I得到的R会大

Resistance中

port中所有的pin

都是short起来的,电压相等,结果是整体的

R。

将IRDrop中的sink设置成等电压会得到理想结果

Unequalcurrent:

Importcurrentmappingfileinspreadsheetformatorcreatepingroupsmanually.

如果仿真是为了看整个port的R的话,用上面的方法IRDrop/sinkmodel=equalvoltage

如果仿真是为了看port中哪个pin压降最大的话,可以sink选择equalcurrent,p/fmodel选择worst,这样计算出来的就是最坏情况下的压降

三、仿真结果分析

1.仿真结果含义

根据仿真的压降结果,结合之前步骤设置的1A电流,可以推导出实际的走线电阻;

按照LDO电源走线+/-3%的的tolerance,结合各电源实际电压和电流,判断是否超标。

当然也可以在前期仿真设置阶段将电压和电流直接写进去,仿真结束后会直接输出Pass或Fail的结论。

2.电流分布

Power-DC还可以直观的体现整体电流密度情况,通过

可以观察整体电流等参数的平面分布。

3.仿真结果后期处理:

SetupE-constrain

通过在SetupE-constrain设置各种约束来看仿真结果:

Sinkvoltagesetup:

1.ClicktheSinkVoltagetabintheConstraintsSetupmenu.

2.SelectallSinks.

3.Right-clickandchooseGroupEditfromthepop-upmenu设置sink的电压和波动幅值

4.EditNominalVoltage(V),UpperTolerance(+%),andLowerTolerance(-%)

5.ClickViewE-ResultsTablesintheWorkflowpane,andclicktheSinkVoltagetab.TheSinkVoltageresultsareupdatedintheResultpane.

可以直观的看出来压降有没有超标

InterconnectCurrentSetup跟Sinkvoltag约束一样,可以看出通过电阻或电感的电流有没有超标

V/IProbesSetup:

VoltageProbe:

在ConstraintsSetup>

voltageprobe中设置约束条件,在ViewE-ResultsTables>

V/Iprobe中看voltageprobe的电压有没有超过约束值

CurrentProbe:

TheCurrentProbemeasurestheVia’scurrent

1.SelectseveralViasintheLayoutwindow.

2.Right-clickintheblankspaceintheV/IProbestableandchooseAddfromthepop-upmenu

TheCurrentProbeiscreatedautomatically

可以查看你关注的流过这些过孔的电流有没有超标

ViaCurrent/CurrentDensitySetup:

分via和padstack,可以约束过孔或pad上流过的电流

ConstraintsSetup>

ViaCurrent/CurrentDensity设置过孔或pad的电流和电流密度约束值

ViewE-ResultsTables>

GlobalViaCurrent/GlobalViaCurrentDensity显示超过这些约束值的过孔或pad

PlaneCurrentDensitySetup:

可以对平面电流密度设置全局约束也可以对特定的电源平面设置局部约束

PlaneCurrentDensity设置平面电流密度约束

GlobalPlaneCurrentDensityshowtheresults.

TraceCurrentDensitySetup:

设置走线的全局或局部约束

TraceCurrentDensity

Pinlocationeffectiveness相当于resistancemeasurementgeneration设置成lumpedtomultiple,source短接在一起,sink分开,可以仿真出最坏情况的pin

PowerDChastheabilitytodosweepinganalysistovariancesinsomeelectricalandphysicalparameterssuchas:

Setup>

SweepingManager

•CircuitGlobalParameter

•Conductivity

•Interconnect

•LayerThickness

•SinkCurrent

•ViaPlatingThickness

•VRMVoltage

Afterthesimulationcompletes,allsweepingandoriginalsimulationresultsareautomaticallysavedintoafoldernamedWorkspaceFileName_Sweep_Results