差错控制编码仿真Word文件下载.docx

《差错控制编码仿真Word文件下载.docx》由会员分享,可在线阅读,更多相关《差错控制编码仿真Word文件下载.docx(14页珍藏版)》请在冰豆网上搜索。

即1+1=0、1+0=1、0+1=1、0+0=0;

1×

1=1、1×

0=0、0×

1=0。

且码字

与码字

的运算在各个相应比特位上符合上述二进制加法运算规则。

线性分组码具有如下性质(n,k)的性质:

1)封闭性。

任意两个码组的和还是许用的码组。

2)码的最小距离等于非零码的最小码重。

对于码组长度为n、信息码元为k位、监督码元为r=n-k位的分组码,常记作(n,k)码,如果满足2r-1≥n,则有可能构造出纠正一位或一位以上错误的线性码。

下面我们通过(7,4)分组码的例子来说明如何具体构造这种线性码。

设分组码(n,k)中,k=4,为能纠正一位误码,要求r≥3。

现取r=3,则n=k+r=7。

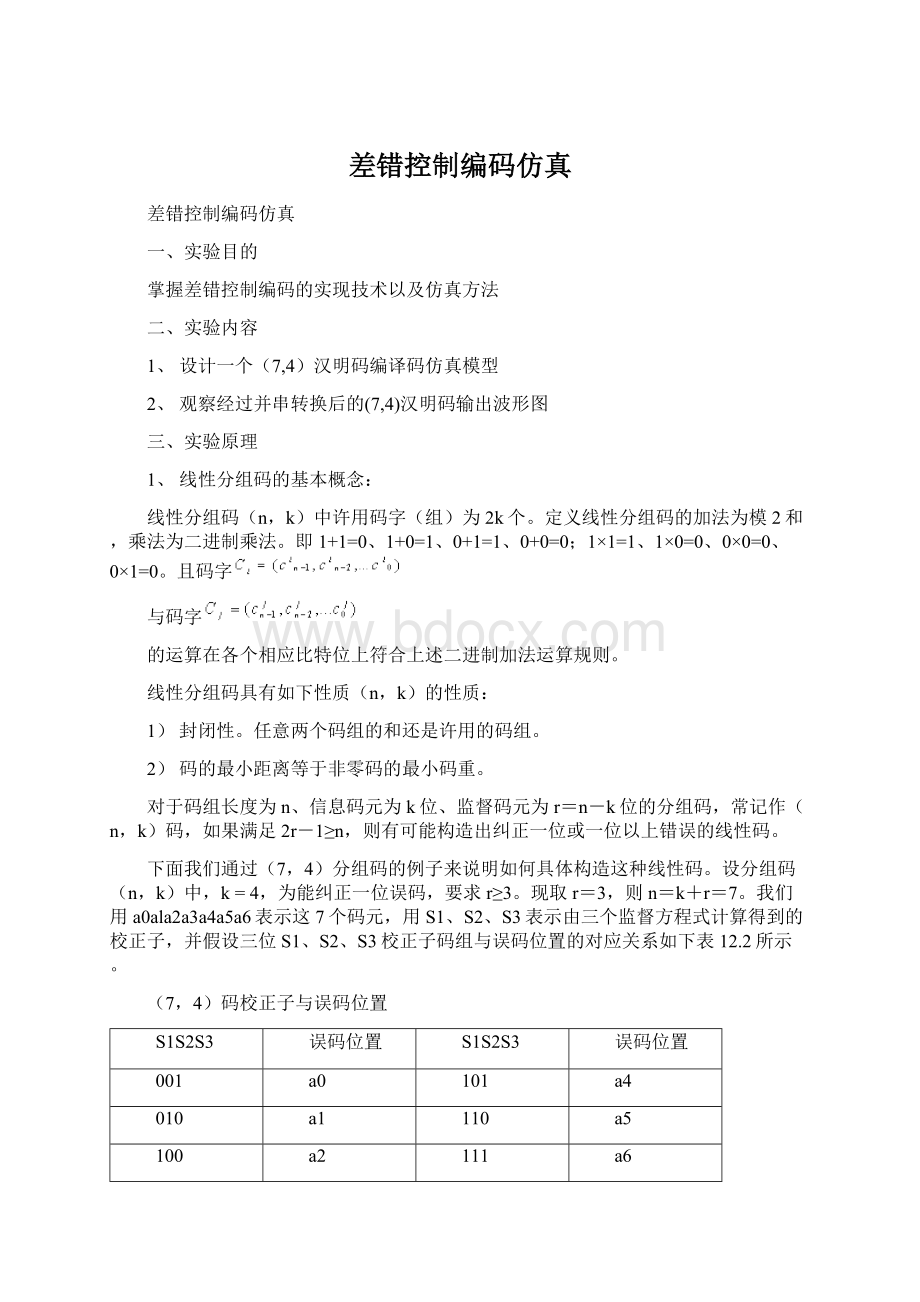

我们用a0ala2a3a4a5a6表示这7个码元,用S1、S2、S3表示由三个监督方程式计算得到的校正子,并假设三位S1、S2、S3校正子码组与误码位置的对应关系如下表12.2所示。

(7,4)码校正子与误码位置

S1S2S3

误码位置

001

a0

101

a4

010

a1

110

a5

100

a2

111

a6

011

a3

000

无错

由表可知,当误码位置在a2、a4、a5、a6时,校正子S1=1;

否则S1=0。

因此有S1=a6⊕a5⊕a4⊕a2,同理有S2=a6⊕a5⊕a3⊕a1和S3=a6⊕a4⊕a3⊕a0。

在编码时a6、a5、a4、a3为信息码元,a2、a1、a0为监督码元。

则监督码元可由以下监督方程唯一确定

即

由上面方程可得到表12.3所示的16个许用码组。

在接收端收到每个码组后,计算出S1、S2、S3,如果不全为0,则表示存在错误,可以由表12.2确定错误位置并予以纠正。

例如收到码组为0000011,可算出S1S2S3=011,由表12.2可知在a3上有一误码。

通过观察可以看出,上述(7,4)码的最小码距为dmin=3,它能纠正一个误码或检测两个误码。

如果超出纠错能力则反而会因“乱纠”出现新的误码。

(7,4)许用码组

信息位

监督位

a6a5a4a3

a2a1a0

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

上述方法构造的能纠正单个误码的线性分组码又称为汉明码。

它具有以下一些特点:

码长n=2m-1,最小码距为d=3,信息码长k=2n-m-1,纠错能力t=1,监督码长r=n-k=m。

这里m为≥2的正整数。

给定m后,就可构造出汉明码(n,k)。

1、(7,4)汉明码的编译码仿真:

图12.1所示为(7,4)汉明码的编码器电路原理图,图12.2为对应的译码器电路原理图。

根据上述两图可构建如图12.3所示的仿真原理图。

该仿真原理图包含两个子系统,分别是(7,4)汉明码的编码器和译码器。

仿真时的信号源采用了一个PROM,并由用户自定义数据内容,数据的输出由一个计数器来定时驱动,每隔一秒输出一个4位数据(PROM的8位仅用了其中4位),由编码器子系统编码转换后成为7位汉明码,经过并串转换后传输,其中的并串、串并转换电路使用了扩展通信库2中的时分复用合路器和分路器图符,该合路器和分路器最大为16位长度的时隙转换,这里定义为7位时隙。

此时由于输入输出数据的系统数据率不同,因此必须在子系统的输入端重新设置系统采样率,将系统设置为多速率系统。

因为原始4位数据的刷新率为1Hz,因此编码器的输入端可设置重采样率位10Hz,时分复用合路器和分路器的数据帧周期设为1秒,时隙数位7,则输出采样率为输入采样率的7倍,即70Hz。

如果要加入噪声,则噪声信号源的采样率也应设为70Hz。

图1是(7,4)汉明码编码器的仿真子系统原理图,图2是其对应的译码器的仿真子系统原理图。

图3为经过并串转换后的(7,4)汉明码输出波形图,这里仅设置了4秒时间长度的仿真,输出的4个数据为0、1、3、4,对应的(7,4)汉明码码字为(0000000)、(0001011)、(0011110)、(0100110),注意串行传输的次序是先低后高的次序(LSB)。

图1(7,4)汉明码编码器的仿真子系统原理图

图2(7,4)汉明码译码器的仿真子系统原理图

当然,我们也可以不通过并串转换,直接并行传输、译码。

这样可以在7位汉明码并行传输时人为对其中的一位进行干扰,并观察其纠错的情况。

通过仿真实验可以发现,出现两位以上错误时汉明码就不能正确纠错了。

因此,在要求对多位错误进行纠正的应用场合,就要使用别的编码方式了,如BCH码、RS码、卷积码等。

图3输入为0、1、3、4的(7,4)汉明码输出波形图