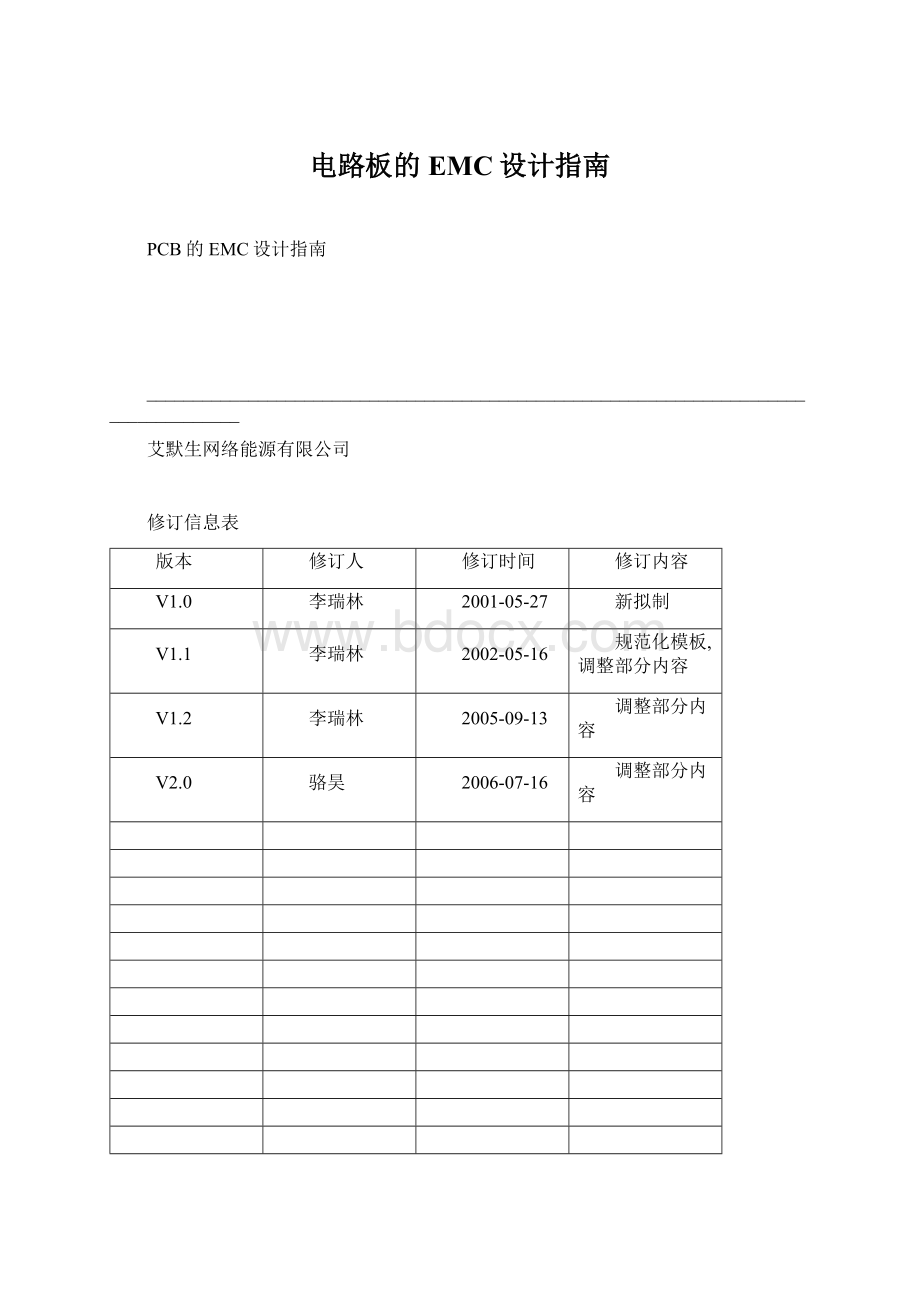

电路板的EMC设计指南Word下载.docx

《电路板的EMC设计指南Word下载.docx》由会员分享,可在线阅读,更多相关《电路板的EMC设计指南Word下载.docx(61页珍藏版)》请在冰豆网上搜索。

”

在一个电子系统中,印制板作为硬件系统的核心部件之一,印制板设计的好坏将直接影响到整个系统的稳定性,因此,在设计之初就充分考虑到电磁兼容的问题,考虑到信号的完整性等,无疑将提高系统的稳定性,缩短开发周期,提前将稳定的系统推向市场。

在任何设计中,经验永远占有一席之地,在处理EMC问题上,经验与技术诀窍仍然如此,从电路设计开始就参考抑制EMI的技术人员汇总的经验与技术诀窍,将之成功地运用于系统设计中,将产生事半功倍的效果。

然而,随着系统越来越复杂化,系统频率越来越高,已有的一些经验不一定适合现在和将来的要求,但从设计初期就开始考虑EMC问题、考虑信号完整性,进行可生产、可测试、可维护性设计,始终是设计时应该考虑的问题。

对于新出现的问题,目前一般采用模拟分析的方法,但是由于该方法对设计人员经验等要求相对较高,而且一些问题诸如过孔与焊接模型的建立等还存在一些问题,比较完整的系统数学模型建立也是一个长期和复杂的工程,导致仿真程序的结果也并不尽如人意。

而且系统将来运行环境的模型化也有一定的困难,仿真程序也难以包含所有的情况。

对我司产品而言,目前绝大部分设计还很难做到这一步。

因此,经验的积累与传授仍将是一项长期的任务。

纵观国内外业界精英的做法,无一不是在产品的预研、开发阶段投入大量精力,在设计阶段开展EMC工作,避免可能出现的电磁兼容问题。

我司在EMC等产品专项工程方面也开展了一系列的研究并取得一定的成绩,EMC研究室、CAD室、以及相关产品线均做出一些探索性的工作。

作为EMI的源头,器件选型、原理设计、PCB设计已逐渐引起重视,硬件开发人员对PCB的EMC设计提出了要求。

为了对PCB的EMC设计成果加以总结、推广,同时对一些未知的领域进行积极的探索,在EMC室和CAD室的积极参与下,由金明宇、骆昊、李瑞林、原晓霞、候俊锋在参考了我司以前对EMC方面进行的总结,共同编制了《PCB的EMC设计指南》。

文中的有些观点、建议仅仅是现有工作经验的总结,由于EMC领域的诸多未知因素,加上编者的水平有限,错误、疏漏之处在所难免,还望大家不断批评、指正。

对于本文的任何不明白之处,以及任何有益建议请与EMC室、CAD室联系,共同探讨PCB的EMC设计过程中的任何实际问题。

同时感谢那些为此指南作过经验积累的同事及前同事胡寿林、谢敏仙、操方星、钱柏年、李静、汤昌茂、胡庆虎、于小卫。

本规范由艾默生网络能源有限公司研发部发布实施,适用于ENPC的PCB设计。

本规范由各产品开发部、电子工艺部等部门参照执行。

本规范拟制部门:

电子工艺部

本规范拟制人:

本规范会签人:

金明宇、李瑞林、原晓霞、候俊锋

本规范批准人:

季明明

本规范发布人:

研发业务管理办

目的

本指导书旨在指导公司PCB的EMC设计,将电路EMC设计要求在PCB中得以实现。

本书旨在对我司PCB的EMC设计现有成果加以总结、推广,结合我司PCB设计过程中的经验教训以及产品的EMC测试数据,谨供各位硬件工程师进行PCB的EMC设计时参考。

本指导书会不断升级,请使用最新版本。

范围

本指导书适用我司所有正式产品的PCBEMC设计。

引用/参考标准或资料

略

名词解释

EMC:

ElectromagneticCompatibility,电磁兼容

EMI:

ElectromagneticInterference,电磁干扰

弱信号:

在本文中电压小于等于Rms15V以下,同时电流小于等于100mA以下的信号。

强信号:

在本文中电压大于Rms48V以上,同时电流大于2A以上的信号。

指南简介

为了正确进行单板的EMC设计,特制定本指南。

指南内容

第一部分层的设置

1层的设置

在PCB的EMC设计考虑中,首先涉及的便是层的设置;

单板的层数由电源、地的层数和信号层数组成;

电源层、地层、信号层的相对位置以及电源、地平面的分割对单板的EMC指标至关重要。

1.1弱信号单板的合理层数

根据单板的电源、地的种类、信号密度、板级工作频率、有特殊布线要求的信号数量,以及综合单板的性能指标要求与成本承受能力,确定单板的层数;

对于EMC指标要求苛刻(如:

产品需认证CISPR22CLASSB)而相对成本能承受的情况下,适当增加地平面乃是PCB的EMC设计的杀手锏之一。

1.1.1Vcc、GND的层数

单板电源的层数由其种类数量决定;

对于单一电源供电的PCB,一个电源平面足够了;

对于多种电源,若互不交错,可考虑采取电源层分割(保证相邻层的关键信号布线不跨分割区);

对于电源互相交错(尤其是象8260等IC,多种电源供电,且互相交错)的单板,则必须考虑采用2个或以上的电源平面,每个电源平面的设置需满足以下条件:

单一电源或多种互不交错的电源;

相邻层的关键信号不跨分割区;

地的层数除满足电源平面的要求外,还要考虑:

元件面下面(第2层或倒数第2层)有相对完整的地平面;

高频、高速、时钟等关键信号有一相邻地平面;

关键电源有一对应地平面相邻(如5V与GND相邻)。

1.1.2信号层数

在CAD室现行工具软件中,在网表调入完毕后,EDA软件能提供一布局、布线密度参数报告,由此参数可对信号所需的层数有个大致的判断;

经验丰富的CAD工程师,能根据以上参数再结合板级工作频率、有特殊布线要求的信号数量以及单板的性能指标要求与成本承受能力,最后确定单板的信号层数。

信号的层数主要取决于功能实现,从EMC的角度,需要考虑关键信号网络(强辐射网络以及易受干扰的小、弱信号)的屏蔽或隔离措施。

1.2电源层、地层、信号层的相对位置

1.2.1Vcc、GND平面的阻抗以及电源、地之间的EMC环境问题

电源、地平面存在自身的特性阻抗,电源平面的阻抗比地平面阻抗高;

为降低电源平面的阻抗,尽量将PCB的主电源平面与其对应的地平面相邻排布并且尽量靠近,利用两者的耦合电容,降低电源平面的阻抗;

电源地平面构成的平面电容与PCB上的退耦电容一起构成频响曲线比较复杂的电源地电容,它的有效退耦频带比较宽,(但存在谐振问题)。

1.2.2Vcc、GND作为参考平面,两者的作用与区别

电源、地平面均能用作参考平面,且有一定的屏蔽作用;

但相对而言,电源平面具有较高的特性阻抗,与参考电平存在较大的电位势差;

从屏蔽的角度,地平面一般均作了接地处理,并作为基准电平参考点,其屏蔽效果远远优于电源平面;

在选择参考平面时,应优选地平面。

1.2.3电源层、地层、信号层的相对位置

对于电源、地的层数以及信号层数确定后,它们之间的相对排布位置是每一个EMC工程师都不能回避的话题;

单板层的排布一般原则:

元件面下面(第二层)为地平面,提供器件屏蔽层以及为顶层布线提供参考平面;

所有信号层尽可能与地平面相邻;

尽量避免两信号层直接相邻;

主电源尽可能与其对应地相邻;

兼顾层压结构对称。

注:

具体PCB的层的设置时,要对以上原则进行灵活掌握,在领会以上原则的基础上,根据实际单板的需求,如:

是否需要一关键布线层、电源、地平面的分割情况等,确定层的排布:

四层板,优选方案1,可用方案3

方案

电源层数

地层数

信号层数

1

2

3

4

S

G

P

表-1四层板解决方案表

方案1:

图1四层PCB的主选层设置方案

此方案为CAD室现行四层PCB的主选层设置方案,在元件面下有一地平面,关键信号优选布TOP层;

至于层厚设置,有以下建议:

满足阻抗控制

芯板(GND到POWER)不宜过厚,以降低电源、地平面的分布阻抗;

保证电源平面的去耦效果;

推荐芯板厚0.2mm,4层板采用1.0的板厚。

为了达到一定的屏蔽效果,有人试图把电源、地平面放在TOP、BOTTOM层,即采用方案2。

方案2:

图2四层板解决方案2

此方案为了达到想要的屏蔽效果,至少存在以下缺陷:

电源、地相距过远,电源平面阻抗较大

电源、地平面由于元件焊盘等影响,极不完整

由于参考面不完整,信号阻抗不连续

实际上,由于我司大量采用表贴器件,对于器件越来越密的情况下,本方案的电源、地几乎无法作为完整的参考平面,预期的屏蔽效果很难实现;

方案3:

图3四层板解决方案3

此方案同方案1类似,适用于主要器件在BOTTOM布局或关键信号底层布线的情况;

六层板,优选方案3,可用方案1,备用方案2、4

电源

地

信号

5

6

S1

S2

S3

S4

G1

G2

表-2六层板解决方案表

对于六层板,优先考虑方案3,优选布线层S2,其次S3、S1。

主电源及其对应的地布在4、5层,层厚设置时,增大S2-P之间的间距,缩小P-G2之间的间距(相应缩小G1-S2层之间的间距),以减小电源平面的阻抗,减少电源对S2的影响;

在成本要求较高的时候,可采用方案1,优选布线层S1、S2,其次S3、S4,与方案1相比,方案2保证了电源、地平面相邻,减少电源阻抗,但S1、S2、S3、S4全部裸露在外,只有S2才有较好的参考平面;

对于局部、少量信号要求较高的场合,方案4比方案3更适合,它能提供极佳的布线层S2。

八层板:

优选方案2、3、可用方案1

7

8

S5

G3

P1

P2

表-3八层板解决方案表

对于单电源的情况下,方案2比方案1减少了相邻布线层,增加了主电源与对应地相邻,保证了所有信号层与地平面相邻,代价是:

牺牲一布线层;

对于双电源的情况,推荐采用方案3,方案3兼顾了无相邻布线层、层压结构对称、主电源与地相邻等优点,但S4应减少关键布线;

方案4:

无相邻布线层、层压结构对称,但电源平面阻抗较高;

应适当加大3-4、5-6,缩小2-3、6-7之间层间距;

方案5:

与方案4相比,保证了电源、地平面相邻;

但S2、S3相邻,S4以P2作参考平面;

对于底层关键布线较少以及S2、S3之间的线间窜扰能控制的情况下此方案可以考虑;

十层板:

推荐方案2、3、可用方案1、4

9

10

S6

G4

表-4十层板解决方案表

扩大3-4与7-8各自间距,缩小5-6间距,主电源及其对应地应置于6、7层;

优选布线层S2、S3、S4,其次S1、S5;

本方案适合信号布线要求相差不大的场合,兼顾了性能、成本;

推荐大家使用;

但需注意避免S2、S3之间平行、长距离布线;

EMC效果极佳,但与方案3比,牺牲一布线层;

在成本要求不高、EMC指标要求较高、且必须双电源层的关键单板,建议采用此种方案;

优选布线层S2、S3,

对于单电源层的情况,首先考虑方案2,其次考虑方案1。

方案1具有明显的成本优势,但相邻布线过多,平行长线难以控制;

十二层板:

推荐方案2、3,可用方案1、4、备用方案5

11

12

S7

G5

表-512层板解决方案表

以上方案中,方案2、4具有极好的EMC性能,方案1、3具有较佳的性价比;

以上层排布作为一般原则;

具体设计过程中可根据需要的电源层数、布线层数、特殊布线要求信号的数量、比例以及电源、地的分割情况,结合以上排布原则灵活掌握。

1.3强信号单板的合理层数

根据单板的功率密度、器件密度、功率流向是否顺畅,开关管的dV/dt,等有特殊布线要求的信号,同时综合单板的成本,确定单板的层数,推荐4层板。

第二部分布线

2布线

2.1布线基本规则

在这里就一些设计中应该遵循的基本规则,结合以前在设计中出现的问题,作一些简单的说明:

2.1.1信号回流最小规则

图4信号回流最小规则

即环面积最小规则,环面积越小,对外的辐射越少。

针对这一规则,在地平面分割时,要考虑到地平面与重要信号走线的分布,防止由于地平面开槽等带来的问题;

在双层板设计中,在为电源留下足够空间的情况下,应该将双面留下的部分用地信号填充,且增加一些必要的孔,将双面地信号有效连接起来,对一些关键信号尽量采用地线隔离,对一些频率较高的设计,需特别考虑其地平面回路问题,建议采用多层板为宜。

2.1.2窜扰分析与控制规则

图5窜扰分析示图

主要针对比较长的平行走线而言,同时满足了5-5原则的信号,一般来说,采用差分信号方式设计,能产生比较理想的效果;

在背板设计中,一般采用中间隔地方式;

对普通的印制板设计来说,应该尽量将线间距离尽量隔开一些,满足3W原则以减低窜扰。

2.1.3走线屏蔽规则

图6走线屏蔽规则

对应信号回流最小规则,实际上也是为了尽量减小信号的回路面积,多见于一些比较重要的信号,如时钟信号,同步信号;

对一些特别重要,频率特别高的信号,应该考虑采用同轴电缆屏蔽结构设计,即将所布的线上下左右用地线隔离,而且还要考虑好如何有效的让屏蔽地与实际地平面有效结合。

注意:

当采用屏蔽规则时,最好应用在一些微弱的信号上,同时保证屏蔽层的良好接地。

对于一般的信号来说,如果屏蔽层的阻抗非常小也是可以采用的。

2.1.4走线的方向控制规则

图7走线的方向控制规则

即相邻层的走线方向成正交结构,这是设计的基本要求,但在实际设计中很难做到,在设计中应该尽量去做。

不要将不同的信号线在相邻层走成同一方向,以减少不必要的窜扰;

对背板上出现该情况,特别是信号速率又高时,应考虑用地平面隔离各布线层,用地信号线隔离各信号线。

对于一些复杂器件(如:

BGA封装的器件)来说不可避免要违反正交原则,这时要注意各类信号的扇出方向,同种类型的网络在一起。

2.1.5走线的开环检查规则

图8走线的开环检查规则

主要是为了避免产生"

天线效应"

,我们知道,在天线的末端面积越小,其发射效果越显著。

对一些高频信号,一定要避免这样的设计产生,否则可能带来不可预知的结果。

PCB板防天线布线如下图所示。

2.1.6阻抗匹配检查规则

主要是为了防止产生反射,在设计中应该尽量避免这样的设计发生,有时设计无法避免类似的结构时,我们应该尽量减少中间不一致部分的有效长度,对诸如BGA之类的器件,这类问题将可能难以避免。

2.1.7走线终结网络规则

图9走线终结网络规则

就是通常所说的终端匹配原则,对母板上的长线及一些时钟线,要仔细分析其可能带来的影响,选择对应的匹配方案。

在这个问题上,一定要结合实际的布局来综合考虑,否则可能产生匹配电阻满板加的情况。

终端匹配电阻在走线末端。

2.1.8走线闭环检查规则

图10走线闭环检查规则

即布线自环规则,主要是一些设计由于层数太多而没有注意到这类问题的发生,在设计中,务必使重要信号不要产生类似的结构,尽量减少信号由于形成环状而产生的辐射大增情况。

2.1.9走线的分枝长度控制规则

图11走线的分枝长度控制规则

尽量控制分枝的长度,一般的要求是Tdelay<

=Trise/20。

2.1.10走线的谐振规则

图12走线的谐振规则

主要针对高频信号设计而言,即布线长度不得与其波长成整数倍关系,以免产生谐振现象。

2.1.11走线长度控制规则

图13走线长度控制规则

即短线规则,也就是说在设计时应该尽量让布线长度尽量短,以减少由于走线过长带来的干扰问题,特别是一些重要信号线,如时钟线,我们务必将其振荡器放在离器件很近的地方。

对驱动多个器件的情况,一定要考虑好采用何种布局方式。

必要时必须牺牲布局来满足特定的要求。

2.1.12倒角规则

图14倒角规则

主要是防止尖角处阻抗太大,产生辐射,同时工艺性能也不好。

公司一般将此作为一项必须遵守的规则。

2.1.13器件去耦规则

图15器件去耦规则

也就是增加必要的去耦电容,滤除电源上的干扰信号,使电源信号稳定。

在多层板中,对去耦电容的位置一般要求不太高,但对双层板,去耦电容的布局及电源的布线方式将直接影响到整个系统的稳定性,有时甚至关系到设计的成败。

在双层板设计中,一般应该使电流先经过滤波电容滤波再供器件使用,同时还要充分考虑到由于器件产生的电源噪声对下游的器件的影响,一般来说,采用总线结构设计比较好,在设计时,我们还要考虑到由于传输距离过长而带来的电压跌落给器件造成的影响,必要时增加一些电源环路,避免产生电位差。

在高速电路设计中,能否正确地使用去耦电容,关系到整个板的稳定性。

2.1.14器件布局分区/分层规则

图16器件布局分区/分层规则

主要是为了防止不同工作频率的模块之间的互相干扰,同时尽量缩短高频部分的布线长度。

通常将高频的部分布设在接口部分以减少布线长度,当然,这样的布局仍然要考虑到低频信号可能受到的干扰。

同时还要考虑到高/低频部分地平面的分割问题,通常采用将二者的地分割,再在接口处单点相接,或者通过别的方式相连接。

对混合电路,也有将模拟与数字电路分别布置在印制板的两面,分别使用不同的层布线,中间用地层隔离的方式。

2.1.15孤立铜区控制规则

图17立铜区控制规则

孤立铜区的出现,将带来一些不可预知的问题,因此将孤立铜区与别的信号相接,有助于改善信号质量,通常是将孤立铜区接地或删除。

在实际的设计中,有时我们会看见厂家将一些板的空置部分增加了一些小小的铜薄,这主要是为了方便印制板加工,同时对防止引制板翘曲也有一定的作用。

2.1.16PCB板层定义规则

图18PCB板层定义规则

该规则主要目的是尽量隔离布线层,有效地降低信号间的干扰。

2.1.17电源与地线层的阻抗匹配规则

图19电源与地线层的阻抗匹配规则

实际上该规则与信号回流最小规则的本质是一样的,都是为了有效减少信号环面积,减少干扰。

2.1.18重叠电源与地线层规则

图20重叠电源与地线层规则

主要是为了减少不同电源之间的干扰,特别是一些电压相差很大的电源之间,重叠问题一定要设法避免,难以避免时可考虑中间隔地层。

2.1.193W规则

图213W规则

对一些带强烈高频成分的时钟信号,如果别的线与之靠得过近时,这些已达RF频率的能量将传到其它的信号上,为了有效的改善这类问题,经过实验证实,如果在相邻的信号之间增加一条接地的隔离线,那么信号之间的影响将大大减少,也就是说,如果保持两信号线中间的距离大于3倍干扰源信号宽度的距离,将有效改善相邻信号线之间的EMI干扰,这就是通常所说的3W规则。

3W规则可保持70%的电场不互相干扰,如要达到98%的电场不互相干扰,可使用10W的间距。

2.1.2020H规则

电源平面和地平面间的RF耦合可能进入自由空间,如下图中的左图所示。

很高速的PCB中,为了避免电源平面层向自由空间辐射能量,因此所有的电源平面必须小于地平面,向内缩进20H412。

为了更好地实行20H规则,就要使电源和地平面间的厚度最小,接近电源平面的走线层可布线区,就等于电源平面铜皮实体投影区。

(从另外一个图中可看出,接近地平面的走线层可布线区,就是地平面铜皮实体投影区)

图22电源平面的RF辐射

遵从20H规则会使PCB的电源层与地层间的电容的自谐振频率提高约2-3倍。

20H规则会使边缘效应减小70%,如果要想达到98%的效果,必须遵从100H规则。

如果在PCB上存在分区,后面章节会考虑到,也要在高频率带宽区(CPU、以太网、SCSI等)实行20H规则,当数字和模拟区之间提供隔离或滤波时,在分界线上也要适用20H规则。

如下图所示。

图23数字、模拟区边界线使用20H规则

2.1.21五一五规则

印制板层