三人多数表决电路文档格式.docx

《三人多数表决电路文档格式.docx》由会员分享,可在线阅读,更多相关《三人多数表决电路文档格式.docx(11页珍藏版)》请在冰豆网上搜索。

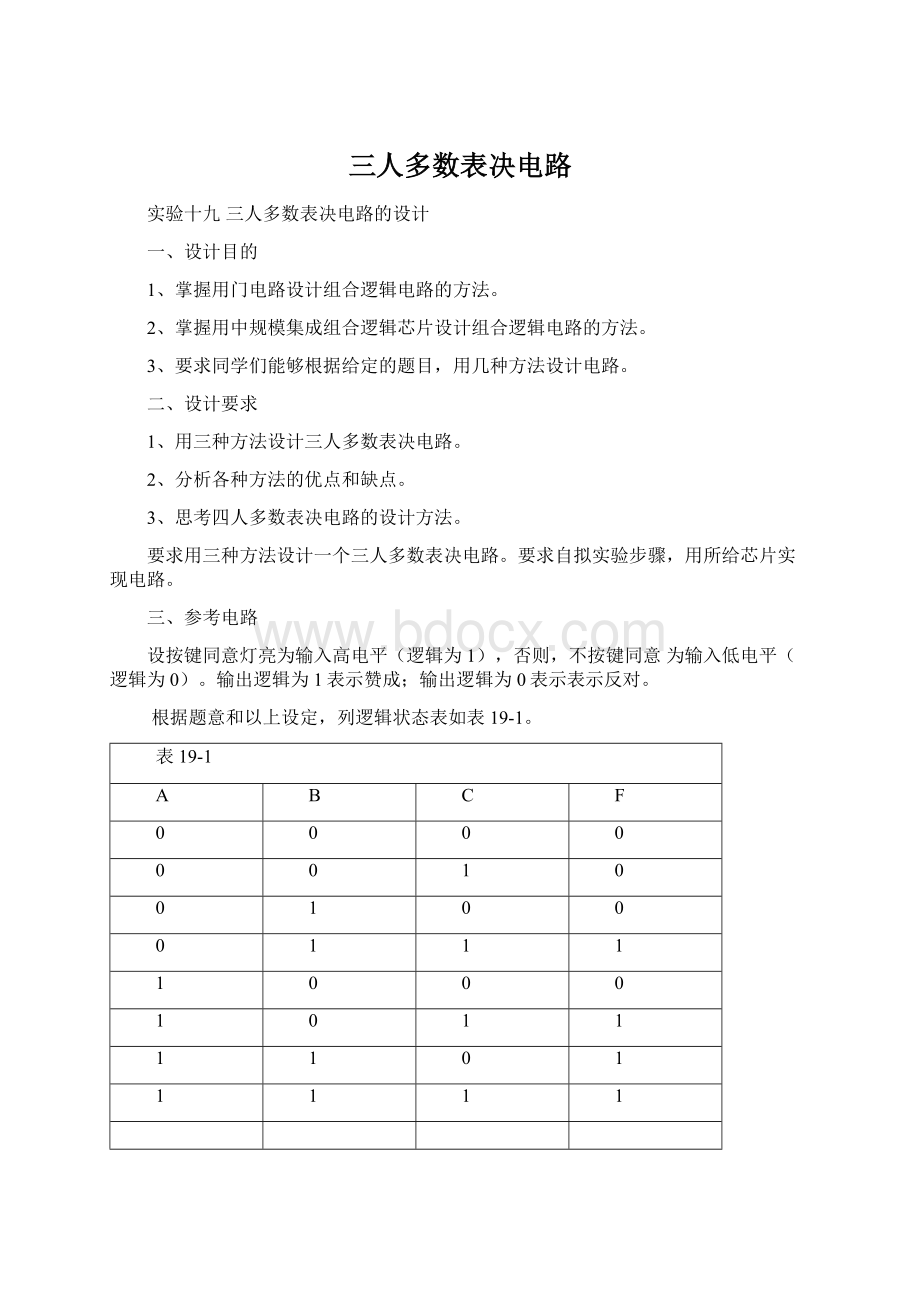

C

F

1

由逻辑状态表可知,能使输出逻辑为1的只有四项:

第4、6、7、8

项。

故,表决器的辑逻表达式应是:

从化简后的逻辑表达式可知,前一项括号中表达的是一个异或门

关系。

因此,作逻辑图如下。

经常用来设计组合逻辑电路的MSI芯片主要是:

译码器和数据选择器。

设计步骤前几步同上,写出的逻辑函数表达式可以不化简,直接用最小项之和的形式,然后根据题目要求选择合适的器件,并且画出原理图实现。

四、实验设备与器件

本实验的设备和器件如下:

实验设备:

数字逻辑实验箱,逻辑笔,万用表及工具;

实验器件:

74LS00、74LS20、74LS138、74LS153等。

五、实验报告要求

1、写出具体设计步骤,画出实验线路。

2、根据实验结果分析各种设计方法的优点及使用场合。

实验二十序列脉冲检测器的设计

1、学习时序逻辑电路的设计与调试方法。

2、了解序列脉冲发生器和序列脉冲检测器的功能区别及设计方法。

二、设计要求及技术指标

1、设计一个序列脉冲检测器,当连续输入信号110时,该电路输出为1,否则输出为0。

2、确定合理的总体方案。

对各种方案进行比较,以电路的先进性、结构的繁简、成本的高低及制作的难易等方面作综合比较。

自拟设计步骤,写出设计过程,选择合适的芯片,完成画出电路图。

3、组成系统。

在一定幅面的图纸上合理布局,通常是按信号的流向,采用左进右出的规律摆放各电路,并标出必要的说明。

注意:

还需设计一个序列脉冲产生器,作为序列脉冲检测器的输入信号。

4、用示波器观察实验中各点电路波形,并与理论值相比较,分析实验结论。

三、设计说明与提示

图20-1串行输入序列脉冲检测器原理框图。

它的功能是:

对输入信号X逐位进行检测,若输入序列中出现“110”,当最后的“0”在输入端出现时,输出Z为“1”;

若随后的输出信号序列仍为“110”,则输出端Z仍为“1”。

其他情况下,输出端Z为“0”。

其输入输出关系如下:

时钟CP12345678

输入X01101110

输出Z00010001

调试要点:

1、分块调试,即先调试出序列脉冲产生器的电路,再调试序列脉冲检测器的电路。

2、序列脉冲产生器和序列脉冲检测器应保证同步。

脉冲发生器电路的形式很多,为使电路简单化,可以用十进制计数器的最高位作为输出。

数字逻辑实验箱、双踪示波器、逻辑笔,万用表及工具;

74LS00、74LS112、74LS290、555定时器和电阻电容若干。

四、设计报告要求

1、画出总体原理图及总电路框图。

2、单元电路分析。

3、测试结果及调试过程中所遇到的故障分析。

实验十一多路智力抢答装置

一、实验目的

1、学习数字电路中D触发器、分频电路、多谐振荡器、CP时钟脉冲源等单元电路的综合运用。

2、熟悉多路智力抢答装置的工作原理。

3、了解简单数字系统实验、调试及故障排除方法。

二、实验原理

图11-1为供四人用的智力抢答装置线路,用以判断抢答优先权。

图11-1智力抢答装置原理图

图中F1为四D触发器74LS175,它具有公共置0端和公共CP端,引脚排列见附录;

F2为双4输入与非门74LS20;

F3是由74LS00组成的多谐振荡器;

F4是由74LS74组成的四分频电路,F3、F4组成抢答电路中的CP时钟脉冲源,抢答开始时,由主持人清除信号,按下复位开关S,74LS175的输出Q1~Q4全为0,所有发光二极管LED均熄灭,当主持人宣布“抢答开始”后,首先作出判断的参赛者立即按下开关,对应的发光二极管点亮,同时,通过与非门F2送出信号锁住其余三个抢答者的电路,不再接受其它信号,直到主持人再次清除信号为止。

三、实验设备与器件

1、+5V直流电源;

2、逻辑电平开关;

3、逻辑电平显示器;

4、双踪示波器;

5、数字频率计;

6、直流数字电压表;

7、74LS175、74LS20、74LS74和74LS00。

四、实验内容与步骤

1、测试各触发器及各逻辑门的逻辑功能。

2、图11-1接线,抢答器五个开关接实验装置上的逻辑开关、发光二极管接逻辑电平显示器。

3、断开抢答器电路中CP脉冲源电路,单独对多谐振荡器F3及分频器F4进行调试,调整多谐振荡器10K电位器,使其输出脉冲频率约4KHz,观察F3及F4输出波形及测试其频率。

4、试抢答器电路功能

接通+5电源,CP端接实验装置上连续脉冲源,取重复频率约1KHz。

(1)抢答开始前,开关K1、K2、K3、K4均置“0”,准备抢答,将开关S置“0”,发光二极管全熄灭,再将S置“1”。

抢答开始,K1、K2、K3、,K4某一开关置“1”,观察发光二极管的亮、灭情况,然后再将其它三个开关中任一个置“1”,观察发光二极的亮、灭有否改变。

(2)重复

(1)的内容,改变K1、K2、K3、K4任一个开关状态,观察抢答器的工作情况。

(3)整体测试

断开实验装置上的连续脉冲源,接入F3及F4,再进行实验。

五、实验预习要求

若在图11-1电路中加一个计时功能,要求计时电路显示时间精确到秒,最多限制为2分钟,一旦超出限时,则取消抢答权,电路如何改进。

六、实验报告

1、分析智力抢答装置各部分功能及工作原理。

2、总结数字系统的设计、调试方法。

3、分析实验中出现的故障及解决办法。

实验十二数字电子秒表

一、实验目的

1、学习数字电路中JK触发器、时钟发生器及计数、译码显示等单元电路的综合应用。

2、学习电子秒表的调试方法。

二、实验原理

图12-1为电子秒表的电原理图。

按功能分成三个单元电路进行分析。

1、控制电路

图12-1中单元Ⅰ为用集成JK触发器组成的控制电路为三进制计数器,图12-2为三进制计数器的状态转换图。

其中00状态为电子秒表保持状态,01状态为电子秒表清零状态,10状态为电子秒表计数状态。

JK触发器在电子秒表中的职能是为计数器提供清零信号和计数信号。

调试的时候先对JK触发器清零。

2、时钟发生器

图12-1中单元Ⅱ为用555定时器构成的多谐振荡器,是一种性能较好的时钟源。

调节电位器RW,使在输出端3获得频率为50HZ的矩形波信号,当JK触发器Q2=1时,门5开启,此时50HZ脉冲信号通过门5作为计数脉冲加于计数器①的计数输入端CP2 。

4、计数及译码显示

二—五—十进制加法计数器74LS90构成电子秒表的计数单元,如图12-1中单元Ⅲ所示。

其中计数器①接成五进制形式,对频率为50HZ的时钟脉冲进行五分频,在输出端Q3取得周期为0.1S的矩形脉冲,作为计数器②的时钟输入。

计数器②及计数器③接成8421码十进制形式,其输出端与实验装置上译码显示单元的相应输入端连接,可显示0.1~0.9秒;

1~9.9秒计时。

注:

集成异步计数器74LS90

74LS90是异步二—五—十进制加法计数器,它既可以作二进制加法计数器,又可以作五进制和十进制加法计数器。

图12-3为74LS90引脚排列,表12-1为功能表。

表12-1

输入

输出

功能

清0

置9

时钟

Q3Q2Q1Q0

R0

(1)、R0

(2)

S9

(1)、S9

(2)

CP1CP2

×

×

0×

0

↓1

Q0输出

二进制计数

1↓

Q3Q2Q1输出

五进制计数

↓QA

Q3Q2Q1Q0输出8421BCD码

十进制计数

QD↓

Q0Q3Q2Q1输出5421BCD码

11

不变

保持

通过不同的连接方式,74LS90可以实现四种不同的逻辑功能;

而且还可借助R0

(1)、R0

(2)对计数器清零,借助S9

(1)、S9

(2)将计数器置9。

其具体功能详述如下:

(1)计数脉冲从CP1输入,Q0作为输出端,为二进制计数器。

(2)计数脉冲从CP2输入,Q3Q2Q1作为输出端,为异步五进制加法计数器。

(3)若将CP2和Q0相连,计数脉冲由CP1输入,Q3、Q2、Q1、Q0作为输出端,则构成异步8421码十进制加法计数器。

(4)若将CP1与Q3相连,计数脉冲由CP2输入,Q0、Q3、Q2、Q1作为输出端,则构成异步二五混合进制计数器。

(5)清零、置9功能。

1)异步清零

当R0

(1)、R0

(2)均为“1”;

S9

(1)、S9

(2)中有“0”时,实现异步清零功能,即Q3Q2Q1Q0=0000。

2)置9功能

当S9

(1)、S9

(2)均为“1”;

R0

(1)、R0

(2)中有“0”时,实现置9功能,即Q3Q2Q1Q0=1001。

三、实验设备

1、+5V直流电源;

2、双踪示波器;

3、直流数字电压表;

4、数字频率计;

5、单次脉冲源;

6、连续脉冲源;

7、逻辑电平开关;

8、逻辑电平显示器;

9、译码显示器;

10、74LS00×

2、555×

1、74LS90×

3和74LS112、电位器、电阻和电容若干。

四、实验内容与步骤

由于实验电路中使用器件较多,实验前必须合理安排各器件在实验装置上的位置,使电路逻辑清楚,接线较短。

实验时,应按照实验任务的次序,将各单元电路逐个进行接线和调试,即分别测试基本RS触发器、单稳态触发器、时钟发生器及计数器的逻辑功能,待各单元电路工作正常后,再将有关电路逐级连接起来进行测试……,直到测试电子秒表整个电路的功能。

这样的测试方法有利于检查和排除故障,保证实验顺利进行。

1、控制电路(JK触发器)的测试

测试方法为:

加三个单脉冲,看是否完成类似图12-2的三个有效状态的一次循环。

2、时钟发生器的测试

测试方法参考实验十五,用示波器观察输出电压波形并测量其频率,调节RW,使输出矩形波频率为50Hz

3、计数器的测试

(1)计数器①接成五进制形式,RO

(1)、RO

(2)、S9

(1)、S9

(2)接逻辑开关输出插口,CP2接单次脉冲源,CP1接高电平“1”,Q3~Q0接实验设备上译码显示输入端D、C、B、A,按表12-1测试其逻辑功能,记录之。

(2)计数器②及计数器③接成8421码十进制形式,同内容

(1)进行逻辑功能测试。

记录之。

(3)将计数器①、②、③级连,进行逻辑功能测试。

4、电子秒表的整体测试

各单元电路测试正常后,按图12-1把几个单元电路连接起来,进行电子秒表的总体测试。

加三个单脉冲,观察是否工作在三个有效循环状态(清零、计数、停止)。

三个有效循环状态的顺序不能错。

5、电子秒表准确度的测试

利用电子钟或手表的秒计时对电子秒表进行校准。

五、预习报告

1、复习数字电路中JK触发器,时钟发生器及计数器等部分内容。

2、除了本实验中所采用的时钟源外,选用另外两种不同类型的时钟源,可供本实验用。

画出电路图,选取元器件。

3、列出电子秒表单元电路的测试表格。

4、列出调试电子秒表的步骤。

1、总结电子秒表整个调试过程。

2、分析调试中发现的问题及故障排除方法。

(注:

可编辑下载,若有不当之处,请指正,谢谢!

)