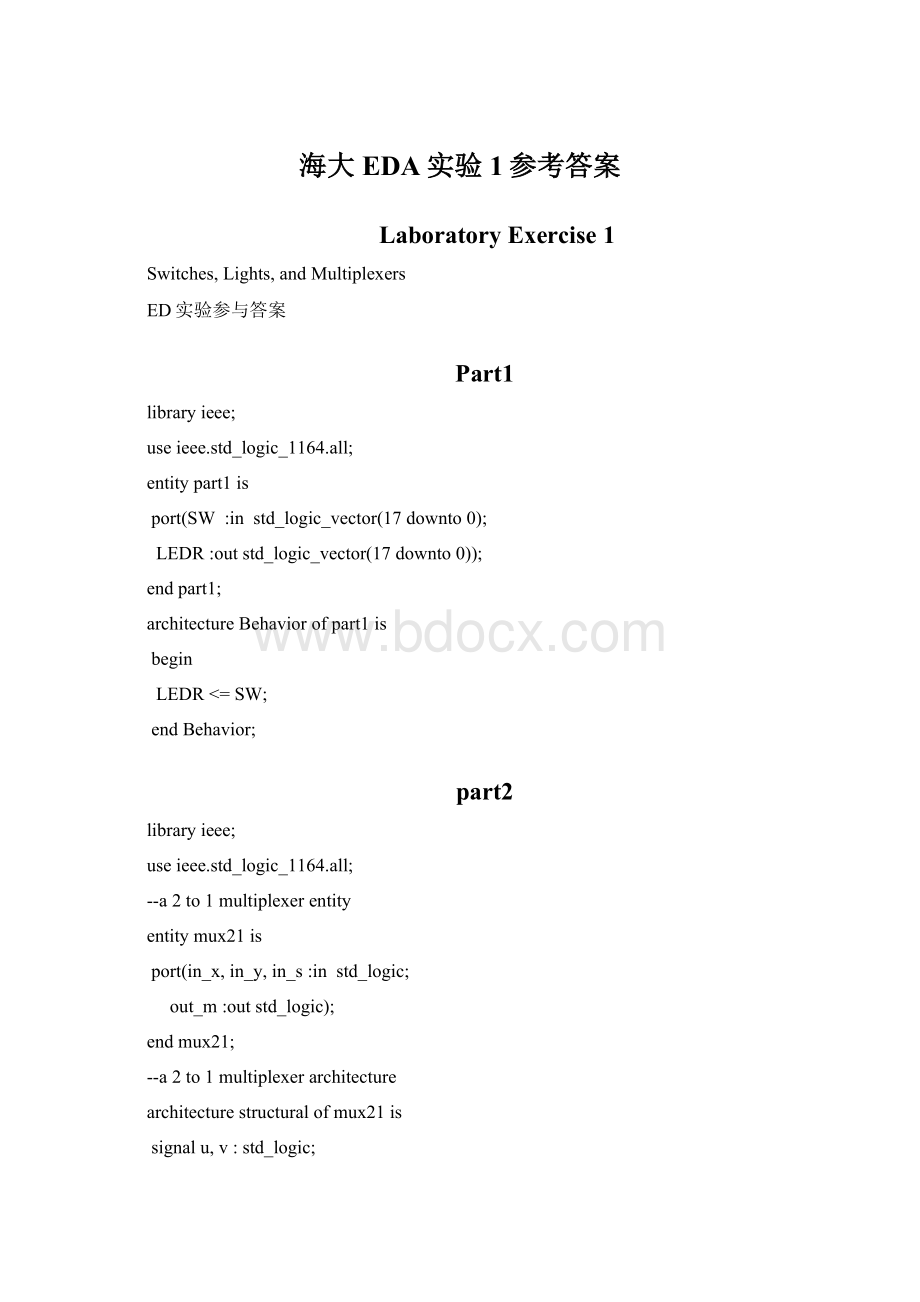

海大EDA实验1参考答案Word文档下载推荐.docx

《海大EDA实验1参考答案Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《海大EDA实验1参考答案Word文档下载推荐.docx(15页珍藏版)》请在冰豆网上搜索。

--a2to1multiplexerarchitecture

architecturestructuralofmux21is

signalu,v:

std_logic;

begin

u<

=in_xand(notin_s);

v<

=in_yandin_s;

out_m<

=uorv;

endstructural;

--aeight-bitwide2to1multiplexer

--eight-bitwide2to1multiplexerentity

entitymux21_8bitis

port(

SW:

instd_logic_vector(17downto0);

--SW:

instd_logic_vector(15downto8);

instd_logic_vector(17downto17);

outstd_logic_vector(7downto0));

endmux21_8bit;

--eight-bitwide2to1multiplexerarchitecture

architectureStructuralofmux21_8bitis

componentmux21

endcomponent;

U1:

mux21portmap(in_x=>

SW(0),in_y=>

SW(8),in_s=>

SW(17),out_m=>

LEDR(0));

U2:

SW

(1),in_y=>

SW(9),in_s=>

LEDR

(1));

U3:

SW

(2),in_y=>

SW(10),in_s=>

LEDR

(2));

U4:

SW(3),in_y=>

SW(11),in_s=>

LEDR(3));

U5:

SW(4),in_y=>

SW(12),in_s=>

LEDR(4));

U6:

SW(5),in_y=>

SW(13),in_s=>

LEDR(5));

U7:

SW(6),in_y=>

SW(14),in_s=>

LEDR(6));

U8:

SW(7),in_y=>

SW(15),in_s=>

LEDR(7));

endStructural;

part3

signalsignal_u,signal_v:

signal_u<

signal_v<

=signal_uorsignal_v;

--a5to1multiplexerentity

entitymux51is

port(in5_u,in5_v,in5_w,in5_x,in5_y,in5_s1,in5_s2,in5_s0:

out5_m:

endmux51;

--a5to1multiplexerarchitecture

architectureStructuralofmux51is

port(in_x,in_y,in_s:

out_m:

signalsignal_a,signal_b,signal_c:

in5_u,in_y=>

in5_v,in_s=>

in5_s0,out_m=>

signal_a);

in5_w,in_y=>

in5_x,in_s=>

signal_b);

signal_a,in_y=>

signal_b,in_s=>

in5_s1,out_m=>

signal_c);

signal_c,in_y=>

in5_y,in_s=>

in5_s2,out_m=>

out5_m);

--a3bit5to1multiplexerentity

entitymux51_3bitis

instd_logic_vector(17downto0);

outstd_logic_vector(17downto0);

LEDG:

outstd_logic_vector(2downto0));

endmux51_3bit;

--a3bit5to1multiplexerarchitecture

architecturestructuralofmux51_3bitis

componentmux51

port(in5_u,in5_v,in5_w,in5_x,in5_y,in5_s1,in5_s2,in5_s0:

out5_m:

begin

=sw;

mux51portmap(in5_u=>

SW(0),in5_v=>

SW(3),in5_w=>

SW(6),in5_x=>

SW(9),in5_y=>

SW(12),

in5_s0=>

SW(15),in5_s1=>

SW(16),in5_s2=>

SW(17),out5_m=>

LEDG(0));

SW

(1),in5_v=>

SW(4),in5_w=>

SW(7),in5_x=>

SW(10),in5_y=>

SW(13),

LEDG

(1));

SW

(2),in5_v=>

SW(5),in5_w=>

SW(8),in5_x=>

SW(11),in5_y=>

SW(14),

LEDG

(2));

endstructural;

part4

--a7-segmentdecoderentity

entitydecoderis

port(decoder_in_3:

instd_logic_vector(2downto0);

HEX0:

outstd_logic_vector(0to6));

enddecoder;

--a7-segmentdecorderarchitecture

architecturebehavioralofdecoderis

process(decoder_in_3)

begin

casedecoder_in_3is

when"

000"

=>

HEX0<

="

0001001"

;

001"

0000110"

010"

1000110"

011"

1000000"

whenothers=>

Hex0<

1111111"

endcase;

endprocess;

endbehavioral;

part5

entitypart5is

port(SW:

instd_logic_vector(17downto0);

HEX0,HEX1,HEX2,HEX3,HEX4:

outstd_logic_vector(6downto0));

endpart5;

architectureBehaviorofpart5is

componentmux51_seg7

port(Mux51_seg7_in:

Seg:

U0:

mux51_seg7portmap(Mux51_seg7_in=>

SW,Seg=>

HEX0);

U1:

mux51_seg7portmap(Mux51_seg7_in(17downto15)=>

SW(17downto15),Mux51_seg7_in(14downto12)=>

SW(11downto9),

Mux51_seg7_in(11downto9)=>

SW(8downto6),Mux51_seg7_in(8downto6)=>

SW(5downto3),

Mux51_seg7_in(5downto3)=>

SW(2downto0),Mux51_seg7_in(2downto0)=>

SW(14downto12),

Seg=>

HEX1);

U2:

SW(8downto6),

SW(5downto3),Mux51_seg7_in(8downto6)=>

SW(2downto0),

SW(14downto12),Mux51_seg7_in(2downto0)=>

HEX2);

U3:

SW(2downto0),Mux51_seg7_in(8downto6)=>

SW(11downto9),Mux51_seg7_in(2downto0)=>

HEX3);

U4:

SW(14downto12),Mux51_seg7_in(8downto6)=>

SW(8downto6),Mux51_seg7_in(2downto0)=>

HEX4);

endBehavior;

-----------------------------------------------------------------------------------------------

-----------Acircuitthatcanselectanddisplayoneoffivecharacters------------------------

entitymux51_seg7is

port(Mux51_seg7_in:

Seg:

endmux51_seg7;

architectureBehaviorofmux51_seg7is

componentmux51_3bit

port(S,U,V,W,X,Y:

M:

outstd_logic_vector(2downto0));

componentchar_7seg

port(C:

Display:

signalM:

std_logic_vector(2downto0);

M0:

mux51_3bitportmap(Mux51_seg7_in(17downto15),Mux51_seg7_in(14downto12),Mux51_seg7_in(11downto9),

Mux51_seg7_in(8downto6),Mux51_seg7_in(5downto3),Mux51_seg7_in(2downto0),M);

H0:

char_7segportmap(M,Seg);

------------------------------a3bitmux51-----------------------------------------------------

------------------------------a3bit5to1multiplexer----------------------------------------

port(S,U,V,W,X,Y:

instd_logic_vector(2downto0);

M:

outstd_logic_vector(2downto0));

mux51portmap(in5_