手把手教你读懂FET选取合适器件Word文档格式.docx

《手把手教你读懂FET选取合适器件Word文档格式.docx》由会员分享,可在线阅读,更多相关《手把手教你读懂FET选取合适器件Word文档格式.docx(12页珍藏版)》请在冰豆网上搜索。

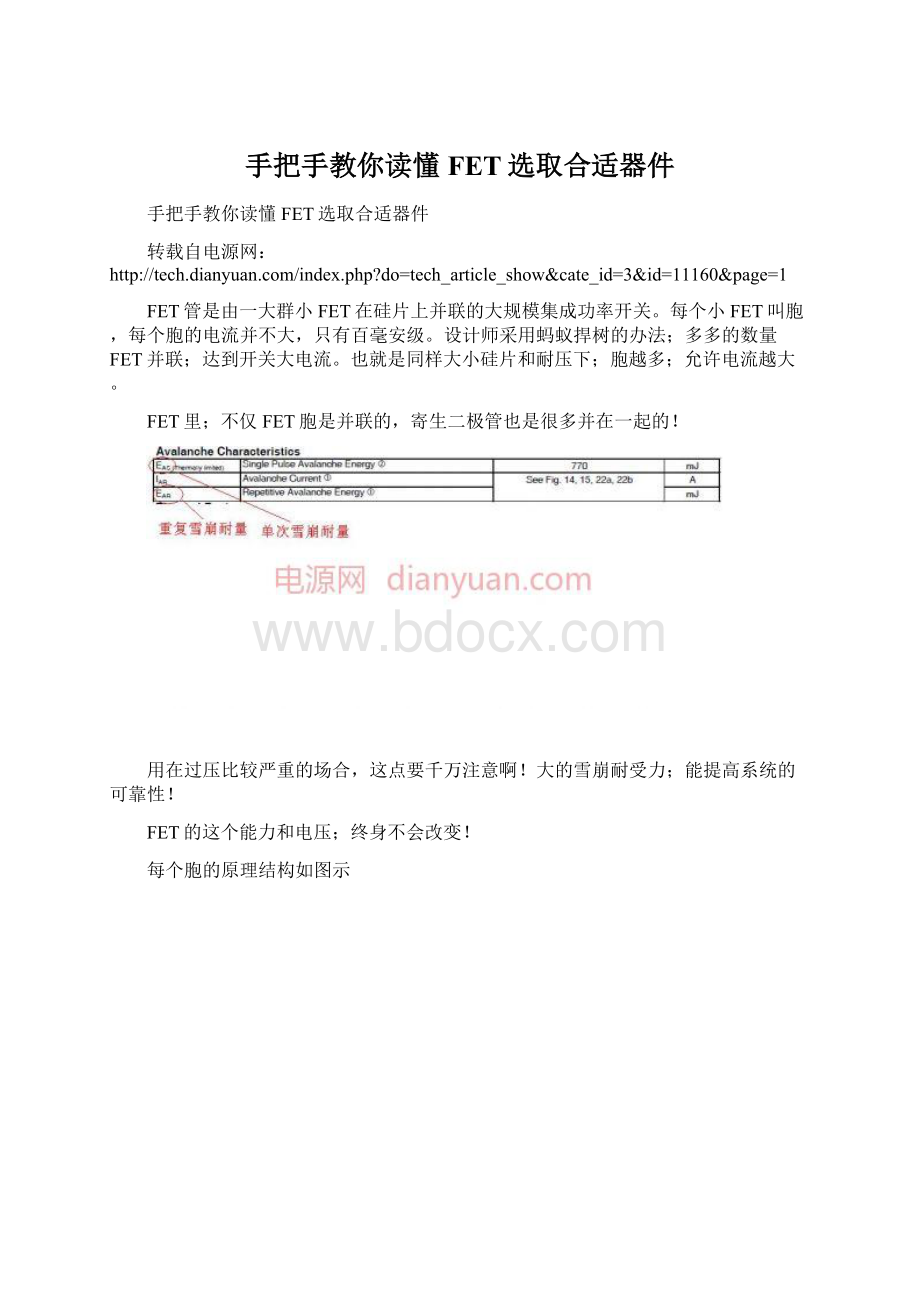

每个胞的原理结构如图示

红色指示的是FET开关的沟道,兰色的是寄生的体二极管。

平时;

FET是关断的。

当栅上加正压时;

在邻近栅的位置;

会吸引许多电子。

这样;

邻近的P型半导体就变成了N型;

形成了连接两个N取的通道(N沟道),FET就通了。

显然;

FET的耐压越高;

沟道越长;

电阻越大。

这就是高压FET的RDSON大的原因。

反之;

P沟FET也是一样的,这里不在叙述。

所以;

功率FET,常被等效为:

场效应晶体管(FieldEffectTransistor缩写(FET))简称场效应管.由多数载流子参与导电,也称为单极型晶体管.它属于电压控制型半导体器件.有3个极性,栅极,漏极,源极,它的特点是栅极的内阻极高,采用二氧化硅材料的可以达到几百兆欧,属于电压控制型器件.具有输入电阻高、噪声小、功耗低、动态范围大、易于集成、没有二次击穿现象、安全工作区域宽等优点,现已成为双极型晶体管和功率晶体管的强大竞争者.

按结构场效应管分为:

结型场效应(简称JFET)、绝缘栅场效应(简称MOSFET)两大类

按沟道材料:

结型和绝缘栅型各分N沟道和P沟道两种.

按导电方式:

耗尽型与增强型,结型场效应管均为耗尽型,绝缘栅型场效应管既有耗尽型的,也有增强型的。

场效应晶体管可分为结场效应晶体管和MOS场效应晶体管,而MOS场效应晶体管又分为N沟耗尽型和增强型;

P沟耗尽型和增强型四大类。

场效应管的主要参数

Idss—饱和漏源电流.是指结型或耗尽型绝缘栅场效应管中,栅极电压UGS=0时的漏源电流.

Up—夹断电压.是指结型或耗尽型绝缘栅场效应管中,使漏源间刚截止时的栅极电压.

Ut—开启电压.是指增强型绝缘栅场效管中,使漏源间刚导通时的栅极电压.

gM—跨导.是表示栅源电压UGS—对漏极电流ID的控制能力,即漏极电流ID变化量与栅源电压UGS变化量的比值.gM是衡量场效应管放大能力的重要参数.

BVDS—漏源击穿电压.是指栅源电压UGS一定时,场效应管正常工作所能承受的最大漏源电压.这是一项极限参数,加在场效应管上的工作电压必须小于BVDS.

PDSM—最大耗散功率,也是一项极限参数,是指场效应管性能不变坏时所允许的最大漏源耗散功率.使用时,场效应管实际功耗应小于PDSM并留有一定余量.

IDSM—最大漏源电流.是一项极限参数,是指场效应管正常工作时,漏源间所允许通过的最大电流.场效应管的工作电流不应超过IDSM

场效应管是电压控制元件,而晶体管是电流控制元件.在只允许从信号源取较少电流的情况下,应选用场效应管;

而在信号电压较低,又允许从信号源取较多电流的条件下,应选用晶体管.

场效应管是利用多数载流子导电,所以称之为单极型器件,而晶体管是即有多数载流子,也利用少数载流子导电,被称之为双极型器件.

有些场效应管的源极和漏极可以互换使用,栅压也可正可负,灵活性比晶体管好.

场效应管能在很小电流和很低电压的条件下工作,而且它的制造工艺可以很方便地把很多场效应管集成在一块硅片上,因此场效应管在大规模集成电路中得到了广泛的应用.

FET是实实在在的物质构成的;

里面有导体/半导体/绝缘体。

这些物质的相互搭配;

做成了FET。

那么;

任何两个绝缘的导体,自然构成了物理电容——寄生电容。

红色的就是DS间的寄生电容Coss。

蓝色的就是密勒电容Cgd。

黑色的就是栅原电容Cgs。

Cgd+Cgs=Ciss——输入电容

Coss——输出电容

Cgd/Cds在理论上存在,在数据表中也有所列。

在微变等效中也可以作为参量计算分析,但;

也仅在线性放大里的微变等效分析中有所使用。

在开关过程的工程分析中,变态的变化导致只能用电荷量这个值来衡量。

Qgd就是Cdg储存的电荷量(弥勒电荷),Qds是Cds储存电荷量。

下面;

分析这些电荷在开/关状态下,是如何影响FET工作的。

FET静态关断时,Cgd/Cgs充电状态如图示:

栅电压为零,Qgs=0。

Qgd被充满,Vgd=Vds。

注:

由于Cds通常和其它杂散电容并联在一起;

共同对电源施加影响,因此;

这里暂时不做分析。

问题将在后面和杂散参数一起一并讨论。

给FET的栅极施加正脉冲。

由于Cgd在承受正压时,电容量非常小(Cgd虽然小;

但是Qgd=Cgd*Ugd,Qgd仍然是很大的),Cgs远大于Cgd。

因此;

脉冲初期,驱动脉冲主要为Cgs充电,直到FET开始开启为止。

开启时;

FET的栅电压就是门槛电压Vth。

大多数情况下;

栅电压达到Vth前,只有很小的电流流过FET。

FET一直处于关断状态。

当FET栅电压达到Vth,FET开始导电。

无论负载在漏极还是在源极,都将因有电流流过而承受部分或全部电压。

这样FET将经历由阻断状态时承受全部电压逐渐变到短路而几乎没有电压降落为止的过程。

这个过程中,Cgd同步经历了放电过程。

放电电流为I=Qgd/ton。

Igd——密勒电流分流了FET的驱动电流!

使得FET的栅电压上升变缓。

弥勒电荷越大;

这个斜坡越长。

弥勒电荷不仅和器件有关还和漏极电压有关。

一般;

电压越高;

电荷量越大。

FET的栅电压达到Vth后;

电流流过FET的沟道,此时;

FET工作在线性区。

FET视在斜率随Id大小变化而变。

但;

从Vg、Id的变化量看,两者之比就是FET跨到S。

即S=(Id2-Id1)/(Vgs2-Vgs1)。

其中;

同样粗细的亮色线为一组;

代表各自的Vg和Id的关系。

由于在FET开的过程中,栅电压变缓,是弥勒电容分流引起的,所以;

也叫弥勒效应区。

在断续反激电源里,弥勒效应区的栅电压斜率基本不变。

而正激、半/全桥等;

斜率随负载而变。

弥勒效应时间(开关时间)ton/off=Qgd/Ig

1)Ig指FET的栅驱动电流。

FET“ON”

Ig=(Vb-Vth)/Rg

2)Vb:

稳态栅驱动电压

FET经过弥勒区后;

完全导通。

原先阻断D-S的PN结被开启的沟道短路。

由于失去了部分绝缘层,Cgd变大;

以至和Cgs相当。

并且;

Cgd通过低阻抗的开启沟道;

和Cgs实现物理上的并联。

使得后期的驱动栅电压沿发生了变化。

如图示:

FET的关断过程和开启过程的物理变化是一样的,只是过程刚好相反。

自己分析一下!

让我们分享一下你的成果!

如前面介绍,完整周期的驱动波型如图示:

贴个典型实测栅&VD的波型,体验一下其中的奥妙。

仔细看看FET沟道部分结构,大家看;

是否可以拼出这来:

如ZVS/同步整流。

反向回复时间和电荷量决定了电源的效率和电磁噪音。

看trr和Qrr

trr是二极管恢复时间;

Qrr是恢复电荷量。

在电路里;

类似在FET的DS间并联电容。

这两个值越大;

电容量也越大。

这个电容值还和温度和实际流过二极管的电流大小有关。

电流越大;

温度越高,等效电容越大。

在对比不同数据表时;

一定要看清测试条件。

否则;

劣管也能标出好参数的。

这里;

二极管流过电流时间基本和Qrr&

trr无关。

EAR/EAS这两个量描述的是FET抗雪崩击穿的能力。

EAR描述的是可重复的雪崩耐量。

EAS描述的是单次耐量。

如在小功率反激里;

取消RCD吸收后,大电流负载时的漏极电压就需要EAR这个量来考核安全。

再如大电流半/全桥电路里,桥短路时电流非常大;

即便在安全工作区能关断FET;

仍会因引线等杂散寄生电感的作用而产生过压,当关的比较快时;

过压就会超过FET耐压极限而击穿。

EAS是衡量FET此时是否安全的参量...这里只列举了这两个量的概念了两个实际工程中的应用实例。

它们的意义远非这些。

这是这两个量的典型图表:

安全工作区SOA

先看这两张图:

这是两个同为600V的MOSFET,都能在600V下承受最大饱和电流。

即在15V栅压时;

MOSFET能流过的最大电流(MOSFET进入了线性区;

呈恒流状态),此时的电流不随电压增高而增加!

状态位置见图中兰圈内的红线区域(最大到600V,呵呵有些画过了):

这两个FET都能在这电压电流下挺住,但;

能坚持的时间却不一样。

左边图显示;

能挺1微秒,而右侧约能挺10微秒。

(电源网原创转载请注明出处)