计算机体系课后答案文档格式.docx

《计算机体系课后答案文档格式.docx》由会员分享,可在线阅读,更多相关《计算机体系课后答案文档格式.docx(18页珍藏版)》请在冰豆网上搜索。

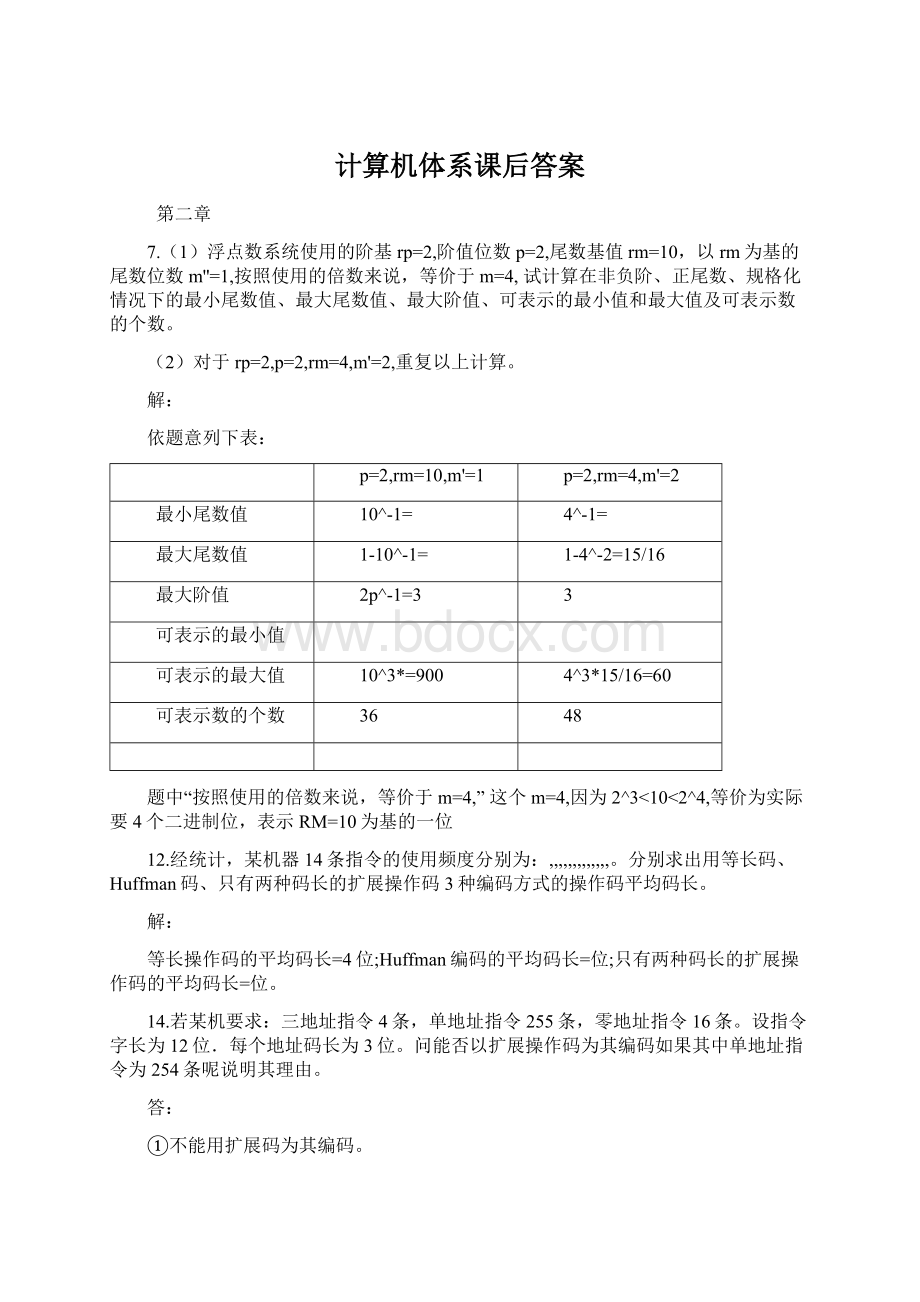

3

可表示的最小值

可表示的最大值

10^3*=900

4^3*15/16=60

可表示数的个数

36

48

题中“按照使用的倍数来说,等价于m=4,”这个m=4,因为2^3<

10<

2^4,等价为实际要4个二进制位,表示RM=10为基的一位

12.经统计,某机器14条指令的使用频度分别为:

,,,,,,,,,,,,。

分别求出用等长码、Huffman码、只有两种码长的扩展操作码3种编码方式的操作码平均码长。

等长操作码的平均码长=4位;

Huffman编码的平均码长=位;

只有两种码长的扩展操作码的平均码长=位。

14.若某机要求:

三地址指令4条,单地址指令255条,零地址指令16条。

设指令字长为12位.每个地址码长为3位。

问能否以扩展操作码为其编码如果其中单地址指令为254条呢说明其理由。

答:

①不能用扩展码为其编码。

∵指令字长12位,每个地址码占3位;

∴三地址指令最多是2^(12-3-3-3)=8条,现三地址指令需4条,

∴可有4条编码作为扩展码,

∴单地址指令最多为4×

2^3×

2^3=2^8=256条,

现要求单地址指令255条,∴可有一条编码作扩展码

∴零地址指令最多为1×

2^3=8条

不满足题目要求

∴不可能以扩展码为其编码。

②若单地址指令254条,可以用扩展码为其编码。

∵依据①中推导,单地址指令中可用2条编码作为扩展码

∴零地址指令为2×

2^3=16条,满足题目要求

note:

三地址指令格式:

操作码地址码地址码地址码

3位3位3位3位

单地址指令格式:

操作码地址码

9位3位

所以前面9位由于三地址指令用了最前面3位,还有中间6位可作为编码(也就是总共可以有9位作为单地址指令的指令操作码的编码)。

减去3地址指令的4条,有4*2^6=256条,但由于韪目要求要有255条,所以剩下一个编码,已经用了9位的全部编码,最后零地址指令(全部12位都可作为操作码的编码)还有1*2^3=8(这是12位编码中最后三位的)若只要求254种,则可以有(256-254)*2^3=16条

15.某机指令字长16位。

设有单地址指令和双地址指令两类。

若每个地址字段为6位.且双地址指令有X条。

问单地址指令最多可以有多少条

单地址指令最多为(16-X)×

2^6

.双地址指令最多是2^(16-6-6)=2^4=16条,现双地址指令有X条,

∴可有(16-X)条编码作为扩展码,

∴单地址指令最多为(16-X)×

2^6=256条

第三章

4.设中断级屏蔽位“1”对应于开放,“0”对应于屏蔽,各级中断处理程序的中断级屏蔽位设置如下:

中断处理程序级别

中断级屏蔽位

1级

2级

3级

4级

第1级

第2级

1

第3级

第4级

(1)当中断响应优先次序为1→2→3→4时,其中断处理次序是什么

(2)如果所有的中断处理都各需3个单位时间,中断响应和中断返回时间相对中断处理时间少得多。

当机器正在运行用户程序时,同时发生第2,3级中断请求,过两个单位时间,又同时发生第1,4级中断请求,试画出程序运行过程示意图。

(1)当中断响应优先次序为1→2→3→4时,其中断处理次序为1→3→4→2。

(2)

5.若机器共有5级中断,中断响应优先次序为1→2→3→4→5,现要求其实际的中断处理次求序1→4→5→2→3。

(1)设计各级中断处理程序的中断级屏蔽位(令“1”对应于开放,“0”对应于屏蔽);

(2)若在运行用户程序时,同时出现第4,2级中断请求,而在处理第2级中断未完成时,又同时出现第1,3,5级中断请求,请画出此程序运行过程示意图。

(1)中断级屏蔽位设置如下图:

5级

第5级

(2)中断过程示意图:

如图

2、4中断同时出现,进行排队器。

首先响应第2级中断请求,屏蔽字为01100,表明其对第4级中断请求开放,所以转去响应第4级中断请求并进行处理。

响应4,中断4运行结束,回2。

1、3、5进入排队器。

第2级中断请求的处理请求被中断,转去响应第1级中断请求并进行处理。

响应第5级中断请求并进行处理。

继续响应并处理第2级中断处理请求,结束后返回用户程序。

最后处理第3级中断请求。

10.通道型I/O系统由一个字节多路通道A(其中包括两个子通道Al和A2),两个数组多路通道B1和B2及一个选择通道C构成,各通道所接设备和设备的数据传送速率如表所示。

(1)分别求出各通道应具有多大设计流量才不会丢失信息;

(2)设I/O系统流量占主存流量的1/2时才算流量平衡,则主存流量应达到多少

通道号

所接设备的数据传送速率(KB/s)

字节多路通道

子通道A1

5035202050352020

子通道A2

数组多路通道B1

500400350250

数组多路通道B2

选择通道C

(1)要不丢失信息,各通道需要达到的流量:

字节多路通道子通道A1:

S;

字节多路通道子通道A2:

数组多路通道B1:

500KB/s;

数组多路通道B2:

选择通道C:

500KB/s。

(2)主存流量应达到4MB/S。

剖析:

(1)设备要求字节多路通道或其子通道的实际最大流量,是该通道所接各设备的字节传送速率之和;

设备要求数组多路通道或选择通道的实际最大流量,是该通道所接各设备的字节传送速率中的最大者。

(2)I/O系统中,各种通道和子通道可以并行工作,因此,I/O系统的最大流量应等于各通道最大流量之和。

第4章

4.某虚拟存储器共8个页面,每页1024个字,实际主存为4096个字,采用页表法进行地址映象。

映象表的内容如下表所示。

虚页号

2

4

5

6

7

实页号

装入位

注:

我把虚页号加上了。

(1)列出会发生页面失效的全部虚页号;

(2)按以下虚地址计算主存实地址:

0,3728,1023,1024,2055,7800,4096,6800。

解:

(1)会发生页面失效的全部虚页号为:

2,3,5,7。

虚地址

页内位移

实地址

3072

3278

656

页面失效

无

1023

4095

1024

2055

7800

632

4096

2048

6800

剖析:

(1)根据页表法列出表2,当装入位为0时,即为页面失效,再找出相对应的虚页号即可。

(2)虚页号=虚地址/页面大小

页内位移量=虚地址-虚页号*页面大小

实地址=实页号*页面大小+页内位移量

由于可以用替换算法解决页面失效的问题,所以,发生页面失效的虚页2,3,5,7仍然可以有相应的实地址,但这样要在页表中建立新的虚实地址对应关系,新的虚实地址对应关系和原来的对应关系相同的可能性就很小了。

6.设某程序包含5个虚页,其页地址为4,5,3,2,5,1,3,2,2,5,1,3。

当使用LRU算法替换时,为获得最高命中率,至少应分配给该程序几个实页其可能的最高命中率为多少

12.有一个Cache存储器。

主存共分8个块(0~7),Cache为4个块(0~3),采用组相联映象,组内块数为2块,替换算法为近期最少使用算法(LRU)。

(1)画出主存、Cache地址的各字段对应关系(标出位数)图;

(2)画出主存、Cache空间块的映象对应关系示意图;

(3)对于如下主存块地址流:

1,2,4,1,3,7,0,1,2,5,4,6,4,7,2,如主存中内容一开始未装入Cache中,请列出Cache中各块随时间的使用状况;

(4)对于(3),指出块失效又发生块争用的时刻;

(5)对于(3),求出此期间Cache的命中率。

解答:

(1)主存地址、Cache地址的各字段的位数及其对应关系如下图所示

(2)主存块、Cache块的映象对应关系如下图所示

(3)Cache中各块随时间的使用状况如下图所示。

图中标*号的是候选替换块的块号,H:

命中;

R:

替换;

L:

失效。

(4)发生块失效又发生块争用的时刻有6、7、9、10、11、12、14、15。

(5)Cache的块命中率Hc=3/15=。

由于主存块、Cache块之间存在上述的映象对应关系,主存的第0、1、4、5块只能映象装入或替换物理Cache的第0、1块;

主存的第2、3、6、7块只能映象装入或替换物理Cache的第2、3块。

第5章

3.假设指令的解释分取指、分析与执行3步,每步的时间相应为t取指、t分析、t执行,

(1)分别计算下列几种情况下,执行完100条指令所需时间的一般关系式:

a.顺序方式;

b.仅“执行k”与“取指k+1”重叠;

c.仅“执行k”、“分析k+1”、“取指k+2”重叠;

(2)分别在t取指=t分析=2、t执行=1及t取指=t执行=5、t分析=2两种情况下,计算出上述各结果。

(1)执行完100条指令所需时间:

*(t取指+t分析+t执行);

取指+100*t分析+99*max(t取指+t执行)+t执行;

取指+max(t取指+t分析)+98*max(t取指+t分析+t执行)+max(t分析+t执行)+t执行。

(2)在t取指=t分析=2、t执行=1的情况下,执行完100条指令所需时间:

在t取指=t执行=5、t分析=2的情况下,执行完100条指令所需时间:

5.流水线有4个功能部件组成,每个功能部件的延迟时间为△t,当输入10个数据后间歇5△t又输入10个数据,如此周期性地工