51 四人抢答器设计Word文档下载推荐.docx

《51 四人抢答器设计Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《51 四人抢答器设计Word文档下载推荐.docx(11页珍藏版)》请在冰豆网上搜索。

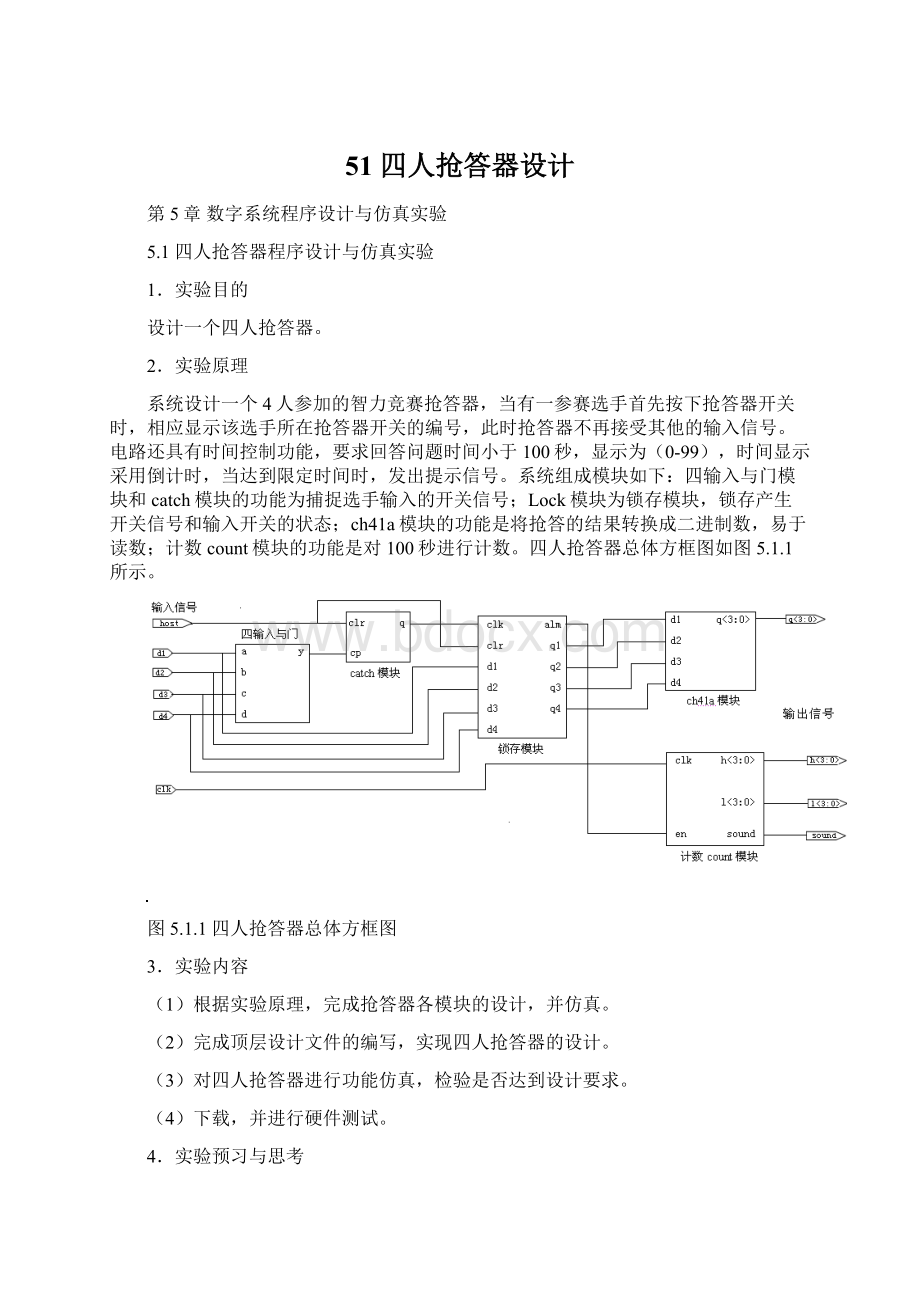

(4)下载,并进行硬件测试。

4.实验预习与思考

(1)考虑四人抢答器设计中信号传递的时间延迟方法。

(2)如何实现当已经有选手输入抢答信号后对其他选手的输入信号进行屏蔽。

5.程序设计与仿真

(1)程序设计

①四输入与门模块(略)。

libraryieee;

useieee.std_logic_1164.all;

entityand4is

port(a,b,c,d:

instd_logic;

z:

outstd_logic);

endand4;

architecturemediedofand4is

begin

z<

=(aandb)and(candd);

endmedied;

②catch模块(catch.vhd)源程序如下,RTL电路如图5.1.2所示。

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitycatchis

Port(cp:

--脉冲

clr:

--复位信号

q:

outstd_logic);

endcatch;

architectureBehavioralofcatchis

process(cp,clr)

begin

ifclr='

0'

then

q<

='

;

elsifcp'

eventandcp='

1'

endif;

endprocess;

endBehavioral;

图5.1.2catch模块RTL电路

③Lock模块(lock.vhd)为锁存模块,锁存产生开关信号时和输入开关的状态,锁存模块源程序如下,RTL电路图略。

entitylockis

Port(d1:

--四位选手的输入信号

d2:

d3:

d4:

clk:

--复位

q1:

outstd_logic;

--锁存数据输出

q2:

q3:

q4:

alm:

--提示信号

endlock;

architectureBehavioraloflockis

process(clk)

q1<

q2<

q3<

q4<

alm<

elsifclk'

eventandclk='

=d1;

=d2;

=d3;

=d4;

④ch41a模块(ch41a.vhd),此模块的功能是将抢答的结果转换成二进制数,易于读数,源程序如下,RTL电路图略。

entitych41ais

--选手信号

outstd_logic_vector(3downto0));

--输出

endch41a;

architectureBehavioralofch41ais

process(d1,d2,d3,d4)

variabletmp:

std_logic_vector(3downto0);

tmp:

=d1&

d2&

d3&

d4;

casetmpis

when"

0111"

=>

q<

="

0001"

1011"

0010"

1101"

0011"

1110"

0100"

whenothers=>

1111"

endcase;

endprocess;

⑤count模块(count.vhd),本模块的功能是对100秒进行计数。

count模块源程序如下,RLT电路图略。

entitycountis

Port(clk:

--输入时钟

en:

--使能

h:

outstd_logic_vector(3downto0);

--计时高位

l:

--计时低位

sound:

--计满提醒

endcount;

architectureBehavioralofcountis

process(clk,en)

variablehh,ll:

ifclk'

ifen='

ifll=0andhh=0then

sound<

elsifll=0then

ll:

1001"

hh:

=hh-1;

else

=ll-1;

sound<

h<

=hh;

l<

=ll;

⑥顶层设计文件(ans_top.vhd),源程序如下:

RTL电路如图5.1.3所示。

entityans_topis

--抢答输入的四个开关信号,低电平有效

host:

--系统时钟

--开关显示输出信号

h,l:

outstd_logic_vector(3downto0);

--计时输出,分高低两位

sound:

outstd_logic);

--限定时间完毕提醒,低电平有效

endans_top;

architectureBehavioralofans_topis

componentcatch

endcomponent;

componentch41a

componentcount

componentlock

componentmy_and4

Port(a:

b:

c:

d:

y:

signalsq1,sq2,sq3,sq4,sq5,sq6,sq7:

std_logic;

u0:

my_and4portmap(a=>

d1,b=>

d2,