CMOS闩锁效应Word格式.doc

《CMOS闩锁效应Word格式.doc》由会员分享,可在线阅读,更多相关《CMOS闩锁效应Word格式.doc(9页珍藏版)》请在冰豆网上搜索。

例如Q1开启,它会提供足够大的电流给R2,使得R2上的压降也达到0.7V,这样R2也会开启,同时,又反馈电流提供给Q1,形成恶性循环,最后导致大部分的电流从VDD直接通过寄生晶体管到GND,而不是通过MOSFET的沟道,这样栅压就不能控制电流KyechongKima,AgisA.Iliadis,Latch-upeffectsinCMOSinvertersduetohighpowerpulsedelectromagneticinterference

。

2.2集总元件上

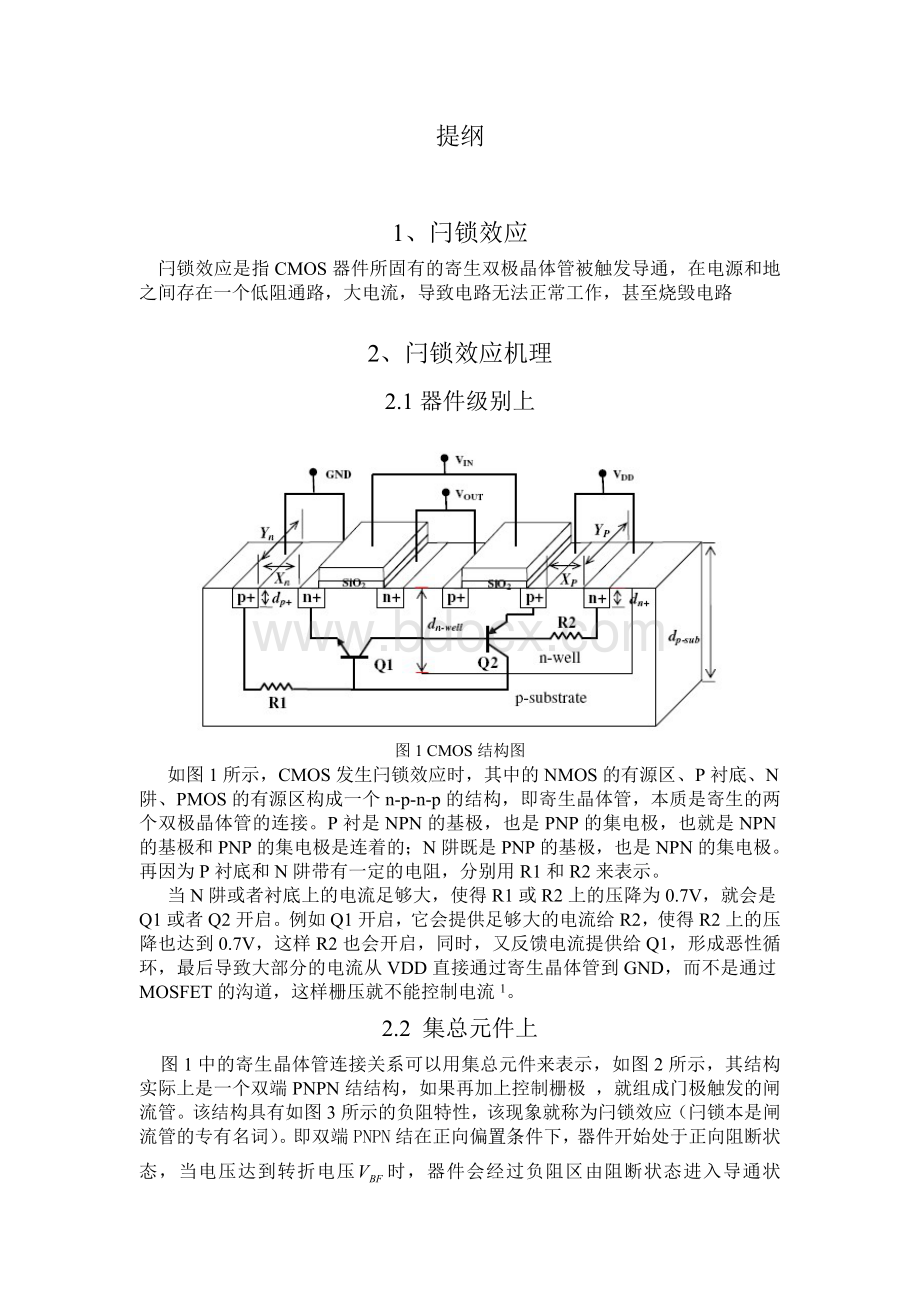

图1中的寄生晶体管连接关系可以用集总元件来表示,如图2所示,其结构实际上是一个双端PNPN结结构,如果再加上控制栅极,就组成门极触发的闸流管。

该结构具有如图3所示的负阻特性,该现象就称为闩锁效应(闩锁本是闸流管的专有名词)。

即双端PNPN结在正向偏置条件下,器件开始处于正向阻断状态,当电压达到转折电压时,器件会经过负阻区由阻断状态进入导通状态.这种状态的转换,可以由电压触发(=0),也可以由门极电流触发(≠O)。

门极触发大大降低了正向转折电压。

图2PNPN双端器件

从上图可以推导出如下的关系

其中,分别是PNP和NPN共基极增益,是集电极饱和电流。

对上式进行调整,得到如下关系:

其中

在低阻抗时,可以忽略,另,在一般情况下,,可以发现

或者

其中

代表在阻止闩锁上起的作用,=1表示所有的发射极电流都绕过电阻,也就是没有闩锁效应发生。

在有载流子产生的情况下,在

(2)式右边添加上GENDA.HU,ABetterUnderstandofCMOSLatch-Up

两个寄生晶体管工作时,形成正反馈电路,加深可控硅导通,造成的结果在器件级的描述一样,一股大的电流将由电源流向接地端,导致一般正常电路工作中断,甚至会由于高电流散热的问题而烧毁芯片

3、闩锁效应与器件参数的关系

3.1尺寸和浓度

根据先前论文CarlesCane,ManuelLozano,EnricCabruja,Latch-UpCharacterizationUsingNovelTestStructuresandInstruments

得知,器件尺寸越小,越容易发生闩锁效应,因为尺寸越小,基区宽度越小,电流放大系数越高,根据一般的闩锁效应发生的条件,越容易满足这个条件。

在浓度上,由前面的论述可知,R越小,越不容易发生闩锁效应,所以重掺杂可有效的减小闩锁效应的发生。

3.3器件的结构

SOI结构有效的阻止了电子和空穴从源到地之间的通路,能从根本上消除闩锁的发生。

RetrogradedWell,倒阱,用高能离子注入将杂质打入阱底部,使得阱底浓度最高,阱表面浓度最低,高浓深阱可以有效的增加复合,减少到达底部的电子浓度。

4、闩锁效应触发条件

4.1产生条件

①电路要能进行开关转换,其相关的PNPN结构的回路增益必须大于1。

②必须存在一种偏置条件,使两只双极型晶体管导通的时间足够长。

以使通过阻塞结的电流能达到定义的开关转换电流的水平。

一般来说,双极管的导通都是由流过一个或两个发射极/基极旁路电阻的外部激发电流所引起的。

③偏置电源和有关的电路,必须能够提供至少等于PNPN结构脱离阻塞态所需的开关转换电流和必须能提供至少等于使其达到闩锁态的保持电流。

4.2触发方式

①输入或输出节点的上冲或下冲的触发,使第一个双极型晶体管导通,然后再使第二个双极型晶体管导通。

当流入寄生PNPN结构的总电流达到开关转换电流时,闩锁就发生。

②当流过阱一衬底结的雪崩电流、光电流及位移电流,同时通过两个旁路电阻、时,旁路电阻较大的晶体管先导通。

然而要使闩锁发生,第二个双极型晶体管必须导通。

同时通过PNPN结构的总电流必须达到开关转换电流。

③穿通、场穿通或漏结雪崩的电流,给PNPN结构的电流达到取消被激发晶体管旁路电阻形成的三极管结构计算的开关转换电流时,至少会发生瞬时闩锁,若总电流也能达到四极管结构开关转换电流,即闩锁将维持下去王新,CMOS集成电路闩锁效应形成机理和对抗措施

5.HPM定义

脉冲功率从100MW到10GW,或平均功率为1MW以上;

频谱范围从300MHz到30GHz

典型的HPM的电磁脉冲如下图所示。

包络线里面的小脉冲的持续时间小于1个纳秒,包络线的持续时间从10ns到100s之间G.VenugopalaRao,AmitavaRoy,ELECTROMAGNETICINTERFERENCEHIGHPOWERMICROWAVES

UWB也包含在HPM中,论文[1]中使用的EMI功率很小,只有3.55w。

6.HPM激发闩锁效应的机理

在论文[1]中,作者认为HPM使得CMOS结构中产生过剩载流子,属于4.2给出的触发条件3,即过剩载流子流入N阱或者P衬底,从而触发其中一个晶体管的开启。

这个过剩载流子怎么产生作者没有明说,我个人认为是HPM作用下,结处产生雪崩击穿,产生大量的电子空穴对。

[1]中HPM的其中一个参数是1.23Ghz,最高给出25.5dBm,按照公式dBm=10log[功率mw]来计算,功率很小,结合论文[6]KyechongKim,Effectsofmicrowaveinterferenceontheoperationalparametersofn-channelenhancementmodeMOSFETdevicesinCMOSintegratedcircuits

当从栅极注入1GHz,30dBm时,I-V特性曲线显示沟道形成强反型层,没有饱和区,直接进入击穿区,可以说明latchup的形成是雪崩击穿而不是二次击穿(即热击穿,会激发本征载流子),否则I-V特性曲线会呈现电阻的特性。

从另外一篇论文,老师你的,

器件编号

损伤/失效功率

损伤/失效现象

1#

100W

失去功能,呈电阻特性

5#

10W

特性退化

6#

70W

8#

失去功能,呈二极管特性

9#

44W

功率为达到40w时,器件只呈现电阻特性,说明MOS管以烧毁,推广到CMOS管,在这个功率下器件也会烧毁。

从同一篇论文中对双极器件的实验得出结论可知,双极的损伤功率远远大于MOS器件,现在的问题是,注入CMOS管的功率大于40w,寄生晶体管还存在吗,还能引起闩锁效应吗,闩锁效应还是不是器件烧毁的主要因素。

7.闩锁效应和HPM参数的关系

HPM的参数有频率,功率,持续时间,重复频率,脉冲宽度等。

7.1频率

在论文[6]中,讨论了HPM频率的关系。

实验中出现一个有趣的现象,1Ghz,30dBm时,I-V特性曲线变形,但是频率到5Ghz,30dBm时,特性曲线又基本恢复正常,作者给的解释是高功率效应被高频率给压制了,但没给出具体的原因。

在论文[1]中,激发闩锁效应所需的功率也是随着频率的增大而增大,因为频率越大,电容旁路效应也明显。

至于功率,很明显,功率越大越容易引发闩锁效应,和前面6小节的问题一样,功率达到什么程度引发的器件烧毁却不是latchup引起的烧毁,需要进一步仿真研究。

7.2脉宽

在论文[7]S.Bargstadt-Franke,W.Stadler,TransientLatch-up:

ExperimentalAnalysisandDeviceSimulation

中,给出的不同脉宽和latchup触发电流的关系,可以看出,脉宽越大,触发电流越小

8.闩锁效应实验现象

论文[1]中的实验现象是:

开始时EMI功率很小,反相器的输出会出现比特翻转错误,但是关闭EMI,又可恢复正常,随着反EMI功率的不断增大,比特翻转错误达到的下限电压不断增大,最后是不可恢复,除非复位VDD。

论文没有给出I-V特性曲线。

论文[2]中的给出出现闩锁时的I-V特性曲线:

出现了负阻

论文[7]给出的一个变量,TLUtriggercurrent,以这个变量来作为器件的latchup的灵敏度。

和脉宽的关系

、

和上升时间的关系

器件内部的电子分布

9.闩锁效应的仿真

9.1器件级别

在论文[7]中,作者在DESSIS上对器件进行仿真。

图9.1为仿真的示意图,比较抽象,只能提供思路。

具体如图9.2所示,为静态latchup和瞬态latchup仿真的通用连接示意图,n阱连接VDD,衬底接地,一个正向的脉冲添加到VDD。

图9.1仿真搭建示意图

图9.2仿真连接图

图9.3进行仿真器件的横截面图

9.2电路级别上的

电路级别上的仿真的问题是,是用SPICE画出MOSFET寄生晶体管的的集总元件的连接图?

在实验中,电路级别上容易实现,因为都是在版图上实现,就像论文[1]中所示,两个级联的反相器,出现latchup是这个CMOS结构在版图上实现的所特有的,但是怎么在仿真中实现,如果用DESSIS,那和器件级别的仿真有什么不同。

这些问题还不知道。