FPGA实验1原理图输入与仿真及由原理图生成元器件模块实验Word格式.docx

《FPGA实验1原理图输入与仿真及由原理图生成元器件模块实验Word格式.docx》由会员分享,可在线阅读,更多相关《FPGA实验1原理图输入与仿真及由原理图生成元器件模块实验Word格式.docx(8页珍藏版)》请在冰豆网上搜索。

2、对已完成的原理图进行Verilog转换和仿真测试。

3、学习观察器件下级原理图及由原理图生成模块的方法。

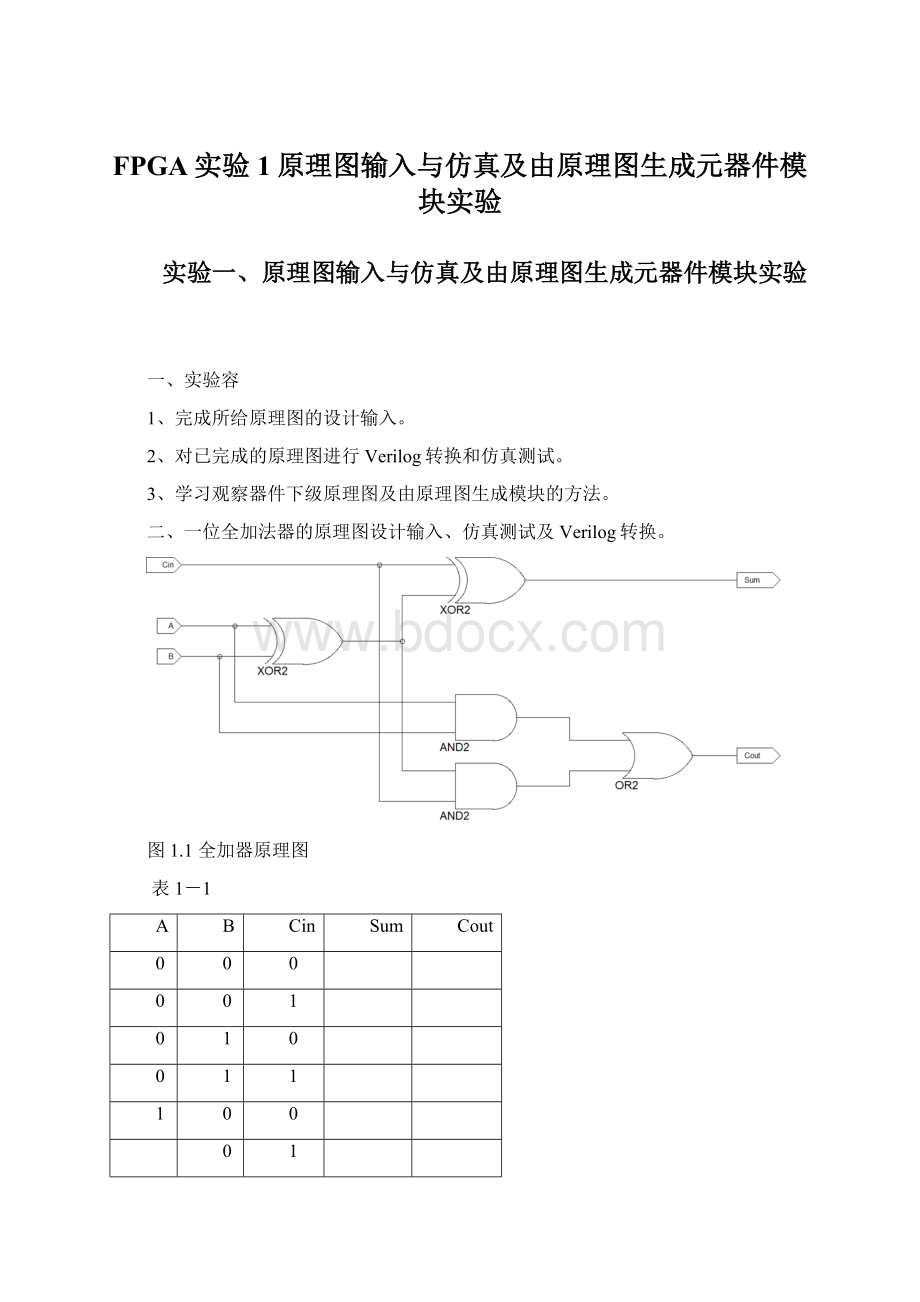

二、一位全加法器的原理图设计输入、仿真测试及Verilog转换。

图1.1全加器原理图

表1-1

A

B

Cin

Sum

Cout

1

1)新建一个项目名为LAB项目,点击菜单ProjectNewSource,选择添加类型为Schematic(参见图1.2——图1.4),完成如图1.1原理图的设计输入。

图1.2创建新工程

图1.3设置工程属性

图1.4新建原理图输入

2)添加测试代码,新建用XST或ModelSimSimulator进行仿真测试(参见图1.5——图1.9),将仿真结果填入一位全加法器真值表1-1中。

图1.5添加测试模块

图1.6关联被测试模块

图1.7添加激励测试代码

图1.8检查语法后点击仿真

图1.9仿真结果

3)确认项目的属性中preferredlanguage为Verilog,利用生成器将原理图转换为Verilog描述的语言。

(如图1-10所示)

图1.10

4)将原理图转换为symbol,以便能在其他原理图中使用。

(如图1-11所示)

图1.11

三、新建一个原理图文件Comp,在原理图中插入生成的图标myadder(如图1.12)。

图1.12

四、选中myadder模块,按下push按钮,即可查看该模块的下级原理图(如图1.13)。

图1.13

五、参照以上步骤,在Comp中完成图1.14的二位比较器原理图的设计输入。

并进行仿真测试及Verilog转换,并将仿真结果填入表1-2。

表1-2

A与B的关系

Q值

A>

A<

A=B

图1.14