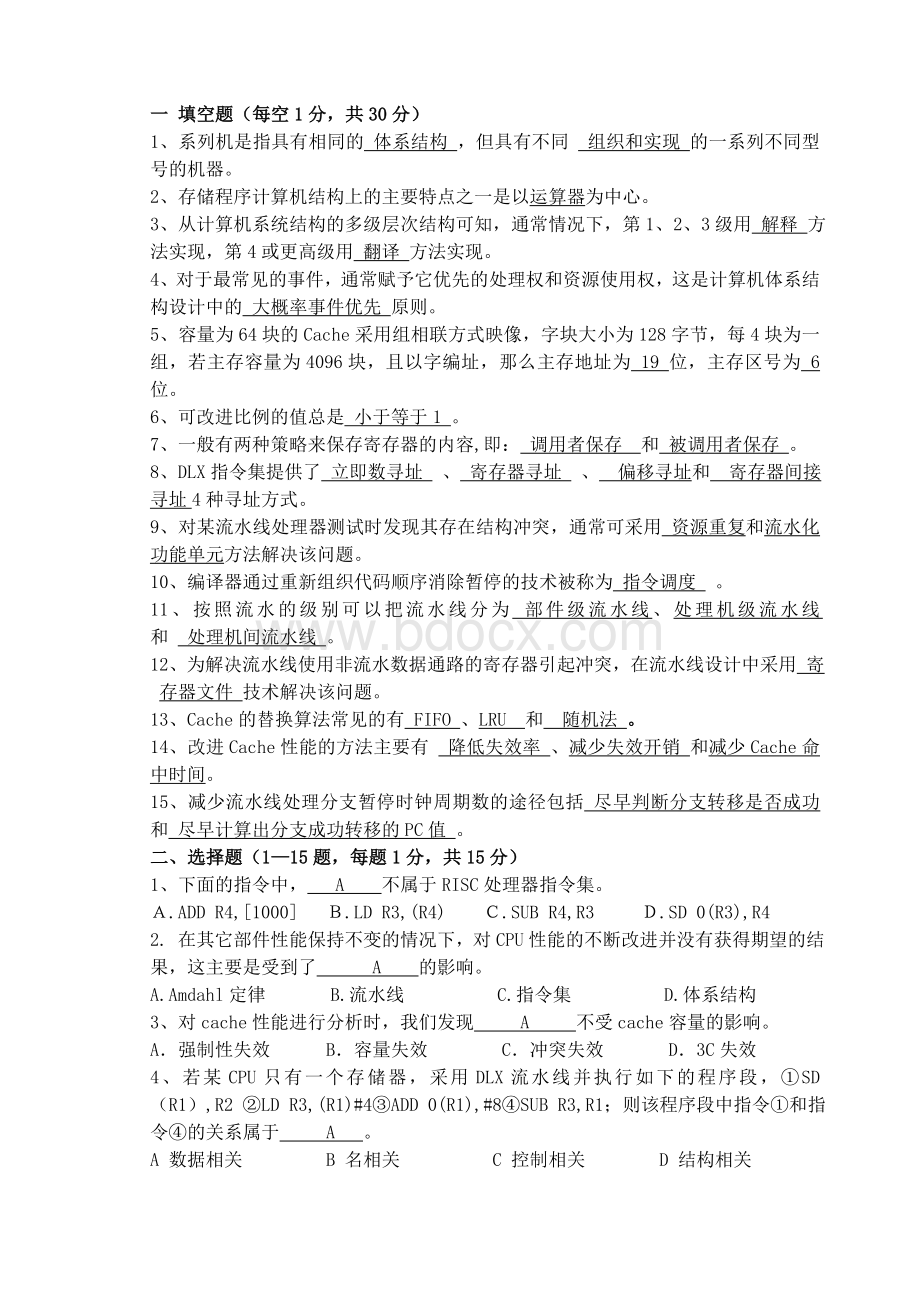

计算机体系结构试卷试题(答案全)Word文档下载推荐.doc

《计算机体系结构试卷试题(答案全)Word文档下载推荐.doc》由会员分享,可在线阅读,更多相关《计算机体系结构试卷试题(答案全)Word文档下载推荐.doc(5页珍藏版)》请在冰豆网上搜索。

1、下面的指令中,A不属于RISC处理器指令集。

A.ADDR4,[1000]B.LDR3,(R4)C.SUBR4,R3 D.SD0(R3),R4

2.在其它部件性能保持不变的情况下,对CPU性能的不断改进并没有获得期望的结果,这主要是受到了A的影响。

A.Amdahl定律B.流水线C.指令集D.体系结构

3、对cache性能进行分析时,我们发现A不受cache容量的影响。

A.强制性失效B.容量失效C.冲突失效D.3C失效

4、若某CPU只有一个存储器,采用DLX流水线并执行如下的程序段,①SD(R1),R2②LDR3,(R1)#4③ADD0(R1),#8④SUBR3,R1;

则该程序段中指令①和指令④的关系属于A。

A数据相关B名相关C控制相关D结构相关

5、在下列存储器中访问速度最慢的是D。

ACacheBSDRAMCDRAMDFlash

6、最近计算机上采用的SSD(固态硬盘)实质上是A存储器。

A.FlashB.磁盘C.磁带D.光盘

7、计算机使用总线结构的主要优点是便于实现积木化,同时C。

A.减少了通信传输量B.提高了通信传输的速度

C.减少了通信传输线的条数D.有利于芯片中布线

8、下面关于流水线的说法不正确的是D。

A流水线由若干个“段”或“级”组成B流水线有“通过时间”

C流水线的“各段时间”应尽量相等D流水线的”深度”越多越好

9、我们常说的32位处理器是指处理器的A是32位的。

A数据总线B控制总线C地址总线D所有的总线

10、科学计算中采用向量处理机的主要原因是A较少。

A数据相关 B控制相关C结构相关D非向量处理机

11、为了便于实现多级中断,保存现场信息最有效的方法是采用_B__.。

A.通用寄存器 B堆栈 C.存储器 D.外存

12、在下面描述的RISC指令系统基本概念中不正确的表述是A。

A.选取使用频率低的一些复杂指令,指令条数多。

B.指令长度固定

C.指令功能简单

D.指令运行速度快

13、在下述I/O控制方式中,主要由程序实现的是B。

A.I/O处理机方式B.中断方式C.DMA方式D.通道方式

14、以下属于降低Cache失效率的方法是B。

A.子块放置技术B.编译器优化C.采用两级CacheD.虚拟Cache

15、现有一个Web服务器,其它部分不变的情况下,若采用如下的增强方式:

采用40个CPU,想要达到30的加速比,则串行部分的比率最大是A。

A.0.11B.0.12C.0.10D.0.13

三、简述题(每题5分,共25分)

1、解释如下几个缩写:

RISC、ISA、MIMD、RAID、Cache。

RISC精简指令集计算机

ISA工业标准结构

MIMD多指令流多数据流

RAID廉价磁盘冗余阵列

Cache高速缓冲存储器

2、试说明名相关的两种类型。

反相关:

指令i先执行,指令j写的名是指令i读的名。

反相关指令之间的执行顺序是必须保证的,反相关就是先读后写相关。

输出相关:

指令j和指令i写相同的名。

输出相关指令的指令顺序是不允许颠倒的。

输出相关就是写后写相关。

3、试说明定向技术的思想。

定向技术的思想是:

在某条指令产生一个计算结果之前,其他指令并不真正需要该计算结果,如果将该计算结果产生的地方直接送到其他指令需要他的地方,那么就可以避免暂停。

4、试说明伪相联Cache的特点。

伪相联Cache既能获得多路组相联Cache的低失效率,又能保持直接映像Cache的命中速度。

采用这种方法时,在命中情况下,访问Cache的过程和直接映像Cache中的情况相同,而发生失效时,在访问下一级存储器之前会先检查Cache另一个位置,看是否匹配。

5、试说明分布式共享多处理机的优缺点。

分布式存储器结构的优点:

(1)如果大多数的访问是针对本结点的局部存储器,则可降低对存储器和互连网络的带宽要求;

(2)对局部存储器的访问延迟低。

主要缺点:

处理器之间的通信较为复杂,且各处理器之间访问延迟较大。

四、图表题(第一题6分,第二题9分,共15分)

1、(6分)下图是写操作流水化的硬件结构,试说明采用该技术的原因及其工作特点。

每个写操作过程分为两个阶段完成,第一阶段进行标识比较,并把标识和数据存入延迟写缓冲器中,第二阶段再进行写入,这两个阶段按流水方式工作。

这样,当前的写标识比较就可以和上一个写的数据写入并行起来,实现每个时钟周期完成一个写操作

2、(9分)下面是采用DLX浮点部件的Tomasulo算法执行过程中用到的状态表,试填写状态表中的相关空白。

假定:

浮点流水线的延迟如下:

加法2个时钟周期,乘法10个时钟周期,除法40个时钟周期。

给出SUBD将要写结果时状态表的信息。

只填写相关部分空格。

指令

指令状态表

IS

EX

WR

LDF6,34(R2)

√

LDF2,45(R3)

MULTDFO,F2,F4

SUBDF8,F6,F2

DIVDF10,F0,F6

ADDDF6,F8,F2

部件

名称

保留站

Busy

Op

Vj

Vk

Qj

Qk

A

Load1

no

Load2

Add1

yes

SUBD

Mem[45+Regs[R3]]

Mem[34+Regs[R2]]

Add2

ADDD

Add3

Mult1

MULTD

Regs[4]

Mult2

DIVD

结果寄存器状态表

F0

F2

F4

F6

F8

F10

……

F30

部件名称

Mult1

Add1

Mult2

五、计算题(第一题7分,第二题8分,共15分)

1.某RISC处理机各类指令使用频率和理想CPI(指令和数据访问Cache命中率为100%时的CPI)如下表所示。

而实际测得的指令访问Cache缺失率(missrate)为5%,数据访问的Cache缺失率为10%,Cache的缺失损失(misspenalty)为40个时钟周期。

1)该机器在无Cache缺失(理想情况)时的CPI是多少?

(3分)

2)该机器在无Cache缺失(理想情况)时的速度比有Cache缺失时快几倍?

(4分)

指令类型

ALU操作

Loads

Stores

Branches

使用频率

40%

20%

15%

25%

CPIideal

1

3

1)CPI=43%X1+21%X2+12%X2+24%X2=1.57

2)对指令讲,指令Cache的访问占全部访问的100%/(100%+21%+12%)=75%

对数据来讲,数据Cache的访问占全部访问的(21%+12%)/(100%+21%+12%)=25%

非理想平均访存时间=命中时间+失效率X失效开销

=1.57+(75%X5%+25%X10%)X40=1.57+2.5=4.07

则:

4.07/1.57=2.59=2.6大约快2.6倍

2.在一台单流水线处理机上执行下面的程序。

每条指令都要经过“取指令”、“译码”、“执行”和“写结果”4个流水段,每个流水段的执行时间都是10ns。

采用基本的DLX流水线,执行如下指令段:

1SUBR0,R0;

R0←0

2LDR1,#4;

R1←向量长度4

3LOOP:

LDR2,A(R1);

R2←A向量的一个元素

4MULR2,R1;

R2←(R2)×

(R1)

5ADDR0,R2;

R0←(R0)+(R2)

6 BNEZR1,LOOP;

R1←(R1)-1,若(R1)≠0转向LOOP

7SD(R3),R0;

保存结果

采用“预测分支失败技术”。

画出指令流水线的时空图(中间部分可以省略,图中可用指令序号表示),计算流水线的加速比。

(8分)

IF

ID

EX

WB

2

E