针织圆机设计毕业设计论文Word文件下载.docx

《针织圆机设计毕业设计论文Word文件下载.docx》由会员分享,可在线阅读,更多相关《针织圆机设计毕业设计论文Word文件下载.docx(15页珍藏版)》请在冰豆网上搜索。

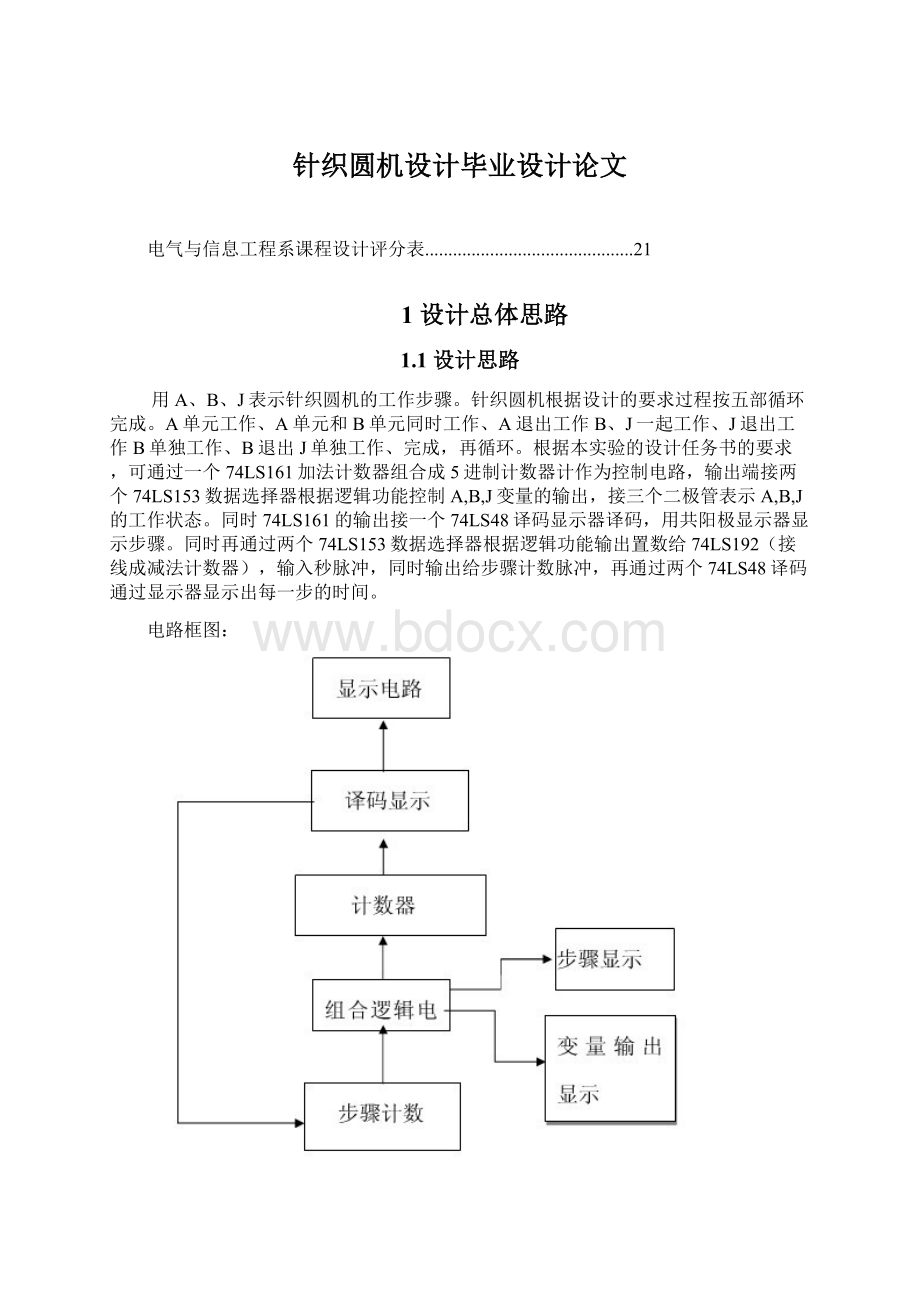

通过两片74LS153芯片数据选择输出控制A,B,J的工作状态。

2总电路图仿真图

3单元电路设计

3.1显示计数电路

下图为带译码驱动的4引脚数码管的共阳极接法。

用两个74LS192连咸亨十进制计数器,再加上两个7段显示器构成计数显示电路。

单元电路如下:

注:

输入端先用电平代替,这样可以验证局部电路的正确性,有利于分析和安装时查找错误的原因。

3.2计数电路

五进制步骤计数显示

4芯片功能

4.174LS192引脚图管脚及功能表

74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:

图5-4

74LS192的引脚排列及逻辑符号

(a)引脚排列

(b)逻辑符号

图中:

为置数端,

为加计数端,

为减计数端,

为非同步进位输出端,

为非同步借位输出端,P0、P1、P2、P3为计数器输入端,

为清除端,Q0、Q1、Q2、Q3为数据输出端。

其功能表如下:

输入

输出

MR

P3

P2

P1

P0

Q3

Q2

Q1

Q0

1

×

d

c

b

a

加计数

减计数

表5-2

74LS192的功能表

4.274LS153管脚及其功能

74LS153是常用的双4选1数据选择器,在各种数字电路和单片机系统的显示系统中经常用到

<

74ls153引脚图>

74LS153里面哟两个地址码公用的4选1数据选择器,通过输入不同的地址码A1,A0,可以控制输出Y选择4个输入数据D3~D0中的一个。

双4选1数据选择器74LS逻辑功能表

A1

A0

1Y

2Y

O

0

Ф

Ф

O

O

1

1

0

1D10

2D20

1D11

2D21

1D12

2D22

1D13

2D23

74ls153逻辑图>

4.374LS161管脚功能

74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:

74ls161引脚图>

管脚图介绍:

时钟CP和四个数据输入端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC.(TC=Q0·

Q1·

Q2·

Q3·

CET)

输入

输出

CR

CP

LD

EP

ET

D3

D2

D1

D0

Q3

Q2

Q1

Q0

Ф

1

↑

d

c

b

a

状态码加1

74LS161功能表>

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO=Q0·

CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

5调试、安装步骤

5.1软件仿真

根据设计的总体思路依次在仿真软件上完成各个模块的电路图。

电路图完成后,先单独仿真各电路模块的功能,然后将各个单元电路连成总电路图进行仿真并修改,直至达到了预期的目标功能。

如果一张标准图纸内无法容下整个电路可通过创建子电路的方法作图。

5.2实际电路的安装及调试步骤

实际电路的安装可在专用的实验箱上也可在数字实验室台上进行。

在数字实验台上的接线较简单,其步骤为:

根据总电路图规划好芯片的位置,然后简单测试芯片和导线的好坏;

接着根据模块电路图连接线路,每个模块单独检验是否符合仿真结果,接线之前要准备好各个芯片的引脚图和模块电路纸质图。

模块逐一测试符合后,连接成总电路图,进一步测试直至达到预期实验效果。

在试验箱上的接线步骤为时除了上述步骤还应注意设置VCC总线、GND总线和时钟总线;

测试时可以将面包板上需要外接的线引到板边缘未使用的列线插孔,外接时从列线其他孔接出。

5.3故障分析与电路改进

5.3.1接线时发生的故障及分析

在用实验台接完总电路后通电后,显示器均无反应。

分析发生发现电源接触不良,检测电源。

经检查发现+5V电源无输出,切换电源,接通后显示器有反应,上述故障消失。

在数电实验台上最后接逻辑控制电路模块时,步骤显示器显示不正常。

经检查是步骤显示器与芯片74LS61输出端之间导线短路,更换导线后,步骤显示器显示正常工作。

实验时发现第五步不能置3,经检查一74LS153芯片输入正常,输出不正常,故推测是试验台内部线路有故障,芯片移动位置后,上述故障消失。

最后,总电路图终于达到预期实验效果。

5.3.2电路的扩展设计

要求实现增加某些步骤循环。

上图实现完成下列工作流程:

A工作→A和B同时工作→A和B同时工作→B工作A退出J工作

↓完成←B退出J工作←J退出B工作←J退出B工作

时间要求:

A和B单独工作的时间均为20秒,两者同时工作时间为5秒,J工作时间为3秒.

6总结与心得

时间总是在不经意间飞逝,两周的课程设计伴随着这份报告的结束而结束。

在设计过程中我所感受到的,所学到的应该说是可以受用终生。

开始接到老师任务书时,我无从下手,但是通过对课题内容的了解和查找资料以及与同学的交流讲解,逐渐形成了总体电路设计和分电路设计的思路,并通过电路仿真,修改方案到最终确定设计方案。

经过自己设计出来的图纸看起来就觉得十分欣慰,但是在接线过程中也是破费周折的。

由于面包板太小,导线不方便实用,经过和同组的组员商量我们转到试验台上做。

这之前我们已经在面包板上接了两次了。

实验台上也不是很顺利,总有这样或者那样的问题出现。

反复检查设计图和接线,我们一个元件一个元件的检查,终于找出了问题所在。

最终完成了老师的任务,也完成了扩展训练。

通过这次课程设计我体会到:

一、不要惧怕困难,遇到苦难要迎难而上,你不解决它它会永远在那,如果面对它,它有可能只是纸老虎;

二、做事一定要严谨细心,细节决定成败;

三、通过课程设计我感觉到了知识的实用性,使我对今后的学习有了新的认识;

四、从电路图的设计我认识到思路的重要性;

五、要注重课本知识的灵活运用;

六、要善于与人沟通,注重培养团队精神。

总之这次课程设计是十分必要的,知识与实际的结合,提高了实际动手能力和专业技能。

最后感谢老师的精心指导和培养,祝老师身体健康工作顺利。

参考文献

1.《电子线路设计、实验、测试》(第二版)

华中理工大学出版社-------谢自美主编

2.《新型集成电路的应用》---------电子技术基础课程设计

华中理工大学出版社梁宗善主编

3.《电子技术基础实验》

高等教育出版社-------------陈大钦主编

4.《电子技术课程设计指导》

高教出版社-------------------彭介华主编

5.《电子技术基础实验与仿真》

中南大学出版社.2008-----------郭照南、孙胜麟主编

6.《数字电子技术基础》(第五版)

高等教育出版社.2006--------阎石主编

附件

1.逻辑式

A=X'

Y'

Z+X'

YX'

B=X'

YZ'

+X'

YZ+XY'

Z'

D0=X'

Z

D1=XY'

D2=X'

YZ

D5=X'

Z+XY'

D3=D4=D6=0

2.电路接线图

(图中为第四步B单独工作20秒)

(图中显示为第一步A单独工作20秒)

附录元件清单

元件类型

数量/个

74LS161

74LS04

74LS32

74LS192

2

74LS153

4

74LS00

4引脚数码管

电气与信息工程系课程设计评分表

项目

评价

优

良

中

及格

差

设计方案的合理性与创造性(10%)

硬件设计或软件编程完成情况(10%)