EDA程序改错题Word文档下载推荐.docx

《EDA程序改错题Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《EDA程序改错题Word文档下载推荐.docx(11页珍藏版)》请在冰豆网上搜索。

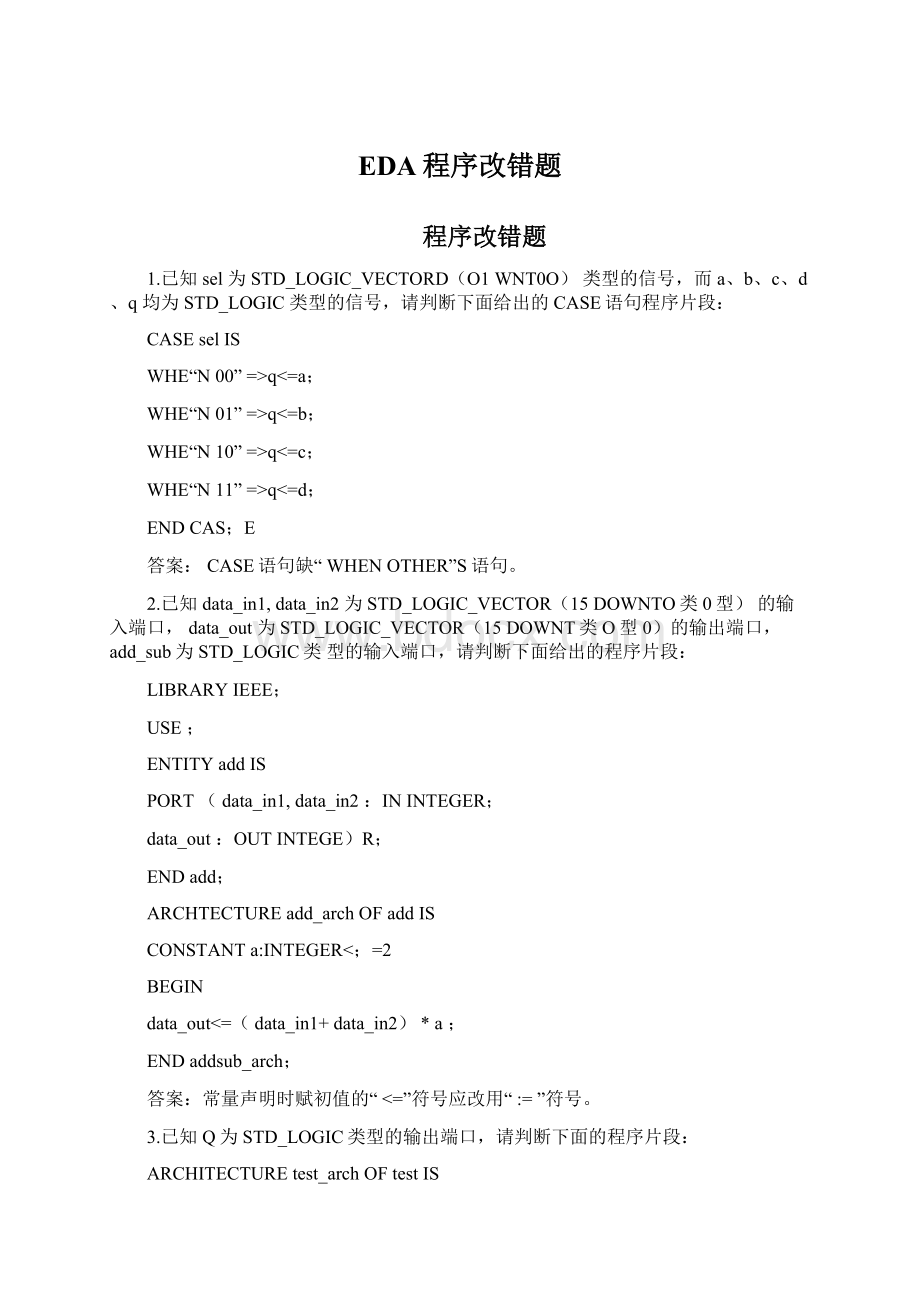

=2

BEGIN

data_out<

=(data_in1+data_in2)*a;

ENDaddsub_arch;

常量声明时赋初值的“<

=”符号应改用“:

=”符号。

3.已知Q为STD_LOGIC类型的输出端口,请判断下面的程序片段:

ARCHITECTUREtest_archOFtestIS

SIGNALB:

STD_LOGI;

C

Q<

=B;

ENDtest_arch

信号SIGNAL的声明语句应该放在BEGIN语句之前。

4.已知A和Q均为BIT类型的信号,请判断下面的程序片段:

ARCHITECTUREarchtestOFtestIS

CASEAIS

WHEN‘0'

=>

=‘1'

WHEN‘1'

=‘0'

ENDarchtest;

CASE语句应该存在于进程PROCES内S。

三.判断改错题(3分×

6题)(评分标准:

给出正确答案1分/题;

答案基本正确分/题。

)

1.已知A和Q均为BIT类型的信号,请判断下面的程序片断:

ARCHITECTUREtestOFtestIS

WHEN'

0'

=>

Q<

='

1'

;

ENDCASE;

ENDtest;

【参考答案】:

CASE语句应该存在于进程PROCESS内。

2.已知start为STD_LOGIC类型的信号,sum是INTEGER类型的信号,请判断下面的程序片断:

PROCESS(start)

FORiIN1TO9LOOP

sum:

=sum+i;

ENDLOOP;

ENDPROCES;

S

sum是信号,其赋值符号应该由“:

=”改为“<

=”。

3.已知Q为STD_LOGIC类型的输出端口,请判断下面的程序片断:

SIGNALB:

STD_LOGIC;

Q<

=B;

信号SIGNAL的申明语句应该放在BEGIN语句之前。

4.已知A和B均为STD_LOGIC类型的信号,请判断下面的语句:

A<

B<

x'

不定态符号应该由小写的‘x'

改为大写的‘X'

。

5.已知A为INTEGER类型的信号,B为STD_LOGIC类型的信号,请判断下面的程序片断:

=A;

A和B的数据类型不一致,不能相互赋值。

6.已知sel是STD_LOGIC_VECTORD(O1WNT0O)类型信号,而a、b、c、d、q均为STD_LOGIC类型信号,请判断下面给出的CASE语句:

WHEN“00”=>

q<

=a;

WHEN“01”=>

=b;

WHEN“10”=>

=c;

WHEN“11”=>

=d;

CASE语句缺“WHENOTHE”RS语句。

四、判断下面程序中是否有错误,若有错误请改正;

1、SIGNALA,EN:

STD_LOGIC;

PROCESS(A,EN)

VARIABLEB:

IFEN=‘1'

THEN

B<

=A;

END;

ENDPROCESS;

2、RCHITECTUREONEOFSAMPLEIS

VARIABLEA,B,C:

INTEGER;

C<

=A+B;

五、判断下列程序是否有错误,如有则指出错误所在(10分)程序:

LIBRARYIEEE;

USEzyt12IS

PORT(R,EN,CP:

INbit;

Q:

BUFFERSTD_LOGIC_VECTOR(0DOWNTO3);

CO:

OUTSTD_LOGIC);

ENDzyt;

ARCHITECTUREc10OFzyt12

CO<

='

WHEN(EN='

ANDQ="

1011"

)ELSE;

'

;

PROCESS(R,CP)

IFR='

="

0000"

ELSIF(CP'

EVENTANDCP<

)THEN

IFEN='

=Q;

ELSIFQ="

THENQ<

=‘0000'

;

ELSE

=Q+1;

ENDIF;

ENDone;

仔细阅读下列程序,回答问题

--1

USE--2

ENTITYLED7SEGIS--3

PORT(A:

INSTD_LOGIC_VECTOR(3DOWNTO0);

--4

CLK:

INSTD_LOGIC;

--5

LED7S:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

--6

ENDLED7SEG;

--7

ARCHITECTUREoneOFLED7SEGIS--8

SIGNALTMP:

STD_LOGIC;

--9

BEGIN--10

SYNC:

PROCESS(CLK,A)--11

BEGIN--12

IFCLK'

EVENTANDCLK='

THEN--13

TMP<

=A;

--14

--15

--16

OUTLED:

PROCESS(TMP)--17

BEGIN--18

CASETMPIS--19

WHEN"

LED7S<

=

"

0111111"

--20

0001"

0000110"

--21

0010"

1011011"

--22

0011"

1001111"

--23

0100"

1100110"

--24

0101"

1101101"

--25

0110"

1111101"

--26

0111"

0000111"

--27

1000"

1111111"

--28

1001"

1101111"

--29

ENDCASE;

--30

--31

--32

1.在程序中存在两处错误,试指出,并说明理由:

第14行TMP附值错误第29与30行之间,缺少WHENOTHER语S句2.修改相应行的程序:

错误1行号:

9程序改为:

TMP:

STD_LOGIC_VECTOR(3DOWNTO0);

错误2行号:

29程序改为:

该语句后添加WHENOTHERS=>

="

0000000

1、LIBRARYIEEE;

USE

ENTITYCNT4BIS

PORT(CLK,RST,ENA:

OUTY:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT:

OUTSTD_LOGIC);

ENDCNT4B;

ARCHITECTUREbehavOFCNT4BIS

SIGNALCQI:

PROCESS(CLK,RST,ENA)

IFRST='

THENCQI<

0000'

ELSIFCLK'

IFENA="

1"

=CQI+1;

ELSECQI<

OUTY<

=CQI;

COUT<

=CQI(0)ANDCQI

(1)ANDCQI

(2)ANDCQI(3);

ENDbehav;

2、LIBRARYIEEE;

USECLK_6DIS

PORT(CLK,RST:

CLK_OUT:

ENDCLK_6D;

ARCHITECTUREONEOFCLK_6DIS

VARIABLETEMP:

STD_LOGICS;

IGNAL

PROCESS(CLK)

VARIABLECNT6D:

INTEGERRANGE0TO3;

CONSTANTSIGN:

INTEGER:

=2;

'

IF(RST=“1”)THENTEMP<

=“0”

EVENTANDCLK='

THEN(CLK'

IF(CNT6D=SIGN)THEN

CNT6D:

=0;

TEMP<

=NOTTEMP;

ELSECNT6D:

=CNT6D+1;

CLK_OUT<

=TEMP;

ENDONE;

3、libraryieee;

useencoder