模可变16位加法计数器教材文档格式.docx

《模可变16位加法计数器教材文档格式.docx》由会员分享,可在线阅读,更多相关《模可变16位加法计数器教材文档格式.docx(23页珍藏版)》请在冰豆网上搜索。

可用仪器:

PC机(QuartusII软件)硬件:

EDA-IV型实验箱。

要求完成的主要任务:

(1)设计任务

设计可变16位加法计数器,可通过3个选择位M2、M1、M0实现最多8种不同模式的计数方式,例如可构成5、10、16、46、100、128、200、256进制,共8种计数模式。

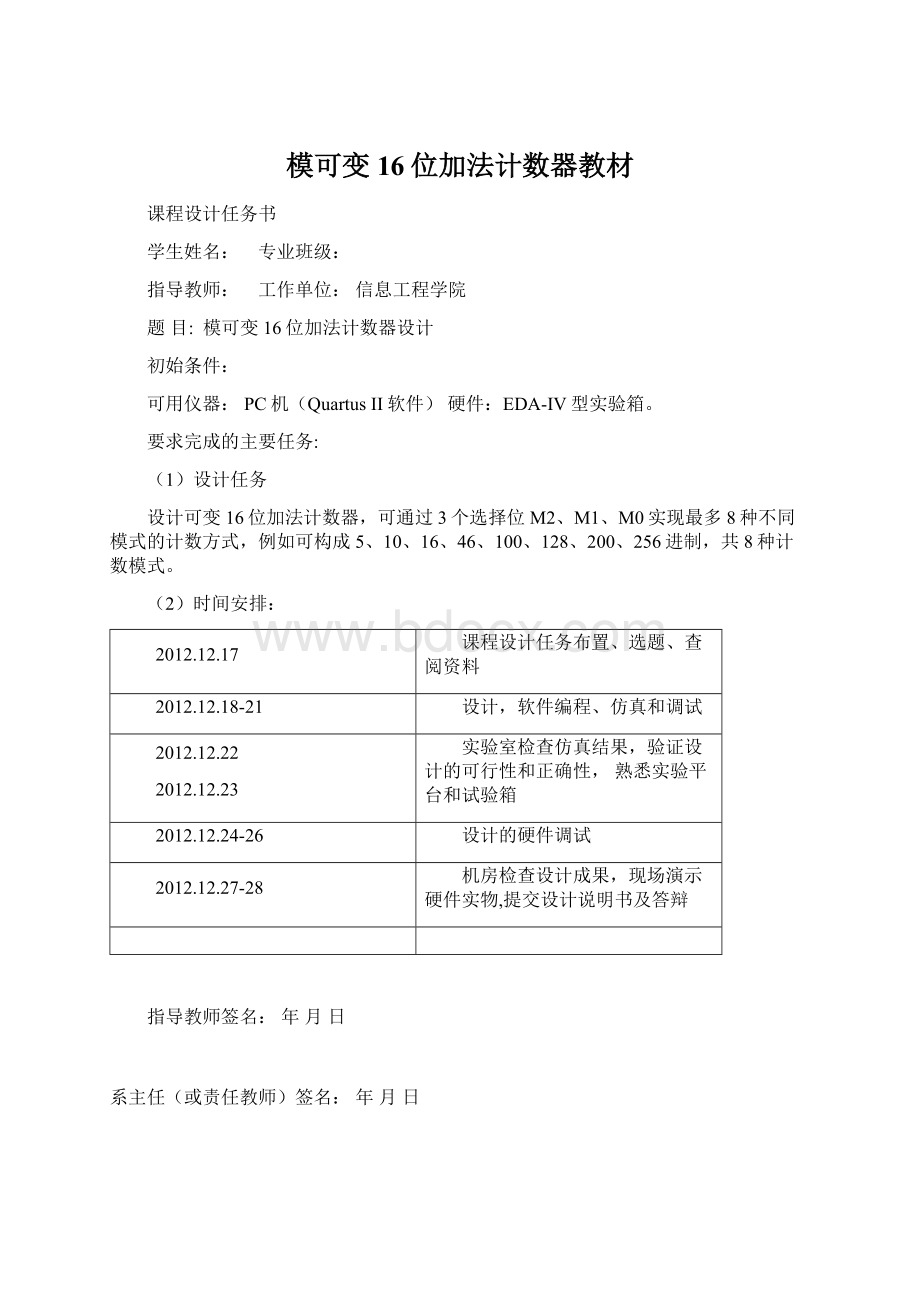

(2)时间安排:

2012.12.17

课程设计任务布置、选题、查阅资料

2012.12.18-21

设计,软件编程、仿真和调试

2012.12.22

2012.12.23

实验室检查仿真结果,验证设计的可行性和正确性,熟悉实验平台和试验箱

2012.12.24-26

设计的硬件调试

2012.12.27-28

机房检查设计成果,现场演示硬件实物,提交设计说明书及答辩

指导教师签名:

年月日

系主任(或责任教师)签名:

摘要

计数器的种类按照计数器中的触发器是否同时翻转分类,可将计数器分为同步计数器和异步计数器两种,如果按照计数过程中数字增减分类,又可将计数器分为加法计数器、减法计数器和可逆计数器,随时钟信号不断增加的为加法计数器,不断减少的为减法计数器,可增可减的叫做可逆计数器。

计数器不仅能用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲和脉冲序列以及进行数字运算等。

但是并无法显示计算结果,一般都是要通过外接LCD或LED屏才能显示。

本次课程设计重点研究了可变模计数器的设计与实现,在对现有的可变模计数器的研究基础上,在Quartus开发环境中,用VHDL语言设计一种功能更加强大的可变模计数器,它具有清零、置数、使能控制、可逆计数和可变模等功能,并且对传统的可变模计数器的计数失控问题进行研究,最终设计出一种没有计数失控缺陷的可变模计数器,并通过波形仿真和EPF10K20TI144-4系列实验箱,验证了其各项设计功能。

结果表明该设计正确.功能完整。

运行稳定。

关键词:

模可变,计数器,VHDL语言

Abstract

Thetypeofthecounterflip-flopinthecounteratthesametimefliptheclassification,canbecountertobedividedintosynchronouscountersandasynchronouscounters,digitalchangesinclassificationinaccordancewiththecountingprocess,butalsothecounterisdividedintoaddingcounter,downcounterandreversiblecounter,atanytimetheclocksignalincreasingfortheadditioncounterdwindlingdowncounter,growthcanbereducediscalledthereversiblecounter,inadditiontoavarietyofclassificationdoesnotenumerate,ThecurriculumdesignwilltakeadvantageofmanyICsoftwareQuartusIIsoftware,usingtheVHDLlanguagetodesigna3-bitselecttheM2,theM1,M0upto8differentmodecountThecounterisnotonlyusedtocountclockpulses,canalsobeusedtodivide,fromtimetotime,thebeatpulseandthepulsesequenceandnumbercrunching.CannotdisplaythecalculationresultsaregenerallythroughanexternalLCDorLEDscreentodisplay.

Focusonthecountervariablemodeofdesignandimplementation.IntheenvironmentofQuartusbasedonresearchoftheexistingmodule—alterablecounter,amodule—alterablecounterwithmorefunctions,suchasclear,set,enablecontrol,reversiblecount,module—alterablecountandsoon,whichisdesignedwithVHDL.Byresearchingtheproblemoflosingcontrolexistedintraditionalmodule—alterablecounter.Amodule—alterablecounterwithnofaultdesigned.AndthroughthewaveformsimulationandEPF10K20TI144-4seriesexperimentbox,allofthefunctionsareverified.Theresuitindicatesthatthecounterisdesignedcorrectly,andhasintegralfunctionsandstableoperation.

Keywords:

Dievariable;

Counter;

VHDLlanguage

1计数器的工作原理

计数器是数字系统中使用较多的一种时序逻辑器件。

计数器的基本功能是统计时钟脉冲的个数,即对脉冲实现计数操作。

其工作原理可概述为:

当输入时钟脉冲的一个上升沿(也可以是下降沿)来临时,二进制数据的低一位加1(或减1),并向高位进1(或借1)。

在没有外部约束条件时,计数器可进行与其二进制位数对应的数值的相应进制的自循环计数,如位数为3的计数器可进行8进制的自循环加法或减法计数。

可根据需要来设置计数器的位数,并通过外部约束条件来人为设定计数器的计数模数,来得到计数进制符合需要的N进制计数器。

所谓N进制计数器,是指一个计数器的计数过程,在经历时钟脉冲信号的个为N之后,二进制数据又回到初始状态的计数器。

时钟

Q0

Q1

……

Qn-1

Qn

0..00

1

2

3

…..

2n-1

2n

1..11

2n+1

图2.1计数器的状态表

图2.2计数器的状态图

2设计原理

本文所设计的为模可变的16位加法计数器,可通过3个选择位M2、M1、M0实现最多8种不同模式的计数方式,例如可构成5、10、16、46、100、128、200、256进制,共8种计数模式。

并编程设计相关配套外围电路,通过把程序下载到实验箱来实现硬件的调试。

2.1整体设计原理

根据层次化设计理念,可分解成分频模块、计数模块、显示模块来进行模块化设计,再把各模块综合得到所设计的电子线路系统。

因为现实时需要用七段数码管来显示所设计的电子系统功能,所以需要设计显示模块。

又因为实验箱上的时钟脉冲频率为20MHZ,而实际需要的频率为2HZ和2000HZ,所以实验箱上的时钟脉冲频率不符合本次设计的使用要求,还需要设计时钟分频模块对时钟进行分频以得到频率为2HZ和2000HZ的时钟脉冲信号。

分频器2000HZ

图3.1整体设计原理框图

原始时钟经过分频模块后得到符合要求的时钟脉冲信号作为计数模块的时钟输入,通过3位拨码开关来控制模数选择模块的模数输出,该模数输出作为计数模块的模数选择信号输入,计数模块的16为数据输出作为显示模块的16位数据输入,显示模块的7位输出做为七段数码管的输入。

2.2单元模块的设计

2.2.1计数模块的设计

计数器是最常用的寄存器逻辑电路,从未处理器的地址发生器到频率计都需要用到计数器。

一般计数器分为两类:

加法计数器和减法计数器。

加法计数器每来一个脉冲计数值加1;

减法计数器每来一个脉冲计数值减1。

本次课程设计需要做的是加法计数器。

计数模块中设计采用了常用的if语句结构,即“if条件句then顺序语句elsif条件句then顺序语句else顺序语句endif”结构,实现模值小于257的可变模计数。

课设所要求的8种不同模式的计数方法,以简单的5进制为例,当拨码开关为000时,输出选中5进制,循环依次显示0,1,2,3,4。

计数源程序中定义了由三个拨码开关控制的八种不同模式的计数方法,000对应5进制,001对应10进制,010对应16进制,011对应46进制,100对应100进制,101对应128进制,110对应200进制,111对应256进制。

程序中还使用withselect语句可使程序设计变得简单,null为空操作语句,程序中使用nullwhenothers语句是为了避免当拨码开关输入出现错误输入时造成程序功能错误。

源程序中定义矢量信号变量是为了实现变量自赋值,因为一般的输出变量不能实现自赋值,而计数过程中又需要变量自赋值来实现计数。

因为信号变量具有暂存功能,所以可实现自赋值。

因此需要设置信号变量,再把信号变量的置赋予输出变量,以使程序正确实现功能。

2.2.2显示模块的设计

显示模块的设计可以由点阵或数码管显示来实现,虽然点阵实现时所设计的程序比较简单,但是我觉得用点阵实现不同模式的结果不易直观的看出,而且本次课程设计最大实现256进制,所以需要利用三个数码管,因此我选择用三个七段数码管来实现。

扫描显示电路需要设计位选程序,分频程序和七段数码管程序。

位选程序是由计数模块输出的两位来提供8421BCD码,经过译码电路后成为七段数码管的字形显示驱动信号。

扫描电路通过可调时钟输出片选地址,有片选地址和七段数码管决定7位中的哪一位亮和显示什么字形。

最终计数过程显示在数码管上,将数据的百、十、个位分开分别送三个数码管显示,用casewhen语句实现数字的BCD码与数码的联系。

数码管的位选利用了3/8译码器及加快时钟频率带来的视觉暂留。

2.2.3分频模块的设计

由于试验箱上提供的时钟频率为20MHZ,而实际需要的是2HZ和2000HZ,所以用两个计数器来实现分频。

利用计数器的进位输出作为分频后的时钟脉冲信号输出,计数器的计数进制就是分频器的分频数,即N进制的计数器就可以对原始时钟进行N分频。

分频模块的输出作为计数模块和显示模块位选功能的输入。

2.2.4顶层例化模块

元件例化是多层次的,在一个设计实体中被调用安插的元件本身也可以使一个低层次的当前设计实体,因而可以调