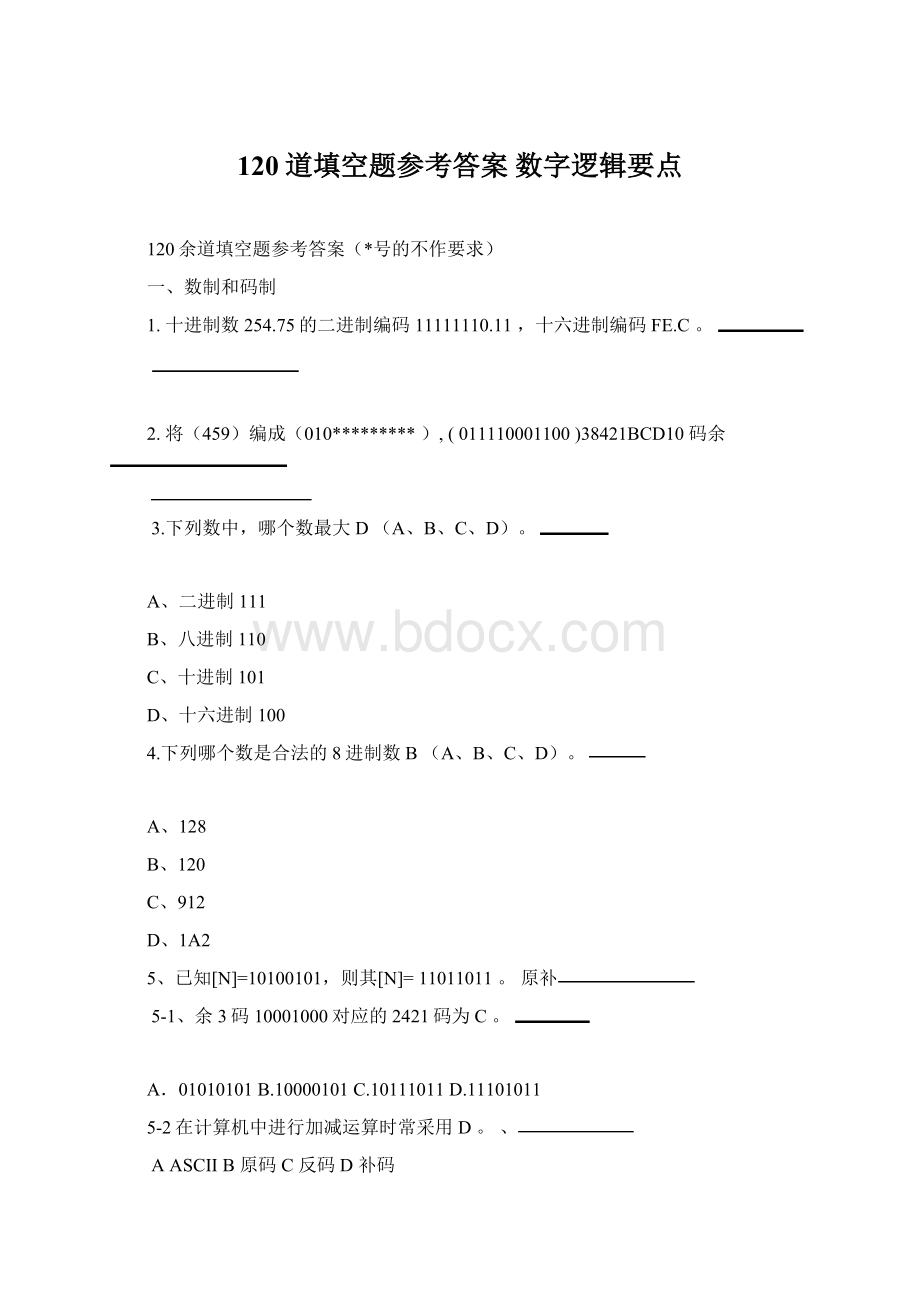

120道填空题参考答案 数字逻辑要点Word文档下载推荐.docx

《120道填空题参考答案 数字逻辑要点Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《120道填空题参考答案 数字逻辑要点Word文档下载推荐.docx(23页珍藏版)》请在冰豆网上搜索。

5-2在计算机中进行加减运算时常采用D。

、

AASCIIB原码C反码D补码

5-3、二进制小数-0.0110的补码表示为1.1010。

5-4、0的原码有2形式,反码有2形式,补码有1形式。

二、门电路

6、CMOS电路不用的输入端不能(能、不能)悬空。

7、CMOS“与非”门用的多余输入端的处理方法有:

A。

A、接逻辑“1”B、接逻辑“0”C、悬空

8、CMOS门电路的功耗比TTL门电路的功耗小(大、小)。

9、TTL门电路的速度比CMOS门电路速度高(高、低)。

10、与普通门电路不同,OC门在工作时需要外接上拉电阻和电源。

1

11、OC门的输出端相连可以实现线与。

*12、有两个TTL与非门,它们的关门电平分别为V=1.1V,V=0.9V;

开门OFFBoffA电平分别为V=1.3V,V=1.7V。

它们输出的高低电平均相同,A(A、onBonA

B)门的抗干扰能力强。

13、一片与非门芯片具有三个三输入端与非门,该芯片引脚数至少要14。

(14、16、18、20)。

14、三态门除了具有高电平和低电平两种状态外,还有第三种状态叫高阻状

态。

15、三极管作为开关器件“非门”时,不能工作在放大状态。

16、将2输入端与非门当作非门使用时,则另一输入端接1(0,1);

将2

输入端或非门当作非门使用时,则另一输入端接0(0,1)。

17、74LS00是TTL电路(TTL电路、CMOS电路)。

74HC00是CMOS电

路(TTL电路、CMOS电路)。

18、TTL门电路主要外部特性参数有标称电平、开门电平、关门电平延时、

功耗、扇入系数、噪声容限等等。

*19、NMOS门电路如图19所示,输入变量为A、B,输出函数L=。

图19

20、一片芯片具有四个两输入端或非门,该芯片引脚数至少14(14、16、

18、20)。

21、74LS00和74HC00芯片,74LS00芯片速度更快。

2

22

图L=低电平)(H=高电平、22、上图中,Y1=L,Y2=L。

V,最大输入低max=0.1V*23、某集成电路芯片,查手册知其最大输出低电平OLVVV,,最小输入高电平max=1.5V,最小输出高电平max=3.5Vmax=4.9V电平IHILOHV则其低电平噪声容限。

=BNL

A2.0VB1.4VC1.6VD1.2V

。

23-1、下列真值表完成的逻辑函数为C

F=A+B

BD、、F=A-BC、F=A⊕A、F=ABB

、1⊕。

0=

23-2⊕X0⊕1⊕1⊕

B、下列逻辑函数中,与23-3相等的是AF?

⊙0?

1A?

F?

AA?

?

A1F1)D(A)(()B()C2143

三、逻辑函数化简和冒险

=0,m=0=1A、三变量、B、C,最小项m,m24210

X是一位二进制数)1=x1⊕0⊕。

(⊕25、x0⊕

有(有,无)险象。

26、由函数构成的逻辑电路

AC?

AEF?

CDE27、逻辑函数无(有、无)构成的逻辑电路,逻辑冒险。

3

28、说法“一个没有冒险现象的逻辑表达式是最简逻辑表达式”错误。

(正确、

错误)

29、说法“用卡诺图简化逻辑函数时,从没有多种入圈方式的1开始画卡诺圈,这样将不会产生多余圈”正确。

(正确、错误)

30、说法“卡诺圈中1的个数应该为2的整数倍,如2、4、6…个1”错误。

(正确、错误)

31、逻辑函数的表达方法有表达式、电路图、真值表等。

32、竞争冒险是由于门电路延时产生的。

四、组合逻辑电路

33、常用MSI组合逻辑电路有编码器、译码器、数据选择器

等。

、全加器数值比较器

34、说法“组合逻辑电路的输出只和即时输入有关,与过去的输入和输出无关”

正确。

35、与门、或门和非门是组合逻辑电路的基本单元。

36、奇偶校验器只能检测奇次(奇次、偶次)数据传输错误。

37、数据选择器的功能是C(A、B、C、D)。

A、从两路输入信号中选一路输出。

B、把一路信号分时从几路输出。

C、从多路输入信号中选一路输出。

D、根据控制信号,决定是输出输入信号,还是输出处于高阻状态。

38、数据比较器如图所示,如果引脚234分别接“100”;

9、11、14、1脚接“1001”;

10、12、13、15接“1001”。

那么567脚分别输出001。

39、超前进位加法器与串行进位加法器相比,速度更快。

4

,则、若要某共阴极数码管显示数字“3”63。

显示代码abcdefg为

)(0000000~1111111

,则3”64、若要某共阳极数码管显示数字“。

1111001显示代码abcdefg为

)(0000000~1111111

五、时序电路

是时序逻辑电路的基本单元。

40、触发器

次,1CP的一个变化周期中,它的状态改变了41、就总体而言,主从触发器在

现象。

空翻克服了

D)克服了空翻现象。

B、C、C(A、42、

JK触发器A、基本JK触发器)B、时钟JK触发器(即电平JK触发器C、主从RS触发器D、时钟性能更好。

、与主从触发器相比,边沿触发器抗干扰43

、钟控触发器、44、触发器按结构可分为基本触发器

等。

、边沿触发器主从触发器

触发器、DJK触发器、触发器、45、触发器按功能可分为RS

触发器等。

Tn+1n=1,

Q触发器的状态由Q=0转换到46、JKD)。

B、C、J和K端正确而又完整的控制状态是A(A、

0)或(X表示1X1D、X0、A、1XB、0XC个触发器。

447、某同步时序电路有9个状态,该电路需要

个触发器。

448、要设计一个14进制加法计数器,该电路至少需要

状态表状态图、、49、时序电路的逻辑功能可以用特征方程、驱动方程、

等方式描述。

时序图

寄存器计数器50、请列举两种常用集成时序逻辑部件、

5

51、两片十进制计数器级联后,最多可构成100进制计数器。

52、状态编码时,状态表中出现次数最多的次态应分配逻辑0(0、1)。

53、异步时序电路中,触发器状态的变化不是(是、不是)同时发生的。

54、下面哪种说法正确B(A、B、C)。

A、同样的输入,对于RS边沿触发器与RS主从触发器,输出状态相同。

B、同样的输入,对于RS边沿触发器与RS主从触发器,输出状态未必相同。

C、同样的输入,对于RS时钟触发器与RS主从触发器,输出状态相同。

55、图示电路是(同步时序电路,异步时序电路)异步时序电路。

、某同步时序电路,状态转移图如图所示,其功能56。

具有自启动功能的模5二进制加法同步计数器是

某自动饮料售卖机连续投入两个一元硬币时,给出一瓶饮料,给饮料控制信、57时序逻辑电路(组合逻辑电路、时序逻辑电路)产生。

号应该用

”键时,密码箱打开,密码箱1”键,再按一次“258、某密码箱当连续按两次“产生。

(组合逻辑电路、时序逻辑电路时序逻辑电路)开启控制信号应该用

、某同步时序电路,状态转移图如图所示,其功能59。

序列检测器是111

6

、

IIN/OUT

D)、B、C、60、时序逻辑电路设计步骤是:

A(A

题意画出状态转换图,列状态表,简化状态表,状态编码,画激励和输出依、A卡诺图,得到激励函数和输出函数表达式,依据激励函数和输出函数表达式画电路图。

题意画出状态转换图,列状态表,状态编码,简化状态表,画激励和输出依、B卡诺图,得到激励函数和输出函数表达式,依据激励函数和输出函数表达式画电路图。

、依题意画出状态转换图,进行状态编码,画电路图,得到激励函数和输出函C数表达式。

题意画出状态转换图,简化状态图,得到激励函数和输出函数表达式,进依D、行状态编码,画电路图。

n?

1nQQ?

的是BD。

61、下列电路中,实现逻辑功能

QCPCP

QK1

Q

)(B(A)

N1Q0D1Q

C1CP?

C1CP(D))C(

QQ

62、某移位寄存器的时钟脉冲频率为100KHZ,欲将存放在该寄存器中的数左移8位,完成该操作需要B时间。

7

A.10μSB.80μSC.100μSD.800ms

63、异步时序电路分为脉冲异步时序电路和电位异步时序电路。

六、存储器和可编程器件、用ROM实现的逻辑函数如上图右所示,写出逻辑函数(不用简化)。

64

。

,为不丢失信息电容存储信息的65、动态MOS存储单元(DRAM)是利用

电路。

DRAM工作时必须辅以刷新必须定期刷新,所以

,PROM、根据写入的方式不同,只读存储器66ROM分为MROM,

2。

PROMEPROM,E

10。

条数据线,该储存器的容量是2字节67、某存储器有10条地址线和8

、存储器的存储矩阵由与阵列和或阵列组成。

68

等种类。

、FPGA、PAL、GAL、可编程逻辑器件有69PLA

,输出可组态可编程,或阵列固定GAL70、与阵列

七、其他

,下面环形多谐振荡器的振、平均延迟时间为t*70、若传输门电路的个数为Npd。

为荡周期

多谐振