数字逻辑电路复习题--2Word文档下载推荐.doc

《数字逻辑电路复习题--2Word文档下载推荐.doc》由会员分享,可在线阅读,更多相关《数字逻辑电路复习题--2Word文档下载推荐.doc(10页珍藏版)》请在冰豆网上搜索。

二、逻辑代数

1、证明等式成立。

2、利用卡诺图化简逻辑函数F(A、B、C、D)=

3、将F(A,B,C)=转换成最大项之积的形式。

4、由函数组成的电路在哪些情况下会产生险象?

如何排除?

已知:

x(a,b,c,d)=∏M(0,2,3,4,5,7,9,10),y(a,b,c,d)=∑m(0,1,4,5,6,

8,10,12,13),

5、求F=x⊕y的最简或非表达式。

6、证明下列等式成立。

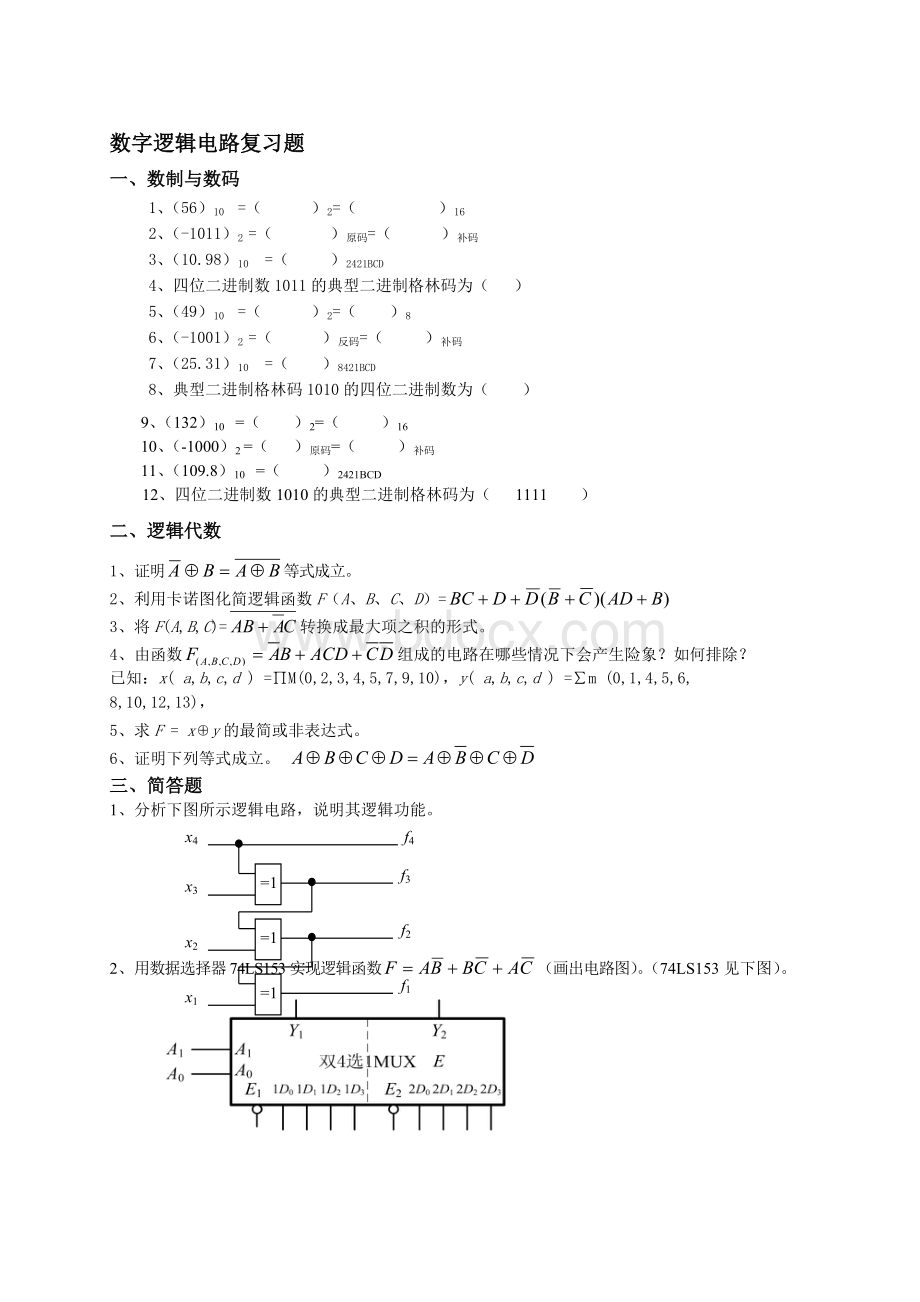

三、简答题

=1

x4

x3

x2

x1

f4

f3

f2

f1

1、分析下图所示逻辑电路,说明其逻辑功能。

2、用数据选择器74LS153实现逻辑函数(画出电路图)。

(74LS153见下图)。

3、用D触发器实现T触发器的逻辑功能,画出电路图(可以根据需要选用适当的逻辑门)。

4、用一片双四选一数据选择器74LS153,实现一位全加器的功能(74LS153见下图)。

四、组合电路设计

1、用与非门设计一个组合电路。

该电路输入为一位十进制的8421码,当其值大于5时输出F的值为1,小于5时输出F的值为0,写出完整设计过程。

2、用与非门设计一个组合电路。

该电路输入为一位十进制的8421码,当其值小于6时输出F的值为1,大于6时输出F的值为0,写出完整设计过程。

五、分析设计

1、设计一个模4计数器。

要求计数代码为典型格林码,用JK触发器实现,写出完整设计过程。

CP

&

D1

CP1

D2

CP2

D3

CP3

Q3

Q2

Q1

2、分析下图所示的时序逻辑电路,要求:

给出分析的必要步骤,描述电路的逻辑功能。

3、设计一个组合逻辑电路。

该电路有三个输入端,是一个二进制判断电路。

当并行输入的值£

3时,输出为0;

当并行输入的是³

6时输出为1。

要求用与非门完成电路设计并写出必要步骤。

4、用JK触发器设计一个模3计数器。

要求写出必要的设计步骤,并且状态顺序为:

11

00

01

5、用与非门设计一个组合逻辑电路。

该电路输入为一位十进制的8421码,当其值大于或等于8和小于等于3时输出F的值为1,否则F的值为0。

6、设计一个模4计数器。

7、用或非门设计一个组合逻辑电路。

该电路输入为一位十进制的8421码,当其值大于7和小于2时输出F的值为1,否则F的值为0。

8、设计一个模3计数器。

要求计数代码按照二进制数自然排列,用JK触发器实现,写出完整设计过程。

9、分析下图所示的时序逻辑电路,要求:

数字逻辑电路复习题答案

1、(56)10=(111000)2=(38)16

2、(-1011)2=(11011)原码=(10101)补码

3、(10.98)10=(00010000.11111110)2421BCD

4、四位二进制数1011的典型二进制格林码为(1110)

5、(49)10=(110001)2=(61)8

6、(-1001)2=(10110)反码=(10111)补码

7、(25.31)10=(00100101.00110001)8421BCD

8、典型二进制格林码1010的四位二进制数为(1100)

9、(132)10=(10000100)2=(84)16

10、(-1000)2=(11000)原码=(11000)补码

11、(109.8)10=(000100001111.1110)2421BCD

证明:

故:

左=右,得证。

2、化简逻辑函数F(A、B、C、D)=

解:

F=

=

3将F(A,B,C)=转换成最大项之积的形式。

解:

F=

=

=M6M7M3M1

=

4、答案(略)

5、已知:

x(a,b,c,d)=∏M(0,2,3,4,5,7,9,10),y(a,b,c,d)=∑m(0,1,4,5,6,8,10,12,13),

求F=x⊕y的最简或非表达式。

x(a,b,c,d)=∑m(1,6,8,11,12,13,14,15),

y(a,b,c,d)=∑m(0,4,5,6,8,10,12,13),

ab

cd

10

1

F(a,b,c,d)=ac+ac

三.简答题答案(略)

1、用与非门设计一个组合电路。

AB

CD

d

F=A+BC

=

1、列真值表:

2、化简,求逻辑函数:

ABCD

F

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

3、画电路图:

B

C

F=

=

A

五、

五.分析设计

1、设计一个模4计数器。

1)、列状态表:

Y2Y1

Y2n+1Y1n+1

Y2

Y1

Y1n+1

Y2n+1

2)、求激励函数: