基于FPGA的QPSK调制解调电路设计与实现.docx

《基于FPGA的QPSK调制解调电路设计与实现.docx》由会员分享,可在线阅读,更多相关《基于FPGA的QPSK调制解调电路设计与实现.docx(8页珍藏版)》请在冰豆网上搜索。

基于FPGA的QPSK调制解调电路设计与实现

基于FPGA的QPSK调制解调电路设计与实现

数字调制信号又称为键控信号,调制过程可用键控的方法由基带信号对载频信号的振幅、频率及相位进行调制,最基本的方法有3种:

正交幅度调制(QAM)、频移键控(FSK)、相移键控(PSK).根据所处理的基带信号的进制不同分为二进制和多进制调制(M进制).多进制数字调制与二进制相比,其频谱利用率更高.其中QPSK(即4PSK)是MPSK(多进制相移键控)中应用最广泛的一种调制方式。

1QPSK简介

QPSK信号有00、01、10、11四种状态。

所以,对输入的二进制序列,首先必须分组,每两位码元一组。

然后根据组合情况,用载波的四种相位表征它们。

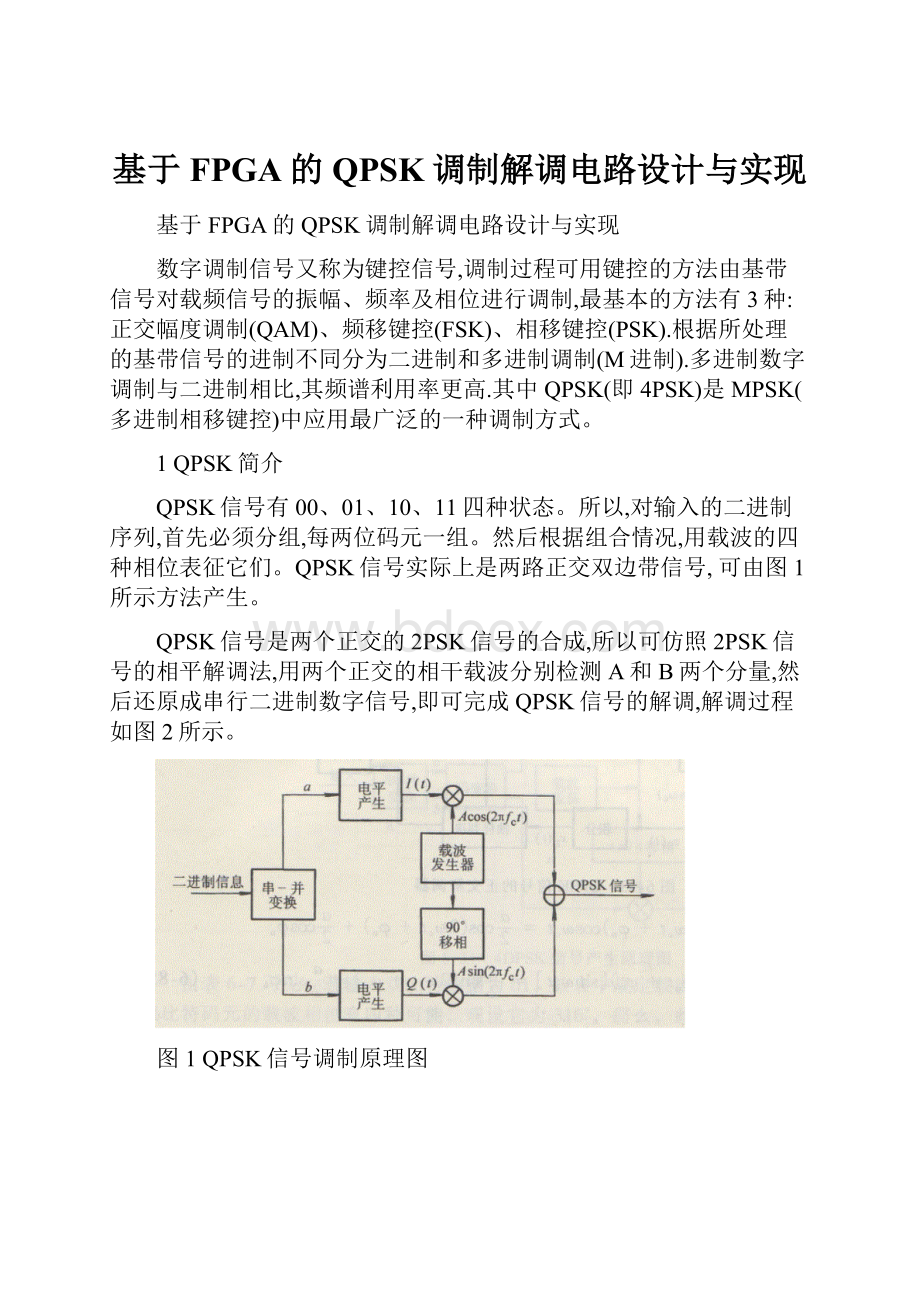

QPSK信号实际上是两路正交双边带信号,可由图1所示方法产生。

QPSK信号是两个正交的2PSK信号的合成,所以可仿照2PSK信号的相平解调法,用两个正交的相干载波分别检测A和B两个分量,然后还原成串行二进制数字信号,即可完成QPSK信号的解调,解调过程如图2所示。

图1QPSK信号调制原理图

图2QPSK信号解调原理图

2QPSK调制电路的FPGA实现及仿真

2.1基于FPGA的QPSK调制电路方框图

基带信号通过串/并转换器得到2位并行信号,,四选一开关根据该数据,选择载波对应的相位进行输出,即得到调制信号,调制框图如图3所示。

图3QPSK调制电路框图

系统顶层框图如下

图中输入信号clk为调制模块时钟,start为调制模块的使能信号,x为基带信号,y是qpsk调制信号的输出端,carrier【3..0】为4种不同相位的载波,其相位非别为0、90、180、270度,锁相环模块用来进行相位调节,用来模拟通信系统中发送时钟与接收时钟的不同步start1为解调模块的使能信号。

y2为解调信号的输出端。

2.2调制电路VHDL程序

程序说明

信号yy

载波相位

载波波形

载波符号

“00”

0°

f3

“01”

90°

f2

“10”

180°

f1

“11”

270°

f0

在quartusii下的仿真结果总体结果如下图所示

局部放大图如下

3QPSK解调电路的FPGA实现及仿真

3.1QPSK解调电路方框图

当调制为低电平时,译码器1根据记数器输出值,送入加法器相应的数据。

加法器把运算结果送到寄存器,译码器2根据寄存器数据通过译码,输出两位并行信号,该信号再通过并/串转换即可得到解调后的基带信号,调制框图如图4所示。

图4QPSK解调电路框图

3.2解调电路VHDL程序

libraryieee;

useieee.std_logic_arith.all;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityPL_MPSK2is

port(clk:

instd_logic;--系统时钟

start:

instd_logic;--同步信号

x:

instd_logic;--调制信号

y:

outstd_logic);--基带信号

endPL_MPSK2;

architecturebehavofPL_MPSK2is

signalq:

integerrange0to7;--计数器

signalxx:

std_logic_vector(2downto0);--加法器

signalyyy:

std_logic_vector(1downto0);--2位并行基代信号寄存器

signalyy:

std_logic_vector(2downto0);--寄存xx数据

begin

process(clk)

begin

ifclk'eventandclk='1'then

ifstart='0'thenq<=0;

elsifq=0then

q<=1;yy<=xx;y<=yyy(0);--把加法计数器的数据送入yy寄存器

ifx='0'then

xx<="001";--调制信号x为低电平时,送入加法器的数据“001”

else

xx<="000";

endif;

elsifq=2thenq<=3;

ifx='0'then

xx<=xx+"001";--调制信号x为低电平时,送入加法器的数据“001”

endif;

elsifq=4thenq<=5;y<=yyy

(1);

ifx='0'then

xx<=xx+"010";--调制信号x为低电平时,送入加法器的数据“010”

endif;

elsifq=6thenq<=7;

ifx='0'then

xx<=xx+"011";--调制信号x为低电平时,送入加法器的数据“011”

endif;

elseq<=q+1;

endif;

endif;

endprocess;

process(yy)--此进程根据yy寄存器里的数据进行译码

begin

ifclk='1'andclk'eventthen

ifyy="101"thenyyy<="00";--yy寄存器“101”对应基带码“00”

elsifyy="011"thenyyy<="01";--yy寄存器“011”对应基带码“01”

elsifyy="010"thenyyy<="10";--yy寄存器“010”对应基带码“10”

elsifyy="100"thenyyy<="11";--yy寄存器“100”对应基带码“11”

elseyyy<="00";

endif;

endif;

endprocess;

endbehav;使用FPGA实现QPSK调制解调电路,多进制数字调制技术与FPGA的结合使得通信系统的性能得到了迅速的提高。

系统联调的全局仿真图如下

局部放大图如下所示

从仿真图中可以看到基带信号x与解调出的信号y2一致,说明解调成功。

感谢下载!

欢迎您的下载,资料仅供参考