数字系统课程设计万年历时钟 VHDL语言.docx

《数字系统课程设计万年历时钟 VHDL语言.docx》由会员分享,可在线阅读,更多相关《数字系统课程设计万年历时钟 VHDL语言.docx(31页珍藏版)》请在冰豆网上搜索。

数字系统课程设计万年历时钟VHDL语言

万年历电子时钟

---------------数字系统课程设计

班级:

电子1412

学号:

14200106214、14200106204

姓名:

孙玮、甘家雨

指导老师:

刘传洋

时间:

6月14日——6月22日

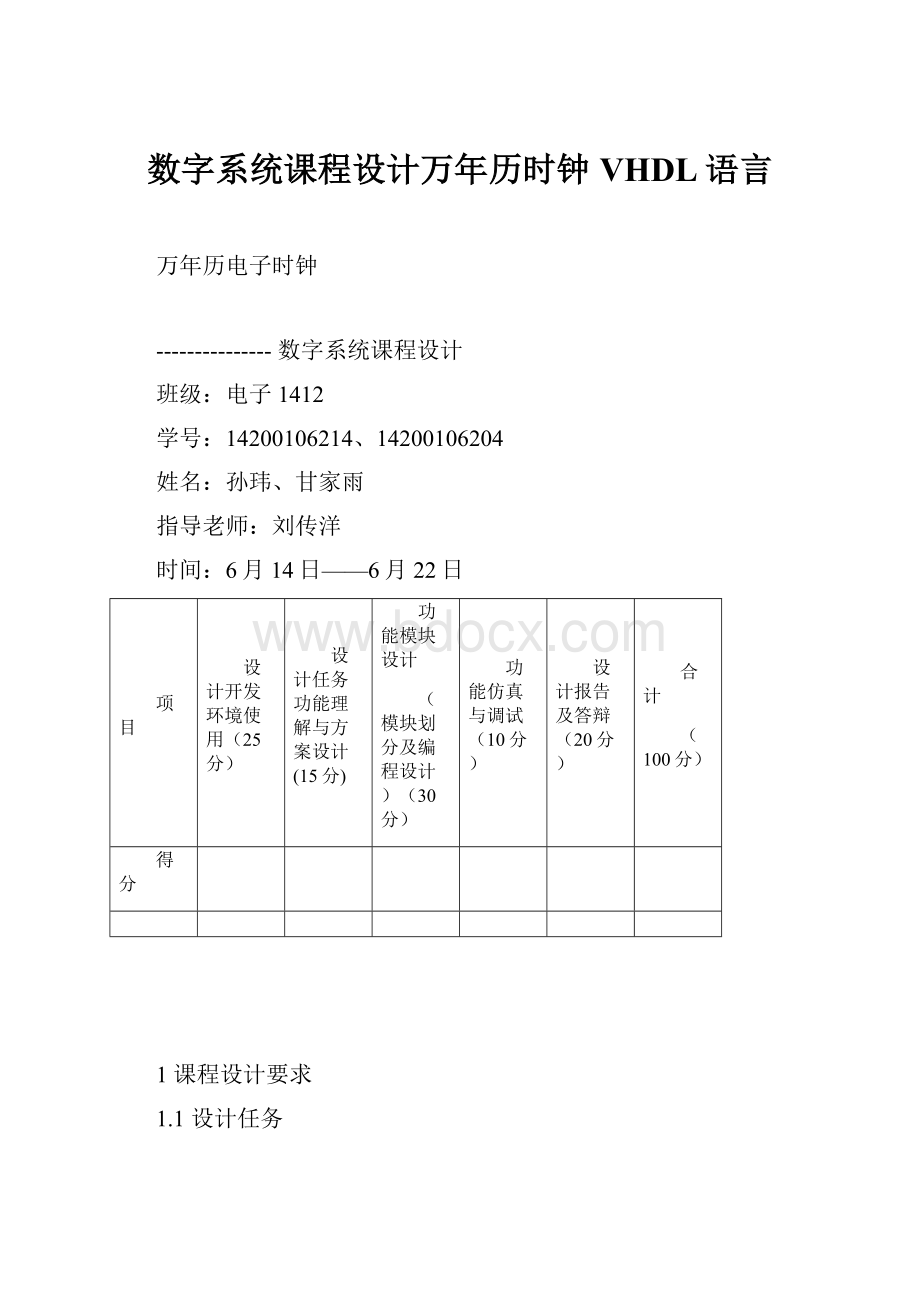

项目

设计开发环境使用(25分)

设计任务功能理解与方案设计(15分)

功能模块设计

(模块划分及编程设计)(30分)

功能仿真与调试(10分)

设计报告及答辩(20分)

合计

(100分)

得分

1课程设计要求

1.1设计任务

设计制作一个基于LCD1602显示,带有时间调整的万年历电子时钟。

1.2设计要求

1)采用硬件描述语言VHDL设计带有日期功能的数字电子时钟模块及LCD显示控制模块,并在Quartus-II环境下编译;

2)在Quartus-II环境下编辑仿真激励波形,并模拟;

3)在CPLD/FPGA实验板下载调试;

4)撰写设计报告,需要提供详细的设计方案分析、相关的参数计算过程、电路/系统组成、模块划分及其功能定义、程序设计、功能仿真及其结果分析、下载调试等内容。

1.3功能及性能指标要求

1)具有时钟的时、分、秒计数功能以及万年历的年、月、日功能;

2)年、月、日、时、分、秒数值采用字符型LCD1602显示;

3)具有对年、月、日、时、分时间数值调整功能,采用两个按键实现。

4)设计中时钟输入采用验证电路板上的50MHz作为基准;

5)程序设计尽可能考虑模块化、参数化设计思想,并遵循基本的格式规范,添加适当的注释及文档说明;

6)采用模块化设计方式,底层模块必须进行功能仿真;

2设计方案

根据课程设计要求,万年历电子时钟的设计框架图如图1所示。

图1设计框架图

由上图可知,万年历电子时钟由校时模块、LCD1602显示模块、分频模块、秒计数器、分计数器、时计数器、日计数器、月计数器和年计数器组成。

3模块分析

3.1秒计数器模块

秒计数器模块为60进制计数器,其有三个输入和三个输出,其中rst起复位作用,clk为1Hz的脉冲输入,stop为运行控制位,l为个位输出,h为十位输出,c为进位输出。

算法流程图如图2所示。

图2秒计数器算法流程图

源程序如下:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitycont_60sis

port(rst,clk,stop:

instd_logic;

l,h:

outstd_logic_vector(3downto0);

c:

outstd_logic);

endcont_60s;

architecturebehaveofcont_60sis

begin

process(clk,stop,rst)

variablell:

std_logic_vector(3downto0):

="0000";

variablehh:

std_logic_vector(3downto0):

="0000";

begin

if(rst='0')then

ll:

="0000";hh:

="0000";

elseifstop='0'then

ifclk'eventandclk='1'then

ll:

=ll+'1';

ifll="1010"then

ifhh="0101"thenhh:

="0000";ll:

="0000";c<='1';

elsell:

="0000";hh:

=hh+'1';c<='0';

endif;

elsec<='0';

endif;endif;

endif;endif;

l<=ll;h<=hh;

endprocess;

endarchitecturebehave;

秒计数器的波形仿真如图3所示。

如图所示,当秒计数器计数至59时,等待至clk上升沿到来时,进位输出c产生一个输出脉冲,同时秒计数器再次从0开始计数。

此外,当rst为0时h和l被置零,当stop为1时停止计时,所以设计正确。

图3秒计算器仿真图

3.2分计数器模块

分计数器模块为60进制计数器,其有两个输入和三个输出,其中rst起复位作用,clk为秒计数器的进位,l为个位输出,h为十位输出,c为进位输出。

算法流程图如图4所示。

图4分计数器算法流程图

源程序如下:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitycont_60mis

port(rst,clk:

instd_logic;

l,h:

outstd_logic_vector(3downto0);

c:

outstd_logic);

endcont_60m;

architecturebehaveofcont_60mis

begin

process(clk,rst)

variablell:

std_logic_vector(3downto0):

="0000";

variablehh:

std_logic_vector(3downto0):

="0000";

begin

if(rst='0')thenll:

="0000";hh:

="0000";

elseifclk'eventandclk='1'thenll:

=ll+'1';

ifll="1010"then

ifhh="0101"then

hh:

="0000";ll:

="0000";c<='1';

else

ll:

="0000";hh:

=hh+'1';c<='0';

endif;

elsec<='0';

endif;endif;endif;

l<=ll;h<=hh;

endprocess;

endarchitecturebehave;

分计数器的波形仿真如图5所示。

如图所示,当分计数器计数至59时,等待至clk上升沿到来时,进位输出c产生一个输出脉冲,同时分计数器再次从0开始计数。

此外,当rst为0时h和l被置零,所以设计正确。

图5分计算器仿真图

3.3时计数器模块

时计数器模块为24进制计数器,其有两个输入和三个输出,其中rst起复位作用,clk为分计数器的进位,l为个位输出,h为十位输出,c为进位输出。

算法流程图如图6所示。

图6时计数器算法流程图

源程序如下:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitycont_24is

port(rst,clk:

instd_logic;

l,h:

outstd_logic_vector(3downto0);

c:

outstd_logic);

endcont_24;

architecturebehaveofcont_24is

begin

process(clk,rst)

variablell:

std_logic_vector(3downto0):

="0000";

variablehh:

std_logic_vector(3downto0):

="0000";

begin

if(rst='0')thenll:

="0000";hh:

="0000";

elseifclk'eventandclk='1'thenll:

=ll+'1';

ifll="1010"thenll:

="0000";hh:

=hh+'1';

endif;

ifhh="0010"andll="0100"thenhh:

="0000";ll:

="0000";c<='1';

elsec<='0';

endif;endif;endif;

l<=ll;h<=hh;

endprocess;

endarchitecturebehave;

时计数器的波形仿真如图7所示。

如图所示,当时计数器计数至23时,等待至clk上升沿到来时,进位输出c产生一个输出脉冲,同时时计数器再次从0开始计数。

此外,当rst为0时h和l被置零,所以设计正确。

图7时计数器仿真图

3.4日计数器模块

日计数器模块为不规则的计数器,其有三个输入和三个输出,其中rst起复位作用,panduan用来输入平月、大月或小月,clk为时计数器的进位,l为个位输出,h为十位输出,c为进位输出。

算法流程图如图8所示。

图8日计数器算法流程图

源程序如下:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitycont_dayis

port(panduan:

instd_logic_vector(1downto0);

rst,clk:

instd_logic;

l,h:

outstd_logic_vector(3downto0);

c:

outstd_logic);

endcont_day;

architecturebehaveofcont_dayis

signalpan:

std_logic_vector(1downto0);

begin

process(clk,panduan,rst)

variablell:

std_logic_vector(3downto0):

="0001";

variablehh:

std_logic_vector(3downto0):

="0000";

begin

if(rst='0')thenll:

="0001";hh:

="0000";

elseifclk'eventandclk='1'then

ll:

=ll+'1';

ifll="1010"then

hh:

=hh+'1';ll:

="0000";

endif;

pan<=panduan;

casepanis

when"00"=>ifll="0010"andhh="0011"then

ll:

="0001";hh:

="0000";c<='1';

elsec<='0';

endif;

when"01"=>ifll="0001"andhh="0011"then

ll:

="0001";hh:

="0000";c<='1';

elsec<='0';

endif;

when"10"=>ifll="1001"andhh="0010"then

ll:

="0001";hh:

="0000";c<='1';

elsec<='0';

endif;

when"11"=>ifll="0000"andhh="0011"then

ll:

="0001";hh:

="0000";c<='1';

elsec<='0';

endif;

whenothers=>null;

endcase;

endif;endif;

l<=ll;h<=hh;

endprocess;

endarchitecturebehave;

日计数器的波形仿真如图9、图10、图11和图12所示。

如图所示,当panduan为00时,日计数器计数至31时,等待至clk上升沿到来时,进位输出c产生一个输出脉冲,当panduan为01时,日计数器计数至30时,等待至clk上升沿到来时,进位输出c产生一个输出脉冲,当panduan为10时,日计数器计数至28时,等待至clk上升沿到来时,进位输出c产生一个输出脉冲,当panduan为11时,日计数器计数至29时,等待至clk上升沿到来时,进位输出c产生一个输出脉冲,同时日计数器再次从1开始计数。

此外,当rst为0时h和l被赋初值,所以设计正确。

图9panduan为00时日计数器仿真图

图10panduan为01时日计数器仿真图

图11panduan为10时日计数器仿真图

图12panduan为11时日计数器仿真图

3.5月计数器模块

月计数器模块为12进制计数器。

此外,该模块还负责判断二月为28天还是29天,并将结果输出。

其有三个输入和三个输出,其中rst起复位作用,clk为日计数器的进位,run为闰年的判断输入,l为个位输出,h为十位输出,c为进位输出,pan为二月判断结果的输出。

算法流程图如图13所示。

图13月计数器算法流程图

源程序如下:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitycont_12is

port(rst,clk,run:

instd_logic;

c:

outstd_logic;

pan:

outstd_logic_vector(1downto0);

l,h:

outstd_logic_vector(3downto0));

endcont_12;

architecturebehaveofcont_12is

signallh:

std_logic_vector(7downto0);

begin

process(clk,rst)

variablell:

std_logic_vector(3downto0):

="0001";

variablehh:

std_logic_vector(3downto0):

="0000";

begin

if(rst='0')thenll:

="0001";hh:

="0000";

elseifclk'eventandclk='1'thenll:

=ll+'1';

ifll="1010"thenhh:

=hh+1;ll:

="0000";

endif;

ifhh="0001"andll="0011"thenll:

="0001";hh:

="0000";c<='1';

elsec<='0';

endif;endif;endif;lh<=hh≪

caselhis

when"00000001"=>pan<="00";

when"00000010"=>ifrun='1'thenpan<="11";

elsepan<="10";

endif;

when"00000011"=>pan<="00";

when"00000100"=>pan<="01";

when"00000101"=>pan<="00";

when"00000110"=>pan<="01";

when"00000111"=>pan<="00";

when"00001000"=>pan<="00";

when"00001001"=>pan<="01";

when"00010000"=>pan<="00";

when"00010001"=>pan<="01";

when"00010010"=>pan<="00";

whenothers=>null;

endcase;

l<=ll;h<=hh;

endprocess;

endarchitecturebehave;

月计数器的波形仿真如图14所示。

如图所示,当输入信号run为1时,即表示该年份为闰年,在2月份,输出判断信号pan为11,在大月,输出判断信号pan为00,在小月,输出判断信号pan为01,故设计正确。

当输入信号run为0时,即表示该年份为闰年,在2月份,输出判断信号pan为10,在大月,输出判断信号pan为00,在小月,输出判断信号pan为01,故设计正确。

图14月计数器仿真图

3.6年计数器模块

年计数器模块为1000进制计数器,但其无进位输出。

此外,该模块还负责判断判断闰年还是平年,并将结果输出。

其有两个输入和三个输出,其中rst起复位作用,clk为月计数器的进位,l为个位输出,h为十位输出,c为进位输出,run为闰年判断结果的输出。

千位计数器算法流程图如图15所示。

判断闰年的算法流程图如图16所示。

图15年计数器算法流程图

图16判断闰年算法流程图

源程序如下:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitycont_yearis

port(rst,clk:

instd_logic;

y1,y2,y3,y4:

outstd_logic_vector(3downto0);

run:

outstd_logic);

endcont_year;

architecturebehaveofcont_yearis

begin

process(clk,rst)

variableq1:

std_logic_vector(3downto0):

="0000";

variableq2:

std_logic_vector(3downto0):

="0000";

variableq3:

std_logic_vector(3downto0):

="0000";

variableq4:

std_logic_vector(3downto0):

="0010";

begin

if(rst='0')thenq1:

="0000";q2:

="0000";q3:

="0000";q4:

="0010";

elseifclk'eventandclk='1'thenq1:

=q1+'1';

ifq1="1010"thenq1:

="0000";q2:

=q2+'1';

endif;

ifq2="1010"andq1="0000"then

q2:

="0000";q3:

=q3+'1';

endif;

ifq3="1010"andq2="0000"andq1="0000"then

q3:

="0000";q4:

=q4+'1';

endif;

ifq3="1010"andq4="0000"andq2="0000"andq1="0000"then

q4:

="0000";

endif;

endif;

endif;

y1<=q1;y2<=q2;y3<=q3;y4<=q4;

endprocess;

process(clk,rst)

variableq5:

std_logic_vector(2downto0):

="000";

variableq6:

std_logic_vector(6downto0):

="0000000";

variablern:

std_logic:

='1';

begin

if(rst='0')thenq5:

="000";q6:

="0000000";

elseifclk'eventandclk='1'thenq5:

=q5+'1';

ifq5="100"thenq5:

="000";q6:

=q6+'1';

ifq6/=25andq6/=50andq6/=75thenrn:

='1';

elsern:

='0';

endif;

ifq6=100thenq6:

="0000000";

endif;

elsern:

='0';

endif;

endif;

endif;

run<=rn;

endprocess;

endarchitecturebehave;

年计数器的波形仿真如图17所示。

如图所示,每四年(除去不能被400整除的世纪年)为一闰年,其输出信号run为1,故设计正确。

图17年计数器仿真图

3.7校时模块

校时模块的主要功能是校对时间,而校时功能通过按键K1、K2来实现。

当不按K2按键时,计数器正常计时,而当按下K2按键时,根据所按的次数不同进入不同的工作模式,利用K1改变对应计数器的值,每按下K1,对应计数器的值加1。

其有七个输入和八个输出,分别为复位信号输入、时钟输入、进位输入、按键输入、进位输出和停止位输出。

校时模块的工作模式总共有6种,分别为正常计时、调分、调时、调日、调月和调年。

算法流程图如图18所示。

图18校时模块算法流程图

源程序如下:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

entityjiaoshiis

port(rst,clk,mo,fo,so,ro,yo:

instd_logic;

k1,k2:

instd_logic;

fi,si,ri,yi,ni,stop:

outstd_logic);

endjiaoshi;

architecturebehaveofjiaoshiis

signala:

std_logic_vector(2downto0);

signalbuf1,buf2:

std_logic;

begin

process(k1,k2,clk,rst)

begin

ifclk'eventandclk='1'then

ifk1='0'thenbuf1<='1';

elsebuf1<='0';

endif;endif;

ifclk'eventandclk='1'then

ifk2='0'thenbuf2<='1';

elsebuf2<='0';

endif;

endif;

ifbuf2'eventandbuf2='1'then

a<=a+1;

ifa="101"then

a<="000";

endif;

endif;

if(rst='0')thena<="000";

endif;

caseais

when"000"=>stop<='0';fi<=mo;si<=fo;ri<=so;yi<=ro;ni<=yo;

when"001"=>stop<='1';fi<=buf1;si<='0';ri<='0';yi<='0';ni<='0';