Allegro中走线等长设置进阶.docx

《Allegro中走线等长设置进阶.docx》由会员分享,可在线阅读,更多相关《Allegro中走线等长设置进阶.docx(9页珍藏版)》请在冰豆网上搜索。

Allegro中走线等长设置进阶

Allegro中走线等长设置进阶

————————————————————————————————作者:

————————————————————————————————日期:

在高速电路设计中,走线的等长显得越来越重要,因此设置等长这问题也就产生了,对于简单走线等长在以前文档中都有涉及这里不再复述了,下面内容将给大家介绍一下有关Xnet等长的设置问题,如现在主板DDR,IDE等部分设等长问题.

注意:

以下设置方法不是公板方式,是我自己摸索的设置方法,所以大家不必效仿,仅供参考!

如果大家有任何其它或简单方法也请分享一下经验!

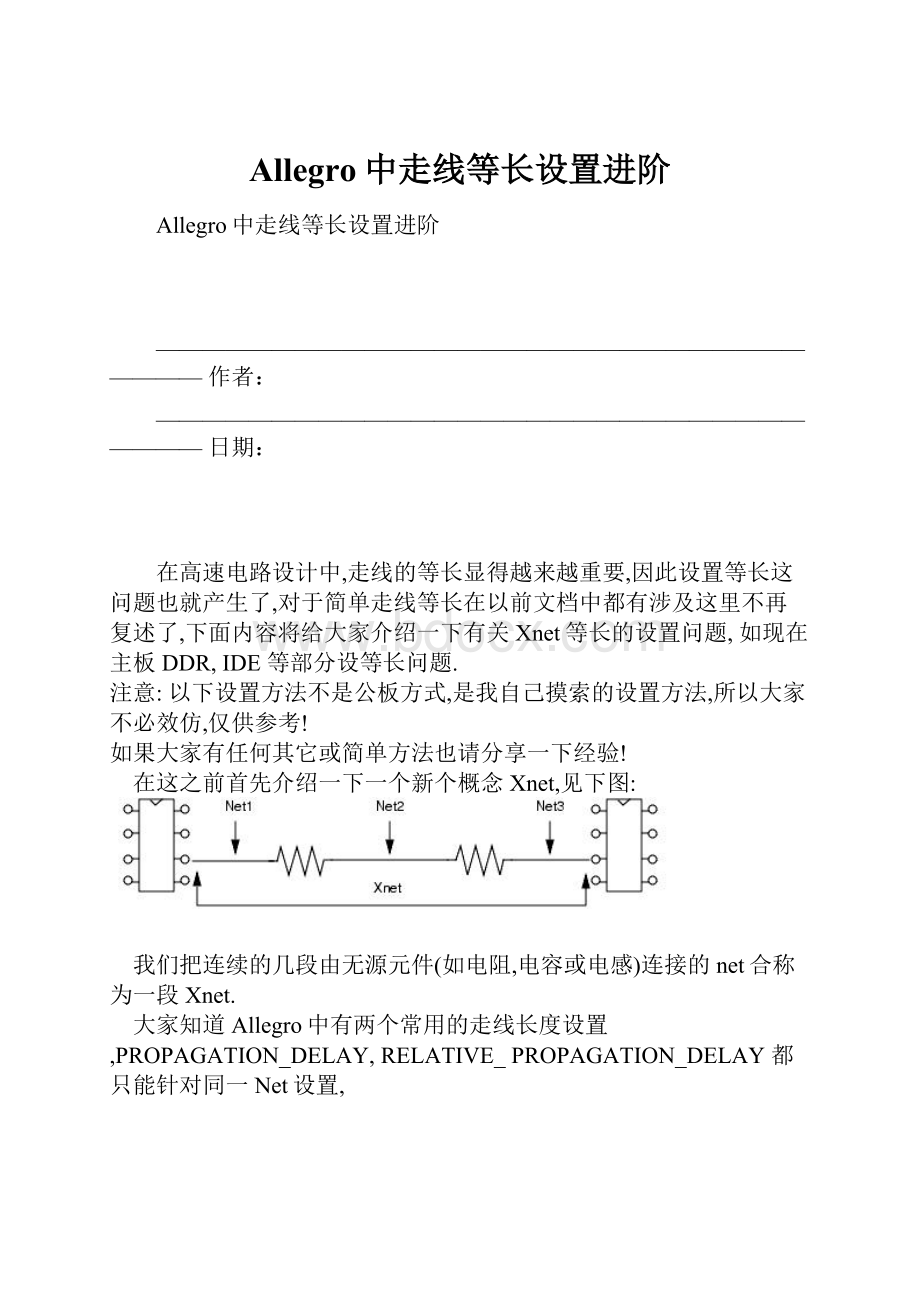

在这之前首先介绍一下一个新个概念Xnet,见下图:

我们把连续的几段由无源元件(如电阻,电容或电感)连接的net合称为一段Xnet.

大家知道Allegro中有两个常用的走线长度设置,PROPAGATION_DELAY,RELATIVE_PROPAGATION_DELAY都只能针对同一Net设置,

下面是一个具体案例:

现在要求U1到U2的走线Net*A+Net*B等长,误差为+/-20Mil,最简单的方式就是分别设置Net*A等长和Net*B等长,误差各为+/-10Mil,这样是可以达到要求,不过会加大Layout工程师绕线的难度,因为可能Net*A部分空间比较大有足够的绕线空间,而Net*B部分没有空间绕线,所以就比较难达到要求.

如果一种设置能把Net*A与Net*B相加,然后再做等长比对,这样就可以解决问题了,好的就是Allegro都早为这些问题考虑过了,只要把Net*A与Net*B设置为一个Xnet问题就解决一半了.

下面内容将详细介绍怎样设置Xnet与Xnet等长.

第一部分:

Xnet设置

(下面步骤可能有些简单,不过能达到效果)

0,需要AllegroExport版本或SPECCTRAQuest中设置,还好大家有CrackedLicense天下无敌,什么版本都有J

1,开启AllegroExport或SPECCTRAQuest(以下省略,用Allegro简称这两个),Open需要设置Xnet的板子.

2,点击菜单Analyze>SI/EMISim>Model…(比正常方式设置Model简单了些)出来的建议定义DCnet直接Yes即可,然后出现下面的Model设置窗体:

3,直接在DevTypeValue/Refdes中选择要设定Model的器件或直接在板子上点选要设置Model的器件;

4,点选CreateModel,建立该零件的Model,(如果已经有该零件的Model,并在前面定义,然后FindModel即可,这里主要介绍没有的情况)

在出现对话框中选择CreateESpiceDevicemodel,点击OK

5,出现下面窗体:

ModelName:

输入产生Model的名字

Circuittype:

选择Type,电阻,电感或电容

Value:

值

SinglePin:

各Pin的连接顺序,中间为空格,

这里要注意要看零件的pin的排列,12345678,就是:

1和2是一个电阻,其它同理所以如果就是普通电阻电容那就更简单了.

CommonPin:

这里不用管它,空着就可以.

上面都输入好了就点击OK,完成Model的建立.

点击OK退出就可以发现连接该排阻的两边的Net都有了个Xnet属性,如下图:

这样就可以搞定Xnet,很简单吧!

下面就开始等长设置吧!

第二部分针对Xnet部分的等长设置

设置好了Xnet后就可以在Allegro中设置该Xnet的等长了,有两种方法可以设置Xnet的等长.

第一种,使用Edit>Properties定义

注意必须使用PinPair才能定义Xnet等长

RELATIVE_PROPAGATION_DELAY=GroupX:

G:

U1.5:

U2.4:

0:

20

在没有定义Xnet之前这样定义时会提示错误的

其它的和前面的等长设置方法都一样.

如果大家觉得这样设置有些麻烦的话,还有一招可以使用,见下面:

第二种,ConstraintManager设置

1,开启ConstraintManager,点选菜单Setup>ElectricalConstraintSpreadsheet或直接点击工具栏

出现ConstraintManager窗体:

对于ConstraintManager的一般使用方法这里不再做详细介绍,如果用户对这部分不熟悉

可以参考其它有关ConstraintManager使用进行学习.

2,因为我们目的是要设置等长,所以我们用RelativePropagationDelay这属性,从左边控制栏中选择Net>Routing>RelativePropagationDelay,

3,在右边就会显示整块板子所有的Net或Xnet,

4,建立需要等长的PinPair,右键点击需要建立PinPair的Xnet

选择起始Pin和结束Pin,

注意:

1,这里没有先后顺序.

2,如果PinPair的两个PinType全是Passive的话不能Creat,所以这里还需要定义一下Pin的形态,如:

Output,Input,Bidirectional等

下面是介绍如何在Allegro中定义Pintype。

如何在Allegro中定义PinType?

1,点击菜单Edit>Properties…

2,在Find栏位中仅勾选Pin

3,直接在PCB中选中需要修改PinType的Pin

4,出现下面窗体:

选择Pinuse,在右边定义为BI即可

5,Ok完成PinType定义

这样就可以CreateXnet的PinPair了。

点击Apply或OK就完成PinPair设置.

5,设置等长Group

当XnetPinPair建立完成后其它设置就和普通PinPair设置等长是一样的.

使用Ctrl键复选所有需要设置等长的PinPair,右键Create>MatchGroup

输入Group名字;

注意:

Scope选择Global