天津大学数字集成电路考点.docx

《天津大学数字集成电路考点.docx》由会员分享,可在线阅读,更多相关《天津大学数字集成电路考点.docx(17页珍藏版)》请在冰豆网上搜索。

天津大学数字集成电路考点

第一章导线

1.集成电路的导线已经形成复杂的几何形体,引起电容、电阻和电感等寄生参数效应。

∙会使传播延时增加,性能下降

∙会影响功率和能耗的分布

∙会引起额外的噪声来源,影响电路的可靠性

2.树结构的RC网络

∙该电路只有一个输入点(s)

∙所有的电容都在某个节点与地之间

∙该电路不包括任何电阻回路(形成树结构)

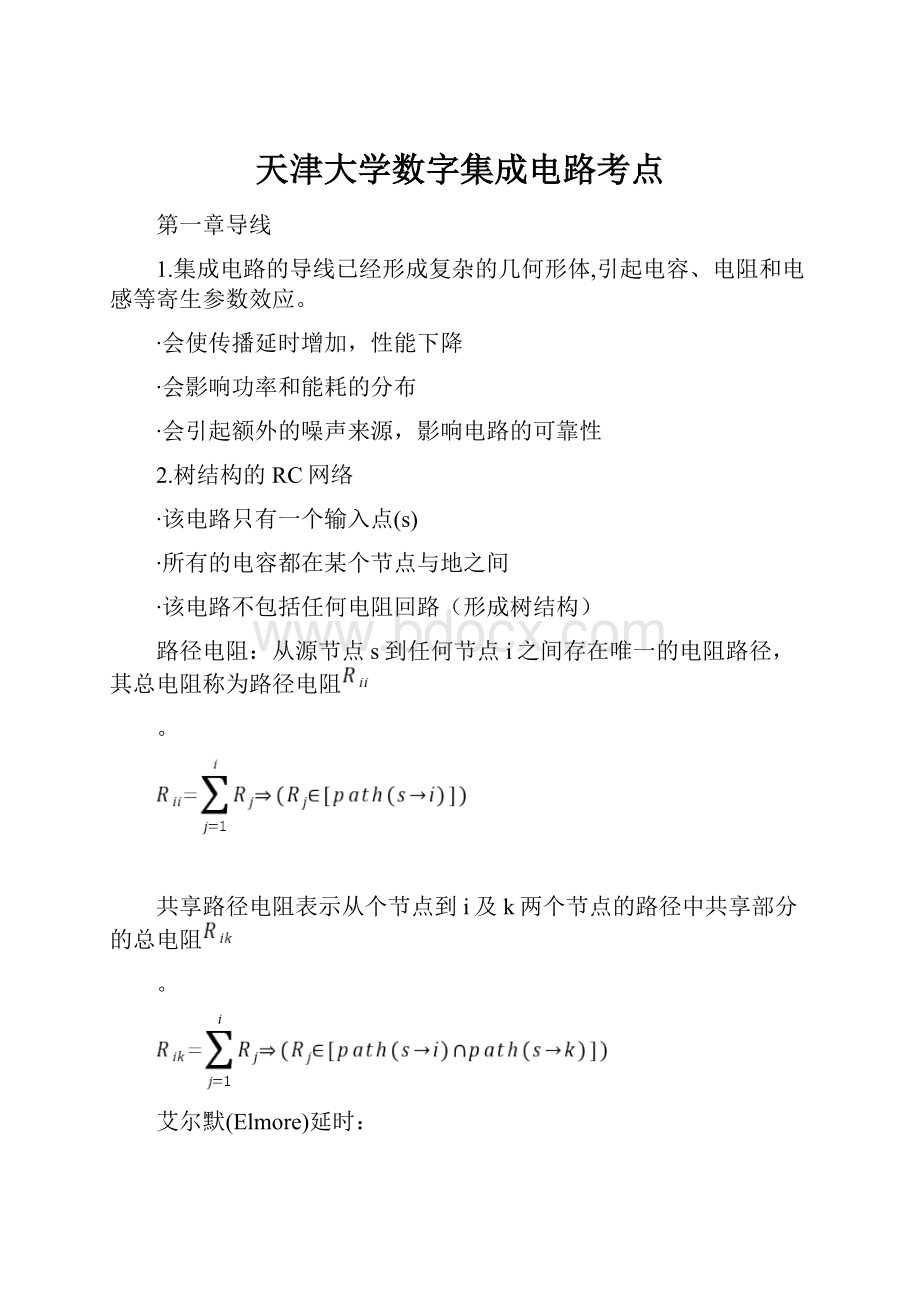

路径电阻:

从源节点s到任何节点i之间存在唯一的电阻路径,其总电阻称为路径电阻

。

共享路径电阻表示从个节点到i及k两个节点的路径中共享部分的总电阻

。

艾尔默(Elmore)延时:

无分支RC链,即梯形链的艾尔默延时:

用路径电阻替换共享路径电阻

3.导线RC延时模型

理想导线:

没有任何附加参数或寄生元件的简单连线。

导线一端的变化会立刻传递到另一端;导线是一个等势区。

集总式RC模型:

导线的电阻部分很小,并且开关频率在低至中间范围;把分布的电容集总为单个电容。

分布式RC模型:

导线寄生参数沿导线长度分布;导线寄生参数沿导线长度分布。

模型和

模型的艾尔默延时计算。

T2,T3,Pi3模型的延时

第二章CMOS反相器

1.CMOS静态特性

1)输出摆幅等于电源电压即高电平为VDD,低电平为GND,噪声容限大;

2)逻辑电平与器件尺寸无关,所以晶体管可以采用最小尺寸,属于无比例逻辑;

3)稳态时输出与VDD或者GND之间总存在一条有限的电阻通路;

4)输入阻抗很高,理论上,单个反相器可以驱动无数个门;

5)稳态时候,电源和地之间没有直接的通路,没有电流存在(忽略漏电流),即该门电路不消耗任何静态功耗。

2.VTC,参数

开关阈值

:

定义为

的点(PMOS和NMOS都处于饱和区)。

,开关阈值取决于r,它是PMOS与NMOS的相对驱动强度比。

相对与器件尺寸比值不敏感。

增大Wp和Wn使

分别移向VDD和GND。

噪声容限:

已知

和

是

时的点,噪声容限

和

定义为

,

。

器件参数对VTC的影响:

1)工艺的不确定引起开关阈值的平移,好PMOS差NMOS右移,好NMOS差PMOS左移。

2)降低电源电压,工作在亚阈值。

3.CMOS反相器动态特性

栅漏电容

:

引起瞬态响应的输出过冲。

负载电容

:

由内部扩散电容

、互连线电容

和扇出电容

三部分组成。

反相器的延时分析:

如何减小传播延时

1)减小

:

细致的版图设计

2)增加晶体管宽长比

:

容易引起扩散电容增加(自载效应)

3)提高VDD,牺牲能量的损耗来换取性能的提高。

反相器尺寸选择:

反相器的本征延时与门的尺寸无关;无负载时,增加门的尺寸不能减少延时;有负载时,S很大时反相器延时趋于本征延时时,增大尺寸便不会有什么改善。

第三章静态CMOS组合逻辑

1.基本的电路结构

上拉网络PUN和下拉网络PDN:

PDN由NMOS构成;PUN由PMOS构成。

因为NMOS产生“强0”而PMOS器件产生“强1”

NMOS串联相当于“与”逻辑,PMOS串联相当于“或”逻辑;NMOS并联相当于“或”逻辑,PMOS并联相当于“与”逻辑。

NAND:

两个PMOS并连,与两个NMOS串连互补;

NOR:

两个PMOS串连,与两个NMOS并连互补;

OR:

NOR后接INVERTER

2.复合门设计

关于扇入:

传播延时在最坏的情况下与扇入数的平方成正比

大扇入时的设计技巧:

1)调整晶体管尺寸;只有当负载以扇出电容为主时,才有效果。

逐级加大晶体管尺寸:

距输出越近,晶体管尺寸越小。

2)重新排晶体管的顺序,使关键路径靠近输出端。

3)重构逻辑结构,变换逻辑方程的形式,降低对扇入的要求,从而减少门延时

4)在输出端和负载之间插入缓冲链。

3.有比逻辑电路

目的:

减少实现一个给定逻辑功能所需要的晶体管数目,但经常以降低稳定性和付出额外功耗为代价。

4.差分级联电压开关逻辑

静态逻辑:

互补NMOS下拉管,交叉连接PMOS上拉管;

负载:

仅一个PMOS管,具有伪NMOS优点;

差分型:

同时要求正反输入,面积大,但在要求互补输出或两个下拉网络能共享时比较有利;

DCVSL比通常的CMOS逻辑慢(因Latch反馈作用有滞后现象,但在特定情况下很快,例如存储器纠错逻辑的XOR门);

无静态功耗,但有较大的翻转过渡(Cross-over)电流。

5.传输管逻辑

传输管逻辑实现的AND门,需要较少的晶体管实现给定的功能

通过允许原始输入驱动栅端和源-漏端来减少实现逻辑所需要的晶体管数目。

第四章动态CMOS组合逻辑

1.动态逻辑门的两个操作阶段

动态逻辑门的工作可以分为两个主要阶段:

预充电和求值,处于何种工作模式由时钟信号CLK决定。

预充电:

当CLK=0时输出节点out被PMOS管Mp预充电值VDD,NMOS求值管Me关断,下拉路径不工作。

求值:

当CLK=1时预充电管Mp关断,求值管Me导通求值。

2.动态门的特点

1)逻辑功能仅由PDN实现(紧凑),晶体管数目是N+2(静态CMOS需2N个晶体管),输入电容与伪NMOS逻辑相同

2)全摆幅输出(VOL=GND及VOH=VDD)

3)无比逻辑–器件尺寸不影响逻辑电平

4)上拉速度改善,下拉时间变慢

5)快速的开关速度

6)输入只允许在预充电阶段变化,在求值阶段必须保持稳定

7)简单的动态CMOS逻辑级不能串联

8)需要预充电/求值时钟

9)总功耗通常高于静态CMOS

10)噪声容限(NML)小,对噪声敏感

11)对漏电敏感

12)有电荷分享问题

3.动态设计中的信号完整性问题

1)电荷泄露:

一个动态门的工作取决于输出值在电容上的动态存储。

如果下拉网络关断,那么理想情况下,输出在求值阶段应当维持在预充电状态的VDD。

然而由于存在漏电电流,这一电荷将逐渐泄露掉,最终会使这个门的工作出错。

漏电流来源主要是亚阈值导电和反偏二极管。

解决办法:

增加一个泄露晶体管补偿漏电。

2)电荷分享:

原先存放在CL上的电荷由CL和CA重新分布(分享),导致输出电压有所下降,鲁棒性降低。

解决办法:

采用时钟驱动的晶体管预充电内部关键节点,代价是增加了面积和功耗。

4.动态门的级联问题

简单的动态CMOS逻辑不能级联应用,需要采用多米诺逻辑,

一个多米诺(Domino)逻辑块由一个n型动态逻辑块后面接一个静态反相器构成;由于多米诺模块输出由一个低阻抗的静态反相器驱动,提高了抗噪声能力。

多米诺逻辑可以串联,串联的数目取决于在求值的时钟阶段,相串联的各级动态逻辑能来得及一个接一个地求值完毕。

多米诺逻辑的特点:

逻辑求值的传播如同多米诺骨牌的倾倒,求值阶段的时间决定了(允许的)逻辑深度;只能实现非反相的逻辑(所有的门均为非反相);只有一个过渡被优化;门为无比逻辑,但电平恢复电路为有比逻辑;节点必须在预充电期间被预充电(这可能限制了PMOS的最小尺寸);求值期间,输入必须稳定,对nlogic只能有一个上升的过渡。

速度非常快;增加电平恢复电路可以减少漏电和电荷分享问题。

第五章静态时序逻辑电路

两种存储机理:

正反馈和基于电荷

1.存储单元的实现方法比较

利用正反馈:

静态,信号可以”无限”保持;鲁棒性好,对扰动不敏感;对触发脉冲宽度的要求:

触发脉冲的宽度须稍大于沿环路总的传播时间,即两个反相器平均延时的两倍;尺寸大,限制了在计算结构如流水线式数据通路中的应用。

利用电荷存储:

动态(要求定期刷新,要求从存储电容中读出信号时不会干扰所存储的电荷,因此要求具有高输入阻抗的器件)

双稳态电路:

过渡区的增益应当大于1,AB为稳态工作点,C为亚稳态点

触发翻转(写入数据)的方法:

(1)切断反馈环(采用Mux)

(2)触发强度超过反馈环强制驱动(正确设计尺寸)

2.时间参数:

1)建立时间

:

在时钟翻转(对于正沿触发寄存器为0

1翻转)之前数据输入必须有效的时间。

2)维持时间

:

在时钟边沿之后数据输入必须仍然有效的时间。

3)传播延时

:

假设建立时间和维持时间都满足要求,输入D端的数据在最坏情况下的延时

(相对于时钟边沿)之后被复制到输出端Q。

3.Latch和Register

锁存器:

电平灵敏,不是边沿触发;可以是正电平灵敏或负电平灵敏,当时钟为高电平(或低电平)时,输入的任何变化经过一段延迟就会反映在输出端上;有可能发生竞争(Race)现象,只能通过使时钟脉冲的宽度小于(包括反相器在内的)环路的传播时间来避免。

最高时钟频率(最小时钟周期)应满足:

维持时间需满足:

写入方法:

基于(传输门实现)Mux:

尺寸设计容易,晶体管数目多;

弱反相器实现。

主从边沿触发寄存器:

时钟为高电平时,主Latch维持,QM值保持不变,输出值Q等于时钟上升沿前的输入D的值,效果等同于“正沿触发”

效果等同于“负沿触发”的主从寄存器只需互换正Latch和负Latch的位置。

4.时钟重叠问题

非理想时钟会有时钟重叠现象,用伪静态锁存器构成的主从触发器当Clk和反Clk发生重迭时,可能引起失效:

当Clk和反Clk同时为高时,A点同时为In和B点驱动,造成不定状态。

当Clk和反Clk同时为高一段较长时间时,In可以直接穿通经过主从触发器。

解决办法:

产生两相不重叠的时钟,但时钟不重迭部分不能太长以免漏电时间过长引起出错。

第六章动态时序逻辑电路

1.动态Latch和Register

动态传输门边沿触发寄存器:

只需8个晶体管,节省功耗和提高性能,甚·至可只用NMOS实现。

动态特点:

比静态Latch和Register简单;基于在寄生电容上存储电荷,由于漏电需要周期刷新(或经常更新数据);“不破坏地”读信息:

因此需要输入高阻抗的器件。

问题:

高阻抗的内部动态节点易受噪声源的干扰;漏电影响了低功耗(例如停止时钟以节省功耗)技术;内部动态节点的电压并不跟踪电源电压的变化,从而降低噪声容限。

解决办法:

增加一个弱反馈反相器这会增加抗噪声能力,但会增加延时除高性能数据通路外,一般均应使寄存器成为伪静态的或静态的。

2.动态Register的时钟重叠问题

在0-0重叠期间,T1的PMOS和T2的PMOS同时导通,形成数据从寄存器的D输入留到Q输出的直接通路,对于1-1重叠亦是如此。

这可以通过强加维持时间约束来解决:

0-0重叠竞争限制条件:

1-1重叠竞争限制条件:

3.C2MOS主从正沿触发寄存器

时钟控制CMOS寄存器的工作分为两个阶段:

当CLK=0时,第一个三态驱动器导通,此时的主级像一个反相器在内部节点QM采样D的反相数据,因此主级处于求值模式。

同时从级处在高阻抗模式,即维持模式。

晶体管M7,M8均关断,输出Q维持其原来存储在C2上的值。

当CLK=1时,主级处于维持模式,M3-M4关断,M7-M8导通,从级求值。

存放在C1上的值经过从级传输到输出节点,此时的从级作用像一个反相器。

特点:

只要时钟边沿的上升和下降时间足够小,具有CLK和反CLK时钟控制的这一C2MOS寄存器对时钟重叠时不敏感的。

4.真单相位时钟控制(TSPC)Latch和Register

正电平Latch:

CLK=1时透明,CLK=0时维持;负电平Latch相反。

简化的TSPCLatch:

优点:

减少了一个时钟控制管,同时也减少了时钟负载

缺点:

内部节点电平不是全幅摆(例如A点有阈值损失)

嵌入逻辑功能的TSPC:

Logic嵌入Latch内ANDLatch

TSPCLatch特点:

优点:

时钟为“真正”单相位;可将逻辑功能嵌入锁存器中,减少与锁存器的相关延时。

缺点:

与简单动态Latch(传输门+反相器)相比,晶体管数目稍有增加;时钟使输出节点浮空(高阻态)时,易受其它信号耦合的影响;驱动传输门时输出节点会发生电荷分享。

第七章数字电路的时序问题

1.分类

在数字系统中,信号可以根据他们与本地时钟的关系来分类。

只有在预先决定的时间周期上发生翻转的信号相对于系统时钟可分为同步的、中等同步的或近似同步的。

反之,可以在任意时间发生翻转的信号成为异步信号。

一个同步信号具有与本地时钟完全相同的频率并与该时钟保持一个已知的固定相位差。

中等同步信号不仅与本地时钟具有同样的频率,而且相对于该时钟具有未知的相位差。

一个近似同步信号是一个频率与本地时钟频率名义上相同但其真正频率却稍有不同的信号。

异步信号可以在任何时候随意变化,并且他们不服从任何本地时钟。

2.非理想时钟引起的问题

时钟偏差:

集成电路中一个时钟翻转的到达时间在空间上的差别通常称为时钟偏差。

时钟偏差是由时钟路径的静态不匹配以及时钟在负载上的差异造成的。

时钟偏差现象无论对时序系统的性能还是功能都有很大影响。

正偏差能够增加电路的数据通过量,但有可能导致出错,负偏差显著提高抗竞争能力,避免出错,但会降低电路性能。

时钟抖动:

时钟抖动是指在芯片的某一个给定点上的时钟发生暂时性的变化,即时钟周期在每个不同的周期上可以缩短或加长。

抖动是一个平均值为零的随机变量,绝对抖动

是指在某一给定位置处的一个时钟边沿相对于理想的周期性参照时钟边沿在最坏情况下的变化(绝对值)。

抖动直接影响时序系统的性能,最坏情况下可用来完成操作的总时间减少了

,降低了时序电路的性能。

---精心整理,希望对您有所帮助