实验VHDL实验报告.docx

《实验VHDL实验报告.docx》由会员分享,可在线阅读,更多相关《实验VHDL实验报告.docx(15页珍藏版)》请在冰豆网上搜索。

实验VHDL实验报告

【关键字】实验

项目一数据选择器

一、实验与设计要求

1.熟悉MAX+PLUSII的编译环境,掌握该集成环境各个菜单项的使用;

2.了解MAX+PLUSII的VHDL程序设计输入方法,初步了解该软件的仿真环境;

3.初步运用VHDL编程,体会硬件描述语言的先进性;

4.理解VHDL语言的并发执行的特点;

5.熟悉VHDL语法

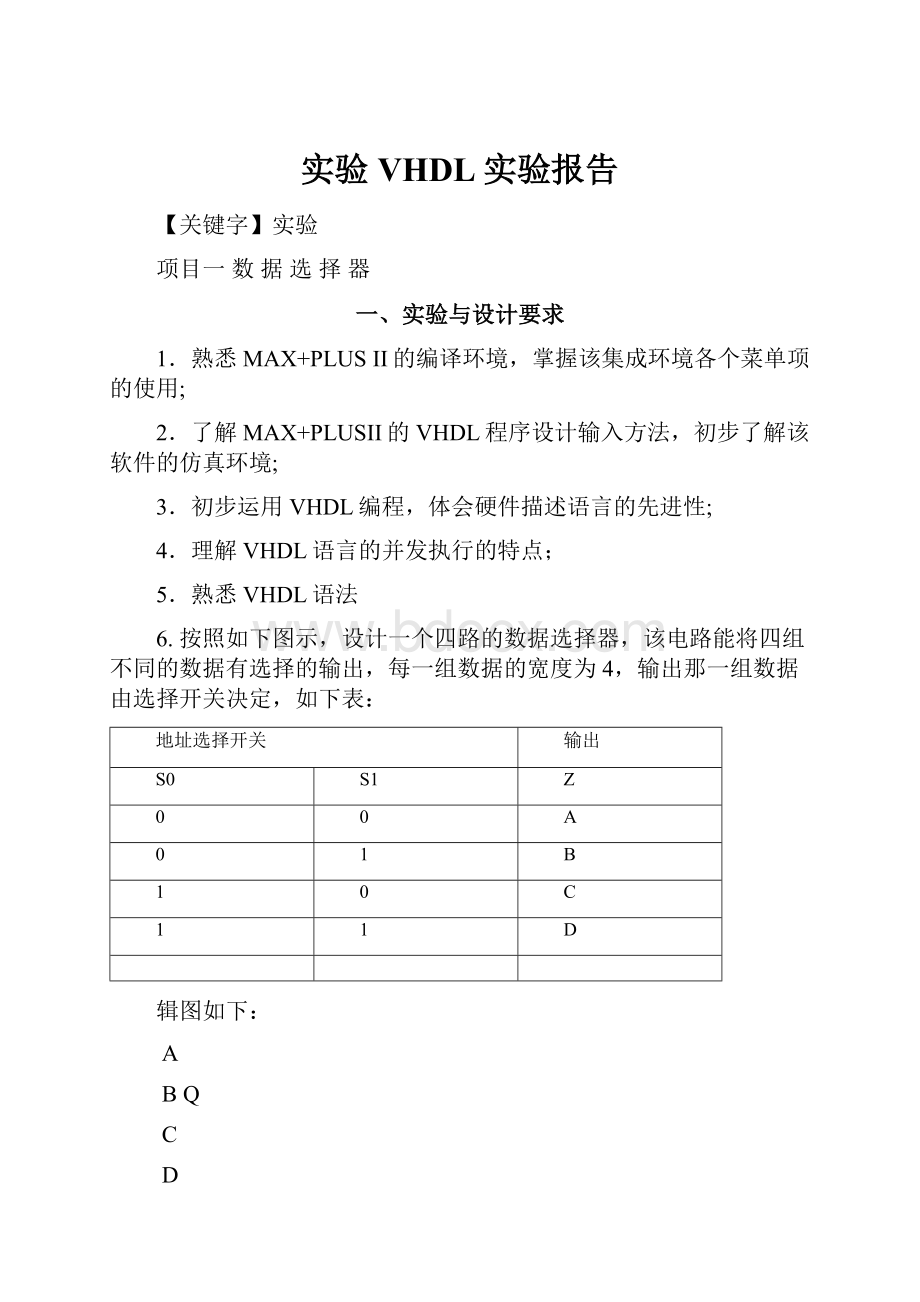

6.按照如下图示,设计一个四路的数据选择器,该电路能将四组不同的数据有选择的输出,每一组数据的宽度为4,输出那一组数据由选择开关决定,如下表:

地址选择开关

输出

S0

S1

Z

0

0

A

0

1

B

1

0

C

1

1

D

辑图如下:

A

BQ

C

D

S0

S1

二、实验与设计方法

1.加入MAX+PLUSII软件之前,在E盘上新建一个工作目录\lyung。

2.加入MAX+PLUSII文本编辑器,编写VHDL程序,并保存文件至\lyung\mux41.vhd:

3.将工程指向当前文件并编译当前文件。

4.建立波形仿真文件,设置输入、输出端口及输入端口的信号波形,保存波形仿真文件。

5.加入仿真器工作环境,查看波形仿真结果。

6.选择器件,为电路端口分配FPGA器件引脚。

7.进行第二次编译(包括逻辑综合和器件工艺映射),生成目标文件(*.sof等)。

8.将目标文件下载至FPGA器件。

9.在实验台上进行实际操作,验证设计的正确性。

三、实验与设计结果

通过实验,初步熟悉了MAX+PLUSII的编译环境,并掌握该集成环境各个菜单项的使用。

实验过程中,了解了MAX+PLUSII的VHDL程序设计输入方法,初步运用VHDL编程,成功的按照实验要求设计了程序的VHDL源码(见附件1),熟悉了VHDL语法,理解了VHDL语言的并发执行的特点;并进行了仿真实验(仿真实验截图见图4-1),初步了解该软件的仿真环境,并成功的将文件烧入实验平台,成功通过了测试(实验平台截图见图4-2)。

四、程序源码及实验截图

4-0、VHDL源码如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYmux41IS

PORT(a,b,c,d:

INSTD_LOGIC_VECTOR(3DOWNTO0);

s1,s0:

INSTD_LOGIC;

q:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDmux41;

ARCHITECTUREbehaveOFmux41IS

SIGNALsel:

STD_LOGIC_VECTOR(1DOWNTO0);

BEGIN

sel<=s1&s0;

q<=aWHENsel="00"ELSE

bWHENsel="01"ELSE

cWHENsel="10"ELSE

dWHENsel="11"ELSE

"XXXX";

ENDbehave;

图4-2实验平台实验

项目二三—八译码器

一、实验与设计要求

1.掌握组合逻辑电路的设计的一般步骤和方法;

2.掌握一般电路设计要求及其设计知识;

3.设计一个3-8译码器,此电路有三个输入端(A,B,C),八个输出端D[7··0];当输入为为不同的值(0~7)时,只有对应的输出端才有输出;如下图所示:

3-8

译

码

器

Y0

AY1

Y2

BY3

Y4

CY5

Y6

Y7

二、实验与设计方法

1.建立真值表

输入

输出

A

B

C

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

0

0

0

1

0

0

0

0

0

0

0

0

0

1

0

1

0

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

0

0

1

1

0

0

0

1

0

0

0

0

1

0

0

0

0

0

0

1

0

0

0

1

0

1

0

0

0

0

0

1

0

0

1

1

0

0

0

0

0

0

0

1

0

1

1

1

0

0

0

0

0

0

0

1

2.编写VHDL语言程序

3.将工程指向当前文件并编译当前文件。

4.建立波形仿真文件,设置输入、输出端口及输入端口的信号波形,保存波形仿真文件。

5.进入仿真器工作环境,查看波形仿真结果。

6.选择器件,为电路端口分配FPGA器件引脚。

7.进行第二次编译(包括逻辑综合和器件工艺映射),生成目标文件(*.sof等)。

8.将目标文件下载至FPGA器件。

9.在实验台上进行实际操作,验证设计的正确性

三、实验与设计结果

通过实验,初步掌握了一般电路设计要求及其设计知识,并掌握了组合逻辑电路的设计的一般步骤和方法,按照实验的要求成功设计了实验的VHDL程序(程序源码见四――源代码),并成功的进行了程序的仿真,并成功将程序烧入实验平台(实验平台见图4-1)。

四、程序源码及实验截图

VHDL源码如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYdec38case1IS

PORT(a,b,c:

INSTD_LOGIC;

y:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));

ENDdec38case1;

ARCHITECTUREbehaveOFdec38case1IS

SIGNALindata:

STD_LOGIC_VECTOR(2DOWNTO0);

BEGIN

indata<=c&b&a;

PROCESS(indata)

BEGIN

CASEindataIS

WHEN"000"=>y<="";

WHEN"001"=>y<="";

WHEN"010"=>y<="";

WHEN"011"=>y<="";

WHEN"100"=>y<="";

WHEN"101"=>y<="";

WHEN"110"=>y<="";

WHEN"XX-"=>y<="01111111";

WHENOTHERS=>y<="XXXXXXXX";

ENDCASE;

ENDPROCESS;

ENDbehave;

图4-1实验平台实验

项目三数字钟的设计

一、实验与设计要求

1.掌握逻辑电路的系统设计方法;

2.熟练使用VHDL语言进行电路设计;

4.设计的电路应具备以下功能:

数字钟24小时循环计数,能显示时、分、秒,并能对时和分进行调整和全部清零;

5.完成电路设计,对设计的正确性进行验证;

7.编写用VHDL语言描述的源程序;

8.在MAX软件平台上完成编译和功能仿真;

9.进行引脚分配,最后生成目标文件下载至FPGA器件,在实验台上进行实际操作,验证电路系统设计的正确性。

二、实验与设计方法

1.分析设计电路的特性,并进行电路抽象处理。

2.整个电路划分为:

秒钟模块、分钟模块、小时模块和显示模块;小时模块和分钟模块中集成调整功能。

3.确定各模块功能:

秒钟模块:

用一个六十进制计数器组成,满六十后向分钟进一;

分钟模块:

和秒钟模块一样,用一个六十进制计数器组成,满六十后向小时进一;

小时模块:

用一个二十四进制计数器组成,满24回到0;,以完成24小时计数;

数码管显示模块:

用1KHz以上频率的时钟选择数码管;分别循环显示时、分、秒,

数码管管选信号的产生采用3-8译码器。

4.根据逻辑图(见图4-3),确定引脚分配(见附件4-4),并编写程序.

5.按项目一所述的步骤和方法依次进行设计输入,编译,仿真,引脚分配,最后生成目标文件下载至FPGA器件,在实验台上进行实际操作,验证设计的正确性。

三、实验与设计结果

通过实验,掌握了逻辑电路的系统设计方法,并初步使用VHDL语言进行电路设计,成功设计出符合要求的电路源程序(源代码见),并进行了功能仿真(仿真图见图4-1),并成功在实验平台上进行了验证(见图4-2)。

四、程序源码及实验截图

图4-1波形仿真

图4-2实验平台实验

G-OUT[]

clkCLKS-OUT[]

resetRESETOVER

D1SEL1

SECOND_G[]D2SEL2

SECOND_S[]D3SEL3

MINUTE_G[]SEL[]IN[]D4SEL4

MINUTE_S[]D5SEL5

RESTG-OUT[]HOUR_G[]OUT[]D6SEL6

SETCINS-OUT[]HOUR_S[]D7SEL7

setminDQSETMINOVERSCAN_CLKD8SEL8

>

OUT[7..1]

ESETG-OUT[]

MININS-OUT[]

sethourDQSETHOUR

>

scan_clk

图4-3整个电路的结构逻辑图

附件4-4:

引脚分配:

数码管的段选out7~out1:

PIN51、49、48、47、46、44、43;

数码管的位选sel8~sel1:

PIN8、102、101、100、99、98、97、96;

清零、设分、设时(reset、setmin、sethuor)对应k9、k8、k7:

PIN59、60、62;

秒时钟(clk):

pin122;输出扫描(刷新)和调时扫描时钟(scan_clk):

PIN55

附件:

程序源码

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYclksystemIS

PORT(cclk,clr,xclk:

INSTD_LOGIC;

minset,hourset:

INSTD_LOGIC;--时、分调节按键

bihuaag:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

gsel:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)

);

END;

ARCHITECTURErtlOFclksystemIS

SIGNALbcd1ns:

STD_LOGIC_VECTOR(3DOWNTO0);--秒个位

SIGNALbcd10ns:

STD_LOGIC_VECTOR(3DOWNTO0);--秒个位

SIGNALbcd1nms:

STD_LOGIC_VECTOR(3DOWNTO0);--分个位

SIGNALbcd10nms:

STD_LOGIC_VECTOR(3DOWNTO0);--分十位

SIGNALbcd1nhs:

STD_LOGIC_VECTOR(3DOWNTO0);--时个位

SIGNALbcd10nhs:

STD_LOGIC_VECTOR(3DOWNTO0);--时十位

SIGNALclkm,clkh:

STD_LOGIC;

SIGNALsco,mco:

STD_LOGIC;--分、时计数标志信号

SIGNALclockadjq:

STD_LOGIC;--计时/调时选择信号

SIGNALminsetq,hoursetq:

STD_LOGIC;--时、分调节信号

SIGNALgscnt:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALsmhdis:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

clkm<=scoWHENminsetq='0'ELSEminsetq;

clkh<=mcoWHENhoursetq='0'ELSEhoursetq;

sp:

PROCESS(clr,cclk)--秒进程

VARIABLEbcd1nsv:

STD_LOGIC_VECTOR(3DOWNTO0);--秒个位

VARIABLEbcd10nsv:

STD_LOGIC_VECTOR(3DOWNTO0);--秒个位

BEGIN

IFclr='0'THEN

bcd1nsv:

="0000";

bcd10nsv:

="0000";

ELSIF(cclk'EVENTANDcclk='1')THEN

IFbcd1nsv=9THEN

bcd1nsv:

="0000";

bcd10nsv:

=bcd10nsv+1;

IF(bcd10nsv=6)THEN

bcd10nsv:

="0000";

sco<='1';--置分计数标志

ELSE

sco<='0';

ENDIF;

ELSE

bcd1nsv:

=bcd1nsv+1;

ENDIF;

ENDIF;

bcd1ns<=bcd1nsv;

bcd10ns<=bcd10nsv;

ENDPROCESS;

mp:

PROCESS(clr,clkm)--分进程

VARIABLEbcd1nmsv:

STD_LOGIC_VECTOR(3DOWNTO0);--分个位

VARIABLEbcd10nmsv:

STD_LOGIC_VECTOR(3DOWNTO0);--分十位

BEGIN

IFclr='0'THEN

bcd1nmsv:

="0000";

bcd10nmsv:

="0000";

ELSIFclkm'EVENTANDclkm='1'THEN

IFbcd1nmsv=9THEN

bcd1nmsv:

="0000";

bcd10nmsv:

=bcd10nmsv+1;

IF(bcd10nmsv=6)THEN

bcd10nmsv:

="0000";

mco<='1';--置时计数标志

ELSE

mco<='0';

ENDIF;

ELSE

bcd1nmsv:

=bcd1nmsv+1;

ENDIF;

ENDIF;

bcd1nms<=bcd1nmsv;

bcd10nms<=bcd10nmsv;

ENDPROCESS;

hp:

PROCESS(clr,clkh)--时进程

VARIABLEbcd1nhsv:

STD_LOGIC_VECTOR(3DOWNTO0);--时个位

VARIABLEbcd10nhsv:

STD_LOGIC_VECTOR(3DOWNTO0);--时十位

BEGIN

IFclr='0'THEN

bcd1nhsv:

="0000";

bcd10nhsv:

="0000";

ELSIFclkh'EVENTANDclkh='1'THEN

IFbcd1nhsv=9THEN

bcd10nhsv:

=bcd10nhsv+1;

bcd1nhsv:

="0000";

ELSE

bcd1nhsv:

=bcd1nhsv+1;

ENDIF;

IFbcd10nhsv=2ANDbcd1nhsv=4THEN

bcd10nhsv:

="0000";--24时即为0时

bcd1nhsv:

="0000";

ENDIF;

ENDIF;

bcd1nhs<=bcd1nhsv;

bcd10nhs<=bcd10nhsv;

ENDPROCESS;

--clkadj:

PROCESS(cclk)--计时/调时选择信号处理

--BEGIN

--IF(cclk'EVENTANDcclk='1')THEN

--clockadjq<=clockadj;

--ENDIF;

--ENDPROCESS;

minhrs:

PROCESS(xclk)--时分设置信号进程

BEGIN

IF(xclk'EVENTANDxclk='1')THEN

minsetq<=NOTminset;--信号反向是因为实验台上

ENDIF;--自复按键的节点的输出常

IF(xclk'EVENTANDxclk='1')THEN--态为高电平,而按下后的

hoursetq<=NOThourset;--输出状态为低电平。

ENDIF;

ENDPROCESS;

disbhp:

PROCESS(xclk)--显示进程

BEGIN

IFclr='0'THEN

gscnt<="0000";

ELSIF(xclk'EVENTANDxclk='1')THEN

gscnt<=gscnt+1;

IFgscnt="0111"THEN

gscnt<="0000";

ENDIF;

ENDIF;

CASEgscntIS

WHEN"0000"=>gsel<="00000001";--显示秒个位

smhdis<=bcd1ns;

WHEN"0001"=>gsel<="00000010";--显示秒十位

smhdis<=bcd10ns;

WHEN"0010"=>gsel<="00000100";--显示“-”

smhdis<="1111";

WHEN"0011"=>gsel<="00001000";--显示分个位

smhdis<=bcd1nms;

WHEN"0100"=>gsel<="00010000";--显示分十位

smhdis<=bcd10nms;

WHEN"0101"=>gsel<="00100000";--显示“-”

smhdis<="1111";

WHEN"0110"=>gsel<="01000000";--显示时个位

smhdis<=bcd1nhs;

WHENOTHERS=>gsel<="";--显示时十位

smhdis<=bcd10nhs;

ENDCASE;

CASEsmhdisIS

WHEN"0000"=>bihuaag<="1111110";--"0"

WHEN"0001"=>bihuaag<="0110000";--'1"

WHEN"0010"=>bihuaag<="1101101";--"2"

WHEN"0011"=>bihuaag<="1111001";--"3"

WHEN"0100"=>bihuaag<="0110011";--"4"

WHEN"0101"=>bihuaag<="1011011";--"5"

WHEN"0110"=>bihuaag<="1011111";--"6"

WHEN"0111"=>bihuaag<="1110000";--"7"

WHEN"1000"=>bihuaag<="1111111";--"8"

WHEN"1001"=>bihuaag<="1111011";--"9"

WHENOTHERS=>bihuaag<="0000001";--"-"

ENDCASE;

ENDPROCESS;

ENDrtl;

实验心得

通过实验,逐渐的了解了VHDL在实际设计及应用中的使用,并掌握了VHDL编译软件的使用,同时也了解了硬件设计的方式方法,掌握了系统设计的思路。

但是在实验过程中,VHDL编译软件的使用较平时接触的软件复杂,虽然进行了课程设计,但是仍然不是很熟悉,在实验过程中总是需要按照实验书指导,才能顺利的对实验书进行处理。

但是尽管如此,在实验过程中,由于在端口设置过程中,未能处理妥当,仍然还是导致了烧入程序的失败!

在数字时钟的设计过程中,源程序的编写存在很大的难度,虽然先前就通过网络及图书馆进行了相关资料的查询,准备了相关的资料。

但是在理论与时间之间还是难以进行转换,难以独立编写代码。

最终参考老师及网络资料,随得到了代码,但是也是勉强看懂。

如果需要自己编写,对于端口等仍存在很大难度!

!

!

此文档是由网络收集并进行重新排版整理.word可编辑版本!