数电课后答案康华光第五版完整.docx

《数电课后答案康华光第五版完整.docx》由会员分享,可在线阅读,更多相关《数电课后答案康华光第五版完整.docx(41页珍藏版)》请在冰豆网上搜索。

数电课后答案康华光第五版完整

第一章数字逻辑习题

1.1数字电路与数字信号

1.1.2图形代表的二进制数

0

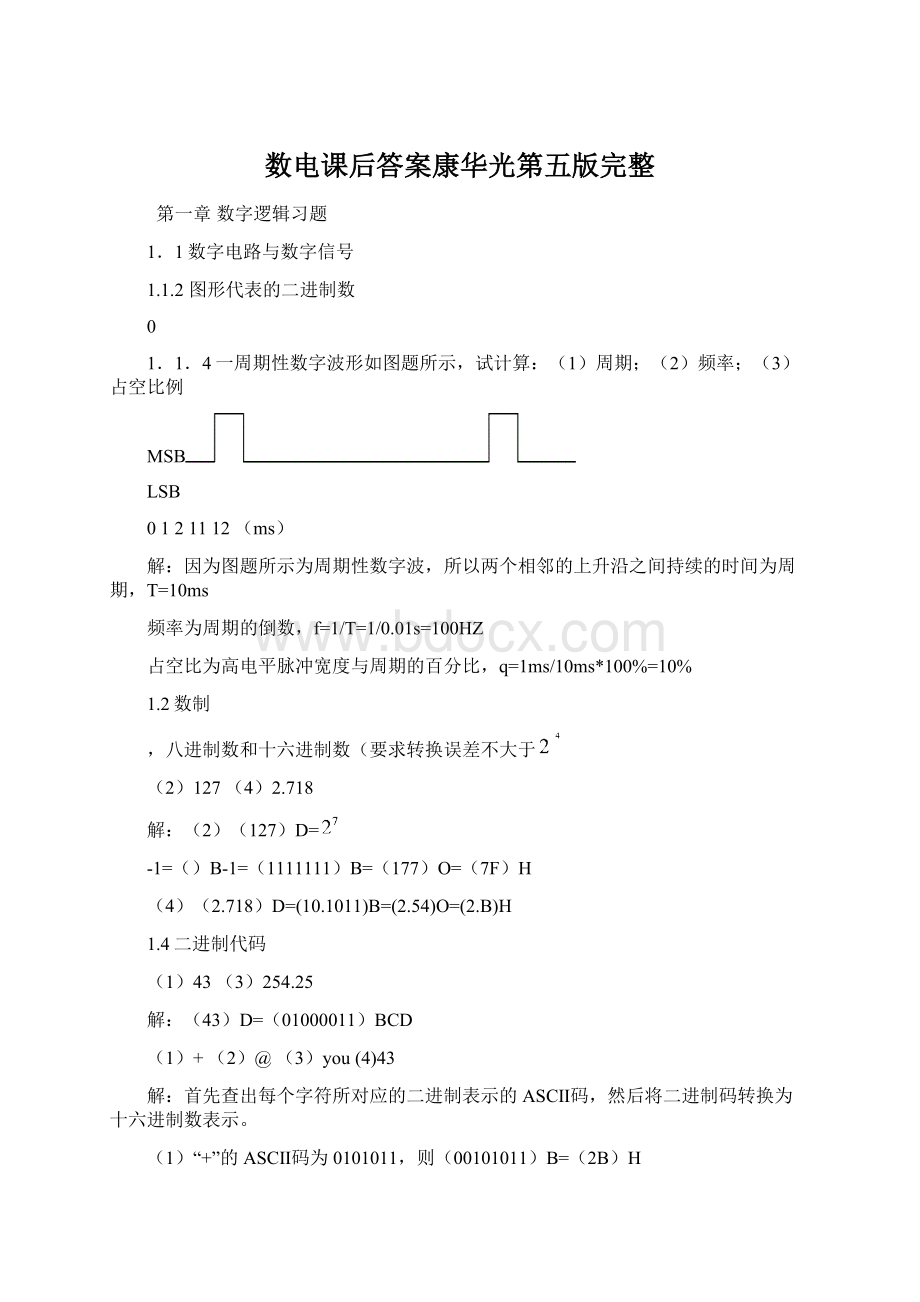

1.1.4一周期性数字波形如图题所示,试计算:

(1)周期;

(2)频率;(3)占空比例

MSB

LSB

0121112(ms)

解:

因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms

频率为周期的倒数,f=1/T=1/0.01s=100HZ

占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%

1.2数制

,八进制数和十六进制数(要求转换误差不大于

(2)127(4)2.718

解:

(2)(127)D=

-1=()B-1=(1111111)B=(177)O=(7F)H

(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H

1.4二进制代码

(1)43(3)254.25

解:

(43)D=(01000011)BCD

(1)+

(2)@(3)you(4)43

解:

首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H

(2)@的ASCⅡ码为1000000,(01000000)B=(40)H

(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75

(4)43的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,33

1.6逻辑函数及其表示方法

6.1中,已知输入信号A,B`的波形,画出各门电路输出L的波形。

解:

(a)为与非,(b)为同或非,即异或

第二章逻辑代数习题解答

2.1.1用真值表证明下列恒等式

(3)

(A⊕B)=AB+AB

解:

真值表如下

A

B

AB

+AB

0

0

0

1

0

1

1

0

1

1

0

0

0

0

1

0

1

0

0

0

0

1

1

0

0

1

1

1

由最右边2栏可知,

与

+AB的真值表完全相同。

2.1.3用逻辑代数定律证明下列等式

(3)

解:

2.1.4用代数法化简下列各式

(3)

解:

(6)

解:

(9)

解:

2.1.7画出实现下列逻辑表达式的逻辑电路图,限使用非门和二输入与非门

(1)

(2)

(3)

2.2.2已知函数L(A,B,C,D)的卡诺图如图所示,试写出函数L的最简与或表达式

解:

2.2.3用卡诺图化简下列个式

(1)

解:

(6)

解:

(7)

解:

2.2.4已知逻辑函数

,试用真值表,卡诺图和逻辑图(限用非门和与非门)表示

解:

1>由逻辑函数写出真值表

A

B

C

L

0

0

0

0

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

0

2>由真值表画出卡诺图

3>由卡诺图,得逻辑表达式

用摩根定理将与或化为与非表达式

4>由已知函数的与非-与非表达式画出逻辑图

第三章习题

3.1MOS逻辑门电路

,试选择一种最合适工作在高噪声环境下的门电路。

表题3.1.1逻辑门电路的技术参数表

VOL(max)/V

逻辑门A

2.4

0.4

2

0.8

逻辑门B

3.5

0.2

2.5

0.6

逻辑门C

4.2

0.2

3.2

0.8

解:

根据表题,以及式(,计算出逻辑门A的高电平和低电平噪声容限分别为:

=

—

=2.4V—2V=0.4V

=

—

=0.8V—0.4V=0.4V

同理分别求出逻辑门B和C的噪声容限分别为:

=1V

=0.4V

=1V

=0.6V

电路的噪声容限愈大,其抗干扰能力愈强,综合考虑选择逻辑门C

计算出它们的延时-功耗积,并确定哪一种逻辑门性能最好

表题3.1.3逻辑门电路的技术参数表

逻辑门A

1

1.2

16

逻辑门B

5

6

8

逻辑门C

10

10

1

解:

延时-功耗积为传输延长时间与功耗的乘积,即

DP=tpdPD

根据上式可以计算出各逻辑门的延时-功耗分别为

=

=

*16mw=17.6*

J=17.6PJ

同理得出:

=44PJ

=10PJ,逻辑门的DP值愈小,表明它的特性愈好,所以逻辑门C的性能最好.

3.1.5为什么说74HC系列CMOS与非门在+5V电源工作时,输入端在以下四种接法下都属于逻辑0:

(1)输入端接地;

(2)输入端接低于1.5V的电源;(3)输入端接同类与非门的输出低电压0.1V;(4)输入端接10kΩ的电阻到地.

解:

对于74HC系列CMOS门电路来说,输出和输入低电平的标准电压值为:

=0.1V,

=1.5V,因此有:

(1)

=0<

=1.5V,属于逻辑门0

(2)

<1.5V=

属于逻辑门0

(3)

<0.1<

=1.5V,属于逻辑门0

(4)由于CMOS管的栅极电流非常小,通常小于1uA,在10kΩ电阻上产生的压降小于10mV即

<0.01V<

=1.5V,故亦属于逻辑0.

解:

图解

L2=

L3=

L4实现与功能,即L4=L1

L2

L3,而L=

所以输出逻辑表达式为L=

3.1.9图题,图中n个三态门的输出接到数据传输总线,D1,D2,……Dn为数据输入端,CS1,CS2……CSn为片选信号输入端.试问:

(1)CS信号如何进行控制,以便数据D1,D2,……Dn通过该总线进行正常传输;

(2)CS信号能否有两个或两个以上同时有效?

如果出现两个或两个以上有效,可能发生什么情况?

(3)如果所有CS信号均无效,总线处在什么状态?

解:

(1)根据图解,片选信号CS1,CS2……CSn为高电平有效,当CSi=1时第i个三态门被选中,其输入数据被送到数据传输总线上,根据数据传输的速度,分时地给CS1,CS2……CSn端以正脉冲信号,使其相应的三态门的输出数据能分时地到达总线上.

(2)CS信号不能有两个或两个以上同时有效,否则两个不同的信号将在总线上发生冲突,即总线不能同时既为0又为1.

(3)如果所有CS信号均无效,总线处于高阻状态.

试分析,说明它们的逻辑功能

(A)(B)

(C)(D)

解:

对于图题,当

=0时,

和

均导通,

和

构成的反相器正常工作,L=

,当

=1时,

和

均截止,无论A为高电平还是低电平,输出端均为高阻状态,其真值表如表题解,该电路是低电平使能三态非门,其表示符号如图题解

图题,

=0时,

导通,或非门打开,

和

构成反相器正常工作,L=A;当

=1时,

截止,或非门输出低电平,使

截止,输出端处于高阻状态,该电路是低电平使能三态缓冲器,其表示符号如图题解

同理可以分析图题,它们分别为高电平使能三态缓冲器和低电平使能三态非门,其表示符号分别如图题

A

L

0

0

1

0

1

0

1

0

高阻

1

1

A

L

0

0

0

0

1

1

1

0

高阻

1

1

高阻

EN

A

L

0

0

高阻

0

1

高阻

1

0

0

1

1

1

A

L

0

0

1

0

1

0

1

0

高阻

1

1

高阻

3.2.2为什么说TTL与非门的输入端在以下四种接法下,都属于逻辑1:

(1)输入端悬空;

(2)输入端接高于2V的电源;(3)输入端接同类与非门的输出高电压3.6V;(4)输入端接10kΩ的电阻到地。

解:

(1)参见教材图,当输入端悬空时,T1管的集电结处于正偏,Vcc作用于T1的集电结和T2,T3管的发射结,使T2,T3饱和,使T2管的集电极电位Vc2=VcEs2+VBE3=0.2+0.7=0.9V,而T4管若要导通VB2=Vc2≥VBE4+VD=0.7+0.7=1.4V,故T4

截止。

又因T3饱和导通,故与非门输出为低电平,由上分析,与非门输入悬空时相当于输入逻辑1。

(2)当与非门输入端接高于2V的电源时,若T1管的发射结导通,则VBE1≥0.5V,T1管的基极电位VB≥2+C1=2.5V。

而VB1≥2.1V时,将会使T1的集电结处于正偏,T2,T3处于饱和状态,使T4截止,与非门输出为低电平。

故与非门输出端接高于2V的电源时,相当于输入逻辑1。

(3)与非门的输入端接同类与非门的输出高电平3.6V输出时,若T1管导通,则VB1=3.6+0.5=4.1。

而若VB1>2.1V时,将使T1的集电结正偏,T2,T3处于饱和状态,这时VB1被钳位在2.4V,即T1的发射结不可能处于导通状态,而是处于反偏截止。

由

(1)

(2),当VB1≥2.1V,与非门输出为低电平。

(4)与非门输入端接10kΩ的电阻到地时,教材图

,则VBI=3.07+VBE=3.07+0.5=3.57V。

但VBI是个不可能大于2.1V的。

当VBI=2.1V时,将使

T1管的集电结正偏,T2,T3处于饱和,使VBI被钳位在2.1V,因此,当RI=10kΩ时,T1将处于截止状态,由

(1)这时相当于输入端输入高电平。

3.2.3设有一个74LS04反相器驱动两个74ALS04反相器和四个74LS04反相器。

(1)问驱动门是否超载?

(2)若超载,试提出一改进方案;若未超载,问还可增加几个74LS04门?

解:

(1)根据题意,74LS04为驱动门,同时它有时负载门,负载门中还有74LS04。

从主教材附录A查出74LS04和74ALS04的参数如下(不考虑符号)

74LS04:

=8mA,

=0.4mA;

=0.02mA.

4个74LS04的输入电流为:

4

=4

0.4mA=1.6mA,

4

=4

0.02mA=0.08mA

2个74ALS04的输入电流为:

2

=2

0.1mA=0.2mA,

2

=2

0.02mA=0.04mA。

1拉电流负载情况下如图题解,74LS04总的拉电流为两部分,即4个74ALS04的高电平输入电流的最大值4

=0.08mA电流之和为0.08mA+0.04mA=0.12mA.而74LS04能提供0.4mA的拉电流,并不超载。

2灌电流负载情况如图题解,驱动门的总灌电流为1.6mA+0.2mA=1.8mA.

而74LS04能提供8mA的灌电流,也未超载。

(2)从上面分析计算可知,74LS04所驱动的两类负载无论书灌电流还是拉电流均未超

3.2.4图题,已知OC门输管截止时的漏电流=0.2mA;负载门的参数为:

=4V,=1V,==1A试计算上拉电阻的值。

从主教材附录A查得74LS03的参数为:

=2.7V,

=0.5V,

=8mA.根据式(,74LS03输出为低电平,

=5

=5

0.001mA=0.005mA,有

=

=

0.56K

拉电流