海思芯片ESDLatchup 测试技术规范V13.docx

《海思芯片ESDLatchup 测试技术规范V13.docx》由会员分享,可在线阅读,更多相关《海思芯片ESDLatchup 测试技术规范V13.docx(34页珍藏版)》请在冰豆网上搜索。

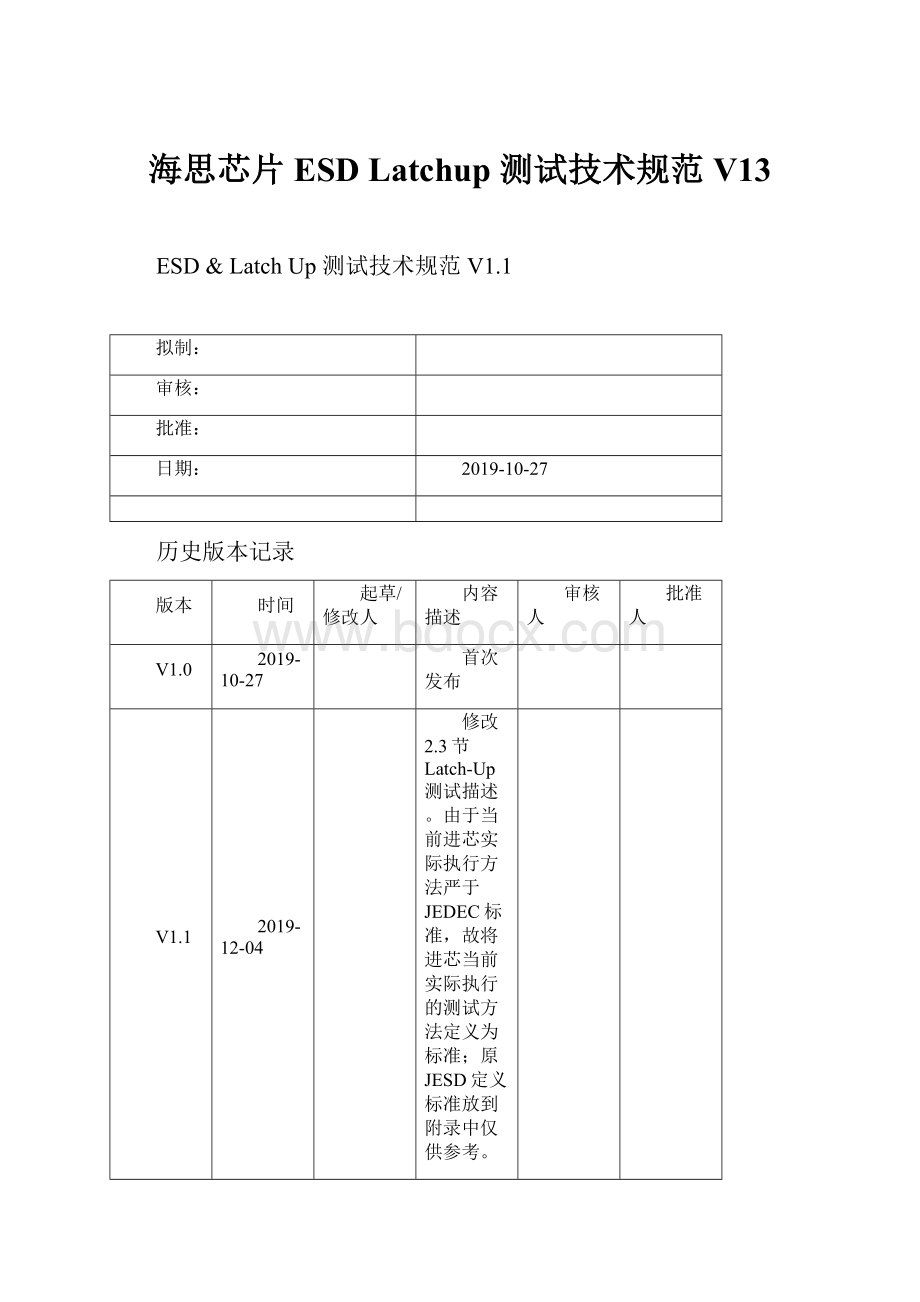

海思芯片ESDLatchup测试技术规范V13

ESD&LatchUp测试技术规范V1.1

拟制:

审核:

批准:

日期:

2019-10-27

历史版本记录

版本

时间

起草/修改人

内容描述

审核人

批准人

V1.0

2019-10-27

首次发布

V1.1

2019-12-04

修改2.3节Latch-Up测试描述。

由于当前进芯实际执行方法严于JEDEC标准,故将进芯当前实际执行的测试方法定义为标准;原JESD定义标准放到附录中仅供参考。

V1.3

2020-01-02

ESD-HBM测试方法由3种删减为2种。

不再介绍其中一种稍显复杂的测试方法,而是介绍测试厂用的比较多的方法

适用范围:

本规范规定了ESD&LatchUp测试的具体流程以及相关技术标准,适用于量产的项目芯片的ESD&LatchUp评估。

简介:

ESD测试主要用于评估芯片的抗ESD电压水平。

抗ESD电压低的芯片容易在生产、运输、安装的过程中,出现大量芯片的失效。

LatchUp测试主要用于评估芯片的抗闩锁能力。

抗闩锁能力低的芯片在应用过程中,输入电流或者电压的波动很容易造成芯片内部出现闩锁失效。

ESD&LatchUp测试是芯片量产前的关键测试,是判断芯片能否量产的主要判据。

引用文件:

下列文件中的条款通过本规范的引用而成为本规范的条款。

凡是注日期的引用文件,其随后所有的修改单(不包括勘误的内容)或修订版均不适用于本规范,然而,鼓励根据本规范达成协议的各方研究是否可使用这些文件的最新版本。

凡是不注日期的引用文件,其最新版本适用于本规范。

序号

参考标准

说明

1

JESD78E

Latch-Up标准

2

JS-001-2017

ESD-HBM标准

3

JS-002-2018

ESD-CDM标准

1.ESD&LatchUp测试流程

1.1ESD&LatchUp测试概要

ESD&LatchUp主要用于测试芯片的ESD&LatchUp的水平,需要项目SE、后端设计工程师、封装工程师、可靠性测试工程师共同参与,主要工作包括:

ESD&LatchUp测试方案确定、ESD&LatchUp测试流程执行、测试结果分析及出现失效后的问题定位和解决方案的确定。

1.2ESD&LatchUp测试流程

ESD-HBM模拟人体静电释放的过程,测试模型和放电模型如下:

2.ESD-HBM测试方法

JEDEC标准介绍有三种ESD-HBM测试方法,测试供应商通常采用方法二。

具体测试激励的电压上限可能会因项目不同会有不同,故每个版本测试时都需跟研发确认激励的上限。

2.1方法一

方法二适用于IO与芯片内部电源域关系未知的ESD测试,优点是分组简便,缺点是测试量较方法一大,存在重复测试。

参考JS-001-2017:

AlternativeProcedureB(followingTable2B):

部分

2.1.1测试步骤

第1步.芯片管脚分类

(1)非连接管脚:

一般少见,如用来温度检测、内部电压监控的IO,ESD测试中全程悬浮处理;

(2)电源管脚:

所有的电源供电IO和地,如VDD、AVDD、VDDIO、DGND、VSS、AGND、VDD2等;

(3)非电源管脚:

除非连接IO、电源类IO以外的其他输入、输出、时钟、参考等IO(注意非电源类的具有内部耦合通路并且成对的IO需要额外的ESD测试,例如差分输入输出、XTALIN和XTALOUT、RF_IN和RF_OUT等,后面详解);

第2步.芯片管脚按电源域分组

(1)将电源管脚按电源域分组,例如AVP32F335芯片可以分为VDD(数字)、VDDIO(IO)、VDDIOPR(IO)、VDD1A33(模拟端口电源)、VDDA2(ADC模拟电源引脚)、VDDAIO(ADC模拟IO电源引脚)、VDD1A18、VDD2A18共8个电源域;

(2)根据电源域和功能的划分,将非电源管脚归类到第

(1)步的电源域分组中;例如ADC输入、参考等相关的管脚归类的相关的模拟电源域分组中;而数字IO既要归类到VDD中,又要归类到VDDIO电源域中;

第3步.按分组进行测试

激励测试1:

电源管脚对电源管脚激励测试

挑选3样本,将电源域组内(如VDD电源域组)电源类管脚(如VDD)依次接到测试机台GND端,将其他电源类管脚(包括其他电源域的电源管脚,如VDDIO、VDD1A18等)依次接到测试机台激励端,施加正脉冲进行测试。

激励测试2:

非电源管脚对电源类管脚激励测试

挑选3样本,将电源域组内(如VDD电源域组)电源类管脚(如VDD)依次接到测试机台GND端,将所有其他非电源管脚依次接到测试机台激励端,施加正脉冲进行测试。

测负脉冲时,另取3样本,重复上述步骤;

激励测试3:

非电源管脚的激励测试

挑选3样本,将全部非电源管脚接到测试机台GND端,将施加激励的非电源管脚轮流接到测试机台激励端,施加正脉冲进行测试。

测负脉冲时,另取3样本,重复上述步骤;

流程图

2.1.2样本量及环境

3pcs/电源分组,分正负压测试;

温度:

室温(25℃±5℃)

湿度:

(55±10)%RH

2.1.3失效判据

电性能判据:

施加激励测试前后,需要对接地端、激励端的IO进行IV曲线测试,I/V曲线指示失效的判据是:

在ESD测试前后的I/V曲线漂移超过30%(1uA处的电压漂移)。

功能判据:

所有分组测试完成且IV测试pass,再统一经FT测试或功能测试确认功能是否OK。

2.1.4参考JS-001-2017示例

2.1.5AVP32F335测试举例

以AVP32F335芯片为例。

第一步.芯片管脚分类

A.非连接管脚(测试全程悬浮):

TEST1/VDD15CORE、TEST2/VSSCORE

B.电源管脚:

VDD1A33、VDDA2、VSSA2、VDDAIO、VSSAIO、VDD1A18、VSS1AGND、VDD2A18、VSS2AGND、VDD、VDDIO、VDDIOPR、VSS

C.非电源管脚:

JTAG相关、XCLKOUT、XCLKIN、X1、X2、XRS、ADCINAx、ADCINBx、ADCLO、ADCRESEXT、ADCREFIN、ADCREFP、ADCREFM、XDR、GPIOxx;注意其中XCLKIN与XCLKOUT为Couple管脚;

第二步.芯片管脚按电源域分组

电源域划分

第三步.按分组进行测试

电源域分组

样本量

(pcs)

接到测试机台GND端的Pin

接到测试机台激励端的Pin

(轮流施加脉冲并测试)

正脉冲激励总数

VDD

电源域

3

VDD

电源管脚

VSS、VDDIO、VDDIOPR、VDDAIO、VSSAIO、VSSA2、VSS1AGND、VSS2AGND、VDD1A18、VDD2A18、VDDA2、VDD1A33

非电源管脚

所有数字IO、模拟IO

VSS

电源管脚

VSS、VDDIO、VDDIOPR、VDDAIO、VSSAIO、VSSA2、VSS1AGND、VSS2AGND、VDD1A18、VDD2A18、VDDA2、VDD1A33

非电源管脚

所有数字IO、模拟IO

VDDIO

电源域

3

VDDIO

电源管脚

VSS、VDDIO、VDDIOPR、VDDAIO、VSSAIO、VSSA2、VSS1AGND、VSS2AGND、VDD1A18、VDD2A18、VDDA2、VDD1A33

非电源管脚

所有数字IO、模拟IO

VDDIOPR电源域

3

VDDIOPR

电源管脚

VSS、VDDIO、VDDIOPR、VDDAIO、VSSAIO、VSSA2、VSS1AGND、VSS2AGND、VDD1A18、VDD2A18、VDDA2、VDD1A33

非电源管脚

所有数字IO、模拟IO

VDDAIO

电源域

3

VDDAIO

电源管脚

VSS、VDDIO、VDDIOPR、VDDAIO、VSSAIO、VSSA2、VSS1AGND、VSS2AGND、VDD1A18、VDD2A18、VDDA2、VDD1A33

非电源管脚

所有数字IO、模拟IO

VSSAIO

电源管脚

VSS、VDDIO、VDDIOPR、VDDAIO、VSSAIO、VSSA2、VSS1AGND、VSS2AGND、VDD1A18、VDD2A18、VDDA2、VDD1A33

非电源管脚

所有数字IO、模拟IO

VDD1A18电源域

3

VDD1A18

电源管脚

VSS、VDDIO、VDDIOPR、VDDAIO、VSSAIO、VSSA2、VSS1AGND、VSS2AGND、VDD1A18、VDD2A18、VDDA2、VDD1A33

非电源管脚

所有数字IO、模拟IO

VSS1AGND

电源管脚

VSS、VDDIO、VDDIOPR、VDDAIO、VSSAIO、VSSA2、VSS1AGND、VSS2AGND、VDD1A18、VDD2A18、VDDA2、VDD1A33

非电源管脚

所有数字IO、模拟IO

VDD2A18电源域

3

VDD2A18

电源管脚

VSS、VDDIO、VDDIOPR、VDDAIO、VSSAIO、VSSA2、VSS1AGND、VSS2AGND、VDD1A18、VDD2A18、VDDA2、VDD1A33

非电源管脚

所有数字IO、模拟IO

VSS2AGND

电源管脚

VSS、VDDIO、VDDIOPR、VDDAIO、VSSAIO、VSSA2、VSS1AGND、VSS2AGND、VDD1A18、VDD2A18、VDDA2、VDD1A33

非电源管脚

所有数字IO、模拟IO

VDDA2

电源域

3

VDD2A

电源管脚

VSS、VDDIO、VDDIOPR、VDDAIO、VSSAIO、VSSA2、VSS1AGND、VSS2AGND、VDD1A18、VDD2A18、VDDA2、VDD1A33

非电源管脚

所有数字IO、模拟IO

VSSA2

电源管脚

VSS、VDDIO、VDDIOPR、VDDAIO、VSSAIO、VSSA2、VSS1AGND、VSS2AGND、VDD1A18、VDD2A18、VDDA2、VDD1A33

非电源管脚

所有数字IO、模拟IO

非电源管脚

3

所有数字IO、模拟IO(除测试激励IO)

非电源管脚

所有数字IO、模拟IO其中之一

轮流施加激励

2.2方法二

方法三操作最简便,但是激励数较多,工作量较方法一、二有增加,但是无需测试人源熟悉芯片电源域的划分,可以理解为“傻瓜式”测试方法。

测试供应商通常采用该方法;

2.2.1参考JS-001-2017示例

2.2.2AVP32F335测试举例

电源域分组

样本量

(pcs)

接到测试机台GND端的Pin

接到测试机台激励端的Pin

(轮流施加脉冲并测试)

正脉冲激励总数

VDD

电源域

3

VDD

电源管脚

所有电源管脚

非电源管脚

所有数字IO、模拟IO

VSS

电源管脚

所有电源管脚

非电源管脚

所有数字IO、模拟IO

VDDIO

电源域

3

VDDIO

电源管脚

所有电源管脚

非电源管脚

所有数字IO、模拟IO

VDDIOPR电源域

3

VDDIOPR

电源管脚

所有电源管脚

非电源管脚

所有数字IO、模拟IO

VDDAIO

电源域

3

VDDAIO

电源管脚

所有电源管脚

非电源管脚

所有数字IO、模拟IO

VSSAIO

电源管脚

所有电源管脚

非电源管脚

所有数字IO、模拟IO

VDD1A18电源域

3

VDD1A18

电源管脚

所有电源管脚

非电源管脚

所有数字IO、模拟IO

VSS1AGND

电源管脚

所有电源管脚

非电源管脚

所有数字IO、模拟IO

VDD2A18电源域

3

VDD2A18

电源管脚

所有电源管脚

非电源管脚

所有数字IO、模拟IO

VSS2AGND

电源管脚

所有电源管脚

非电源管脚

所有数字IO、模拟IO

VDDA2

电源域

3

VDD2A18

电源管脚

所有电源管脚

非电源管脚

所有数字IO、模拟IO

VSS2A

电源管脚

所有电源管脚

非电源管脚

所有数字IO、模拟IO

非电源管脚

3

所有数字IO、模拟IO(除测试激励IO)

非电源管脚

所有数字IO、模拟IO轮流施加激励

(测试激励IO)

3.CDM测试方法

具体测试激励的电压上限可能会因项目不同会有不同,故每个版本测试时都需跟研发确认激励的上限。

ESD-CDM模拟器件本身带电后的静电释放过程。

其放电时间更短,放电现象更难模拟。

2.2.1测试步骤

2.2.1.1标准步骤(参考JS-002-2018)

2.2.1.2简便步骤

对于ESD-CDM的测试,每个测试电压一共需要六颗芯片,3颗测试正电压,3颗测试负电压。

2.2.2样本量及环境

6pcs,正负压测试各3pcs

温度:

室温(25℃±5℃)

湿度:

≤30%RH

2.2.3失效判据

电性能判据:

施加激励测试前后,需要对接地端、激励端的IO进行IV曲线测试,I/V曲线失效的判据是:

在ESD测试前后的I/V曲线漂移超过30%(1uA处的电压漂移)。

功能判据:

所有分组测试完成且IV测试pass,再统一经FT测试或功能测试确认功能是否OK。

4.Latch-Up测试方法

4.1JEDEC标准流程

4.2详细步骤

4.2.1测试步骤(I-Test)

I-Test针对所有输入IO进行测试。

Ø第1步(+I-Test)

所有输入、双向(输入或高阻状态)管脚接逻辑高电平的最大值(MaxLogicHigh),输出管脚悬空;所有电源管脚接最大输入电压(Maximumoperatingvoltage)。

Ø第2步

待测管脚接逻辑高电平(此时电流为I1),测试此时所有电源管脚的Isupply(Inormal)并记录。

Ø第3步

施加测试电流脉冲,激励强度+100mA(此时电流为I1+100mA,参考2.2.1节Table-1)

Ø第4步

待激励移除后,测试此时电源管脚的电流Isupply,对比第2步记录的Inormal,如果此时任意的Isupply大于2.2.4所列失效条件(同2.2.1节Table-2),则判断产生Latch-Up失效。

Ø第5步

如没有Latch-Up失效产生,则重复第2~第4步,完成所有输入管脚的测试。

Ø第6步

将所有输入、双向(输入或高阻状态)管脚改接逻辑低平的最小值(MinLogicLow),重复第2~第5步。

Ø第7步(-I-Test)

所有输入、双向(输入或高阻状态)管脚接逻辑高电平的最大值(MaxLogicHigh),输出管脚悬空;所有电源管脚接最大输入电压(Maximumoperatingvoltage)。

Ø第8步

待测管脚接逻辑低电平(此时电流为I2),测试此时所有电源管脚的Isupply(Inormal)并记录。

Ø第9步

施加测试电流脉冲,激励强度-100mA(此时绝对值为I2-100mA,参考2.2.1节Table-1)

Ø第10步

待激励移除后,测试此时电源管脚的电流Isupply,对比第8步记录的Inormal,如果此时任意的Isupply大于2.2.4所列失效条件(同2.2.1节Table-2),则判断产生Latch-Up失效。

Ø第11步

没有Latch-Up失效产生,则重复第8~第10步,完成所有输入管脚的测试。

Ø第12步

将所有输入、双向(输入或高阻状态)管脚改接逻辑低平的最小值(MinLogicLow),重复第8~第11步。

+I-Test激励波形图

-I-Test激励波形图

4.2.2测试步骤(V-Test)

V-Test针对所有电源IO进行测试。

Ø第1步

所有输入、双向(输入或高阻状态)管脚接逻辑高电平的最大值(MaxLogicHigh),输出管脚悬空;所有电源管脚接最大输入电压(Maximumoperatingvoltage),测试此时所有电源管脚的Isupply(Inormal)并记录。

Ø第2步

对待测电源管脚(组)施加测试脉冲,激励强度1.5xVddmax或MSV中的较小值。

(参考2.2.1节Table-1)

Ø第3步

待激励移除后,测试此时所有电源管脚的电流Isupply,与第1部中的Inormal对比,如果此时任意的Isupply大于2.2.4所列失效条件(同2.2.1节Table-2),则判断产生Latch-Up失效。

Ø第4步

如没有Latch-Up失效产生,则重复第2~第3步,完成所有电源管脚的测试。

V-Test激励波形图

4.2.3详细测试表格9

测试

类型

测试

管脚

激励极性

untested输入

管脚状态

输出管脚

Vsupply电源

电压5

Test管脚激励条件

失效判据

I-Test

非电源IO

正

逻辑高电平最大值

悬空

最大额定电压

Trigger:

I+100mA

钳位电压:

+1.5xVmax或+MSV中的较小值1,2,7

如果Inormal≤25mA,判据Inormal+10mA

如果Inormal>25mA,判据1.4*Inormal6,7,8

逻辑低电平最小值

负

逻辑高电平最大值

Trigger:

I-100mA

钳位电压:

|-0.5xVmax|或|-MSV|中的较大值1,2,7

逻辑低电平最小值

V-Test

电源IO5,10

正

逻辑高电平最大值

Trigger:

1.5xVddmax或MSV中的小值2,3,8

钳位电流:

Inormal+100mA或1.5xInormal中的较大值4

逻辑低电平最小值

注1:

Vmax是指逻辑高电平的最大值

注2:

MSV(maximumstressvoltage),非datasheet中额定电压最大值,跟芯片制造工艺和电路拓扑结构相关,是指管脚可承受而又不造成不可逆损坏的最大电压(例如TIDSPdatasheet“AbsoluteMaximumRatings”)。

注3:

这里的Vddmax注意有是数字、IO等电源,注意是额定最大值(习惯用Vddmax测试,与原始标准有不同)。

以进芯AVP32F335为例,“6.2建议的运行条件”VDDIOmax=3.465V,“6.1最大绝对额定值(MSV)”VINmax=4.6V,由于1.5*VDDIOmax>VINmax,故trigger大小应以MSV(VINmax)为参考。

注4:

Inormal指各Inormal的和,因为电源一般有多个管脚引出。

注5:

由于Latch-up容易发生在IO管脚,偶尔发生在芯片内部,故Latch-up测试以IO电源域为主要关注点。

注6:

注意判据是以各个电源的Inormal独立判定,任意一个判定超标则测试fail。

注7:

trigger=±100mA的有可能因钳位电压限制而达不到设定的幅度,实际施加的幅度<±100mA,如果此时没有产生latch-up失效,则认为该管脚的latch-up测试pass。

注8:

trigger=1.5xVddmax的有可能因钳位电流限制而达不到设定的幅度,实际施加的幅度<1.5xVddmax,如果此时没有产生latch-up失效,则认为该管脚的latch-up测试pass。

注9:

测试机台供电电流有限流设置,如果测试中出现限流,则测试结果有可能是错误的,需要增大限流值。

注10:

某些时钟类、特定状态的IO不需要测试,参考《JESD78E》AnnexA部分。

4.2.4样本量及环境

9pcs(+I-Test3pcs,-I-Test3pcs,V-Test3pcs);

温度:

85℃±5℃(CLASSII,按Datasheet最高环境温度测试)

湿度:

(55±10)%RH

4.2.5失效判据

电性能判据:

如果Inormal≤25mA,判据Inormal+10mA

如果Inormal>25mA,判据1.4*Inormal

功能判据:

FT回测pass,功能复测pass。