数字信号处理器tms320lf2407.docx

《数字信号处理器tms320lf2407.docx》由会员分享,可在线阅读,更多相关《数字信号处理器tms320lf2407.docx(19页珍藏版)》请在冰豆网上搜索。

数字信号处理器tms320lf2407

数字信号控制器TMS320LF2407

DSP芯片,也称数字信号控制器,是一种具有特殊结构的微处理器。

DSP芯片内部采用程序和数据分开的哈佛结构,具有专门的硬件乘法器,广泛采用流水线操作,提供特殊的DSP指令,可以快速实现各种数字信号处理算法。

TMS320LF2407芯片是TI公司TMS320系列中的一种16位定点DSP芯片,是目前应用最为广泛的芯片。

基于TMS320C2xxDSP的CPU核结构设计提供了低成本、低功耗、高性能的处理能力,对电机的数字化控制非常有用。

同时,几种先进的外设被集成到该芯片内,形成了真正意义上的数字控制器。

∙2407的基本特点和资源配置

LF2407DSP具有TMS320系列DSP的基本功能之外,还有其自身特点:

∙采用高性能静态CMOS技术,使得供电电压降为3.3V,减小了控制器的功率损耗;30MIPS的执行速度是的指令周期缩短到33ns(30MHZ),从而提高控制器的实时控制能力;

∙基于TMS320C2XXDSP的CPU内核保证了TMS320LF2407DSP代码和TMS320系列DSP代码兼容;

∙片内有高达32K字×16位的Flash程序存储器;高达2.5K×16位的数据/程序RAM;2K字的单口RAM;

∙SPI/SCI引导ROM;

∙两个事件管理模块EVA和EVB,每个均包括如下资源:

两个16位通用定时器;8个16位的脉宽调制通道(PWM),可以实现三相反相器控制、PWM的中心或边缘校正、当外部引脚\PDPINTX出现低电平时快速关闭PWM通道;防止击穿故障的可编程的PWM死去控制;对外部事件进行定时捕获的3个捕获单元;片内光电编码器接口电路;16通道的同步ADC转换器。

∙可扩展的外部存储器具有192K×16位空间,分别为64K字程序存储空间,64K字的数据存储空间和64K字的I/O存储空间;

∙看门狗(WD)定时器模块;

∙10位的ADC转换器,其特性为:

最小转换时间为500ns,16个多路复用的输入通道、可选择两个事件管理器来触发两个8通道输入ADC转换器或一个16通道输入的A/D转换器;

∙基于锁相环(PLL)的时钟发生器;

∙高达41个可单独编程或复用的通用输入输出引脚(GPIO);

∙5个外部中断(两个驱动保护、复位和两个可屏蔽中断);

∙电源管理,具有3种低功耗模式,能够独立的将外围器件转入低功耗工作模式;

∙数字和混合信号的外设

∙事件管理器;

∙CAN(ControllerAreaNetwork),即控制器区域网;

∙串行通信接口(SCI)和16位串行外部设备接口(SPI);

∙模数转换器(ADC);

∙系统保护,例如低电压保护和看门狗定时器。

∙DSP引脚功能介绍

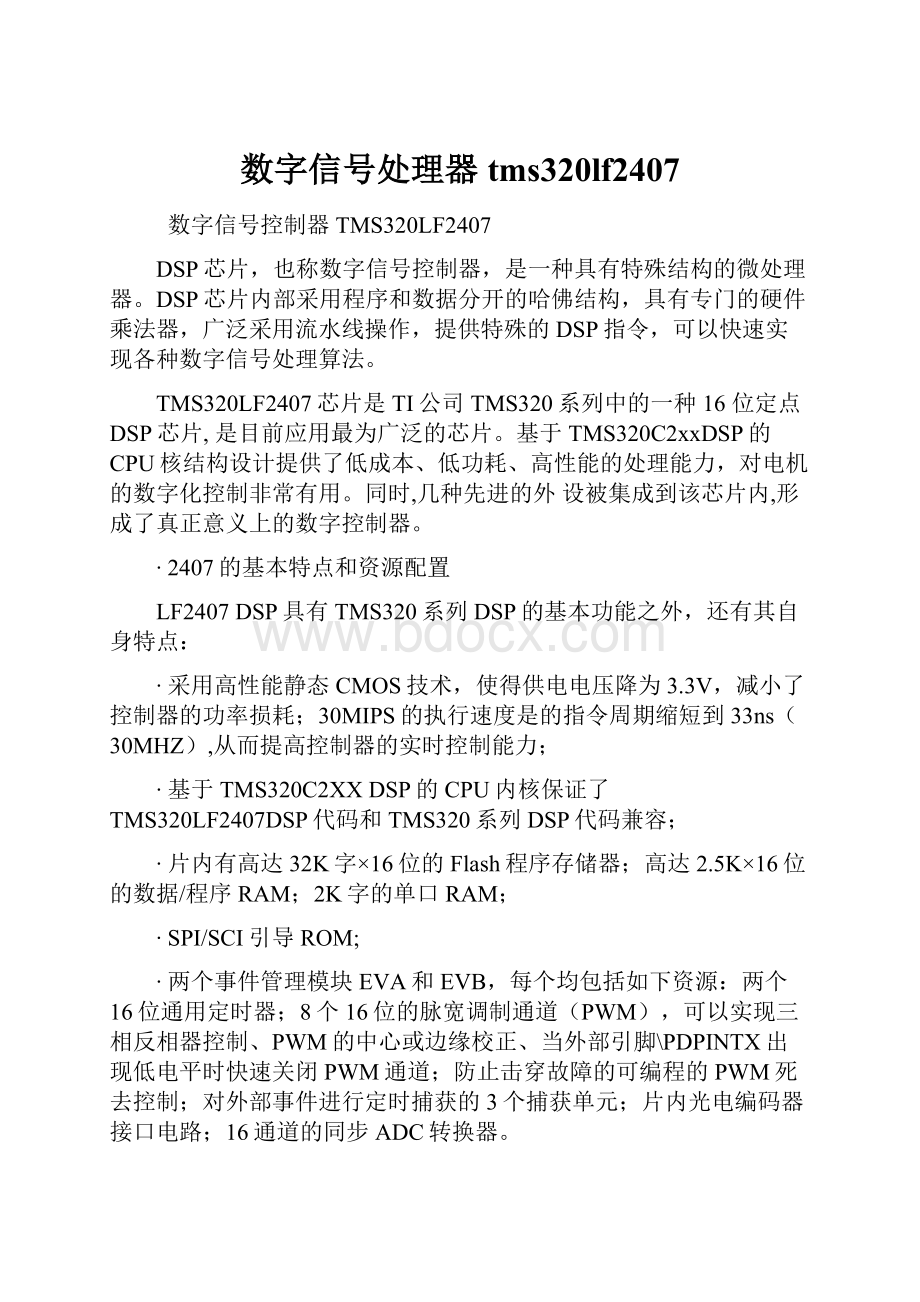

TMS320LF2407控制器具有144条引脚,如图1所示,其引脚功能如表1所示。

TMS320LF2407PEG

图1TMS320LF2407的引脚布置

表1

引脚号

引脚名

功能

事件管理器A(EVA)

83

CAP1/QEP1/IOPA3

捕获输入#1/正交编码脉冲输入#1(EVA)或通用I/O

79

CAP2/QEP2/IOPA4

捕获输入#2/正交编码脉冲输入#2(EVA)或通用I/O

75

CAP3/IOPA5

捕获输入#3(EVA)或通用I/O

56

PWM1/IOPA6

比较/PWM输出引线#(EVA)1或通用I/O

54

PWM2/IOPA7

比较/PWM输出引线#(EVA)2或通用I/O

52

PWM3/IOPB0

比较/PWM输出引线#(EVA)3或通用I/O

47

PWM4/IOPB1

比较/PWM输出引线#(EVA)4或通用I/O

44

PWM5/IOPB2

比较/PWM输出引线#(EVA)5或通用I/O

引脚号

引脚名

功能

40

PWM6/IOPB3

比较/PWM输出引线#(EVA)6或通用I/O

16

T1PWM/T1CMP/IOPB4

TMR1比较输出(EVA)或通用I/O

18

T2PWM/T2CMP/IOPB5

TMR2比较输出(EVA)或通用I/O

14

TDIRA/IOPB6

通用定时器计数方向选择(EVA)或通用I/O,若TDIRA=1则为加计数,否则为减计数

37

TCLKINA/IOPB7

通用定时器(EVA)外部时钟输入或通用I/O。

注意,

定时器也可以使用内部时钟。

事件管理器B(EVB)

88

CAP4/QEP3/IOPE7

捕获输入#4/正交编码脉冲输入#4(EVB)或通用I/O

81

CAP5/QEP4/IOPF0

捕获输入#5/正交编码脉冲输入#5(EVB)或通用I/O

69

CAP6/IOPF1

捕获输入#6(EVB)或通用I/O

65

PWM7/IOPE1

比较/PWM输出引脚#7(EVB)或通用I/O

62

PWM8/IOPE2

比较/PWM输出引脚#8(EVB)或通用I/O

59

PWM9/IOPE3

比较/PWM输出引脚#9(EVB)或通用I/O

55

PWM10/IOPE4

比较/PWM输出引脚#10(EVB)或通用I/O

46

PWM11/IOPE5

比较/PWM输出引脚#11(EVB)或通用I/O

38

PWM12/IOPE6

比较/PWM输出引脚#12(EVB)或通用I/O

8

T3PWM/T3CMP/IOPF2

TMR3比较输出(EVB)或通用I/O

6

T4PWM/T4CMP/IOPF3

TMR4比较输出(EVB)或通用I/O

2

TDIRB/IOPF4

通用定时器计数方向选择(EVB)或通用I/O

当TDIRA=1时,选择加计数,否则选择减计数

126

TCLKINB/IOPF5

通用定时器(EVB)外部时钟输入或通用I/O:

可用内部时钟

模数转换器(ADC)

112

ADCIN0

ADC的模拟输入#0

110

ADCIN1

ADC的模拟输入#1

107

ADCIN2

ADC的模拟输入#2

105

ADCIN3

ADC的模拟输入#3

103

ADCIN4

ADC的模拟输入#4

引脚号

引脚名

功能

102

ADCIN5

ADC的模拟输入#5

100

ADCIN6

ADC的模拟输入#6

99

ADCIN7

ADC的模拟输入#7

113

ADCIN8

ADC的模拟输入#8

111

ADCIN9

ADC的模拟输入#9

109

ADCIN10

ADC的模拟输入#10

108

ADCIN11

ADC的模拟输入#11

106

ADCIN12

ADC的模拟输入#12

104

ADCIN13

ADC的模拟输入#13

101

ADCIN14

ADC的模拟输入#14

98

ADCIN15

ADC的模拟输入#15

115

VREFHI

ADC模拟输入参考电压高电平输入端

114

VREFLO

ADC模拟输入参考电压低电平输入端

116

VCCA

ADC模拟供电电压(3.3V)

117

VSSA

ADC模拟地

CAN、串口通信(SCI)、串行外部设备接口(SPI)

70

CANRX/IOPC7

CAN接收数据脚或通用I/O脚

72

CANTX/IOPC6

CAN发送数据脚或通用I/O脚

25

SCITXD/IOPA0

SCI异步串行口发送数据引脚或通用I/O

26

SCIRXD/IOPA1

SCI异步串行口接收数据引脚或通用I/O

35

SPICLK/IOPC4

SPI时钟引脚或通用I/O

30

SPISIMO/IOPC2

SPI从动输入、主控输出或通用I/O引脚

32

SPISOMI/IOPC3

SPI从动输出、主控输入或通用I/O引脚

33

/IOPC5

SPI从动发送使能(可选)引脚或通用I/O

外部中断、时钟

133

复位引脚,当为高电平时,从程序存储器的0位址开始执行;

当WD定时器溢出时,在脚产生一个系统复位脉冲。

低电平时,导致240x终止执行,PC=1。

引脚号

引脚名

功能

7

功率驱动保护中断输入引脚,当电机驱动/电源逆变器不正常时,

如出现过压、过流时,该中断有效,PWM脚(EVA)置为高阻态。

是一个下降沿敏感的中断。

23

XINT1/IOPA2

外中断或通用I/O

21

XINT2/ADCSOC/IOPD0

外部用中断2可做AD转换开始输入引脚或通用I/O。

XINT1/2都是边沿有效、边沿极性可编程。

73

CLKOUT/IOPE0

时钟输出或通用I/O脚.输出时钟为CPU时钟或监察定时器时钟,

这由系统控制状态寄存器中CLKSRC决定。

当不作为时钟输出,

可以用作通用I/O。

137

功率驱动保护中断输入引脚,当电机驱动/电源逆变器不正常时,

如出现过压、过流时,该中断有效,PWM脚(EVA)置为高阻态。

是一个下降沿敏感的中断。

振荡器、锁相环(PLL)、FLASH、引导和其他

123

XTAL1/CLKIN

PLL振荡器输入引脚。

晶体振荡器或时钟源输入到PLL时,

该引脚接到参考晶体振荡器的一端。

124

XTAL2

晶体振荡器、PLL振荡器输出引脚。

该引脚接到参考晶体振荡器的一端,

当EMU1/是低电平时,该引脚为高阻态。

12

PLLVCCA

PLL电压(3.3V)

131

IOPF6

通用I/O引脚

121

/XF

引导ROM使能,通用I\O、XF引脚,该引脚在复位期间被输入采样,

以更新SCSR2.3,,然后驱动XF作为输出信号。

复位之后,XF被置高电平

,只能接无源回路。

11

PLLF

PLL外接滤波器输入1

10

PLLF2

PLL外接滤波器输入2

58

VCCP(5V)

FLASH编程电压输入引脚。

在硬件仿真时,

该引脚必须为个5V。

在程序下载时,该引脚可以为5V或0V。

运行时,该引脚必须接地,在该引脚上,不要使用任何限流电阻。

引脚号

引脚名

功能

60

TP1

FLASH阵列测试引脚,悬空。

63

TP2

FLASH阵列测试引脚,悬空。

119

/IOPC1

分支控制输入引脚,BIO指令检测该引脚电平,若为低,则执行分支程序;

若不用该引脚,则应该将其拉为高电平;所有控制器复位时,

将该位配置为分支控制输入,不用此功能时,该引脚可以作为I/O口

仿真和测试

90

EMU0

具有内部上拉的仿真器I/O的#0号引脚。

当引脚拉为高电平时,

该引脚用作指向来自仿真器系统的中断,通过JTAG扫描可定义为I/O引脚;

91

EMU1/

仿真器#1引脚,该引脚可禁用所有输出。

当引脚为高电平时,

该引脚用作来自或指向仿真器系统的中断,通过JTAG扫描可定

义为I/O引脚;当引脚拉为低电平时,该引脚设置为引脚,

当低电平有效时所有的输出引脚驱动为高阻态。

注意:

只用于测试和仿真(不用于多处理应用),因此对

于的状态有以下几种:

=0;EMU=0,EMU1/=0

135

TCK

带内部上拉的JTAG测试时钟

139

TDI

带内部上拉的JTAG测试数据输入。

在TCK的上升沿从TDI输入

的数据被锁存到选定的寄存器(指令或数据)

142

TDO

JTAG扫描输出,测试数据输出(TDO)。

在TCK下降沿,选定寄

存器中的内容(指令或数据)被移出到TDO引脚

144

TMS

带内部上拉的JTAG测试数据输入,在TCK的上升沿锁存到TAP控制器中。

36

TMS2

带内部上拉的JTAG测试方式选择2.该串行控制输入在TCK的

上升沿锁存到TAP控制器中,只用于测试盒仿真,在用户

应用中该引脚可以不接

引脚号

引脚名

功能

1

带内部下拉的JTAG测试复位。

当拉为高电平时,扫描系统

控制器运行,若该引脚未接或处于低电平时,控制器运行

在功能模式,并且测试复位信号无效。

地址、数据、存储器控制信号

87

数据空间选通引脚。

、和总保持为高电平,除非要用低电平

请求访问相关的外部存储器或I/O空间,在复位、掉电和EMU1

低电平有效时该引脚被置为高阻态。

82

I/O空间选通引脚。

、和总保持为高电平,除非要用低电平请

求访问相关的外部存储器或I/O空间,在复位、掉电和EMU1低

电平有效时该引脚被置为高阻态。

84

程序空间选通引脚。

、和总保持为高电平,除非要用低电平请

求访问相关的外部存储器或I/O空间,在复位、掉电和EMU1低电

平有效时该引脚被置为高阻态。

92

R/

读/写选通信号,通常为读方式(高电平),除非低电平请求执

行写操作,当EMU1/低电平有效和掉电时该引脚被置为高阻态。

19

W//IOPC0

写/读选通或通用I/O口,通常为低电平,除非在执行存储器写操

作时采薇高电平

89

写使能引脚,该信号下降沿表示控制器驱动外部数据线,对所有的

外部程序、数据和I/O接口有效:

当EMU1/低电平有效时,该引脚被置为高阻态。

96

外部存储器访问选项,该引脚一直为高电平,除非插入一个低电平

来表示一个外部总线周期:

在访问片外空间时该信号有效:

当EMU1/

低电平有效和掉电时该引脚被置为高阻态。

120

READY

访问外部设备时,该引脚被拉为低电平来增加等待状态,它表示一

个外部器件作为将要完成的总线处理的任务做好准备,若该外设没

有准备好,则将该引脚拉为低电平;

(此时,处理器将等待一个周期,并在此检测该引脚)。

引脚号

引脚名

功能

118

MP/

微处理器/微控制器方式选择引脚,复位时若该引脚为低电平,则

工作在为控制方式;若复位时该引脚为高电平,则工作在微处理器

方式,同时将MP/置位。

93

/RD

读使能信号对所有I/O有效,当EMU1/低电平有效时,该引脚置为高阻态。

122

ENA_144

高电平输入有效时使能外部接口信号,若为低电平没有外部存储器;

若DS为低电平则产生一个无效的地址,该引脚内部下拉。

97

可视输出使能(当数据总线输出有效时)。

在可视输出方式下,在

外部数据总线驱动为输出的任何时候该引脚有效(为低电平)。

当

运行在可视方式下,该引脚可用作外部编码逻辑,以防止数据总线冲突。

80

A0

16位地址总线第0位(bit0)

78

A1

16位地址总线第1位(bit0)

74

A2

16位地址总线第2位(bit0)

71

A3

16位地址总线第3位(bit0)

68

A4

16位地址总线第4位(bit0)

64

A5

16位地址总线第5位(bit0)

61

A6

16位地址总线第6位(bit0)

57

A7

16位地址总线第7位(bit0)

53

A8

16位地址总线第8位(bit0)

51

A9

16位地址总线第9位(bit0)

48

A10

16位地址总线第10位(bit0)

45

A11

16位地址总线第11位(bit0)

43

A12

16位地址总线第12位(bit0)

39

A13

16位地址总线第13位(bit0)

34

A14

16位地址总线第14位(bit14)

31

A15

16位地址总线第15位(bit15)

127

D0

16位数据总线第0位(bit0)

引脚号

引脚名

功能

130

D1

16位数据总线第1位(bit0)

132

D2

16位数据总线第2位(bit0)

134

D3

16位数据总线第3位(bit0)

136

D4

16位数据总线第4位(bit0)

138

D5

16位数据总线第5位(bit0)

143

D6

16位数据总线第6位(bit0)

5

D7

16位数据总线第7位(bit0)

9

D8

16位数据总线第8位(bit0)

13

D9

16位数据总线第9位(bit0)

15

D10

16位数据总线第10位(bit0)

17

D11

16位数据总线第11位(bit0)

20

D12

16位数据总线第12位(bit0)

22

D13

16位数据总线第13位(bit0)

24

D14

16位数据总线第14位(bit14)

27

D15

16位数据总线第15位(bit15)

电源电压

29、50、86、129

VDD

内核电源电压+3.3V数字逻辑电源电压。

4、42、67、77、95、141

VDDO

I/O缓冲电源电压+3.3V,数字逻辑和缓冲器电源电压。

28、49、85、128

VSS

内核电源地,数字参考地。

3、41、66、76、94、125、140

VSSO

I/O缓冲器电源地,数字逻辑和缓冲电源地。

∙DSP的功能结构

TMS320LF2407引脚可以按功能表示为如图2所示的功能结构。

10-bitADC

具有双排序器

数字I/O

与其他引脚共享

事件管理器B

∙3个捕获输入

∙6个比较/PWM输出

∙2个定时器/PWM

事件管理器A

∙3个捕获输入

∙6个比较/PWM输出

∙2个定时器/PWM

外部存储器接口

Flash/ROM

32K字

4K/12K/12K/4K

图2TMS320LF2407的功能结构

∙TMS320LF2407中ADC转换模块

TMS320LF2407具有内置采样和保持器(S/H)的10位模数转换(ADC)内核,具有最短达375ns的转换时间(S/H+转换);一共具有16个模拟输入通道(ADCIN0~ADCIN15)。

AD转换可以采用多个触发源,可以启动转换(SOC),包括:

软件立即启动(使用SOC的SEQn位);事件管理器A(在EVA中有多个事件源可以启动转换),或者事件管理器B(在EVB中有多个事件源可以启动转换),也可以使用外部ADCSOC引脚启动。

芯片具有输入通道的自动排序能力,一次最多可执行16个通道的“自动转换”,而每次要转换的通道可以通过编程来选择。

排序器可工作在启动/停止模式,允许多个按时间排序的触发源同步转换。

转换结果存储在可单独访问的16个结果寄存器(RESULT0~RESULT15)中。

采样保持时间可以独立设置,用于适应不同内阻的信号源。

图3TMS320LF2407ADC结构图

∙TMS320LF2407外接LCD模块