基于FPGA的数字系统设计实验3lcd显示字符OK的程序.docx

《基于FPGA的数字系统设计实验3lcd显示字符OK的程序.docx》由会员分享,可在线阅读,更多相关《基于FPGA的数字系统设计实验3lcd显示字符OK的程序.docx(23页珍藏版)》请在冰豆网上搜索。

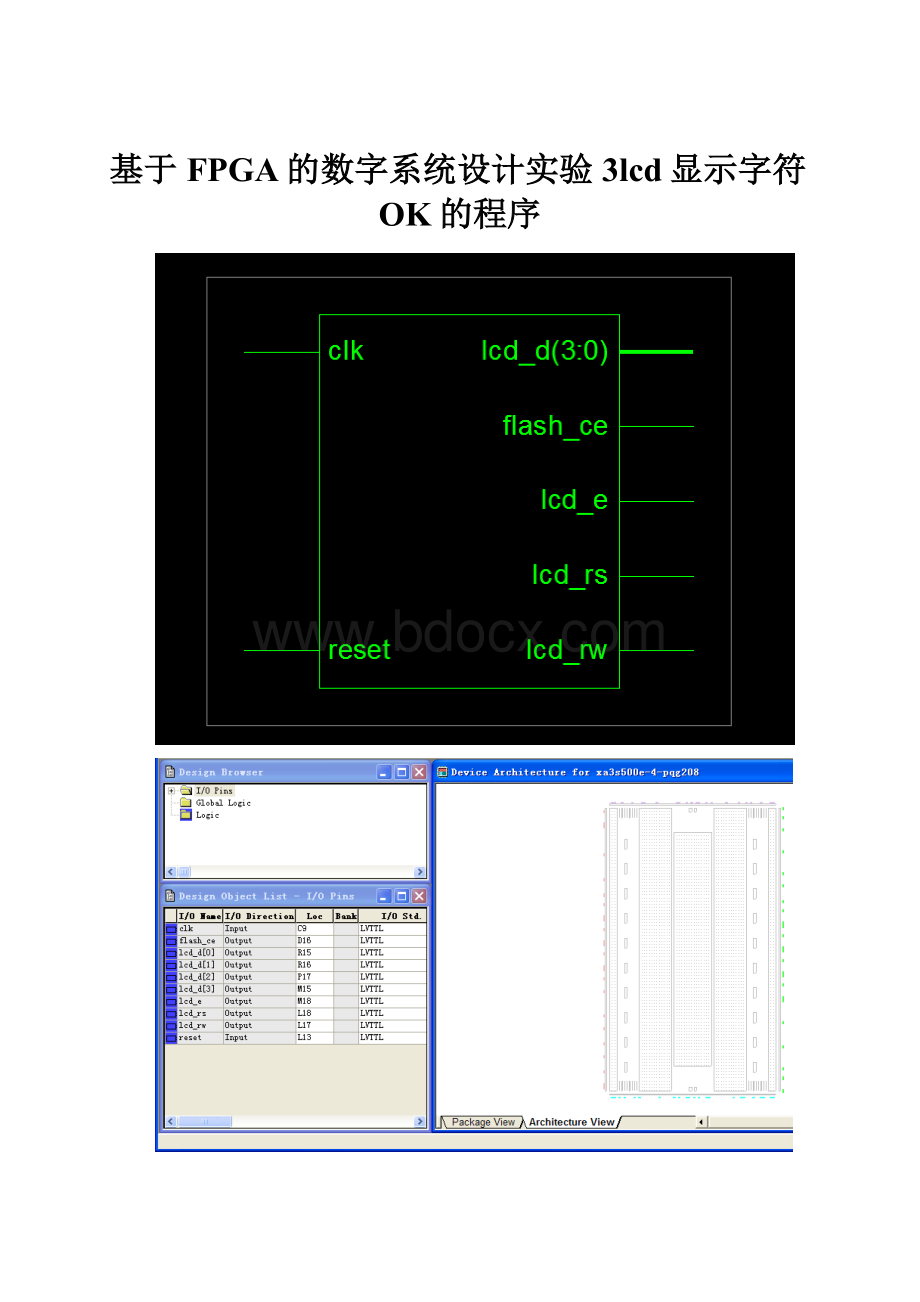

基于FPGA的数字系统设计实验3lcd显示字符OK的程序

`timescale1ns/1ps

//////////////////////////////////////////////////////////////////////////////////

//Company:

//Engineer:

//

//CreateDate:

15:

48:

3004/21/2015

//DesignName:

//ModuleName:

lcd

//ProjectName:

//TargetDevices:

//Toolversions:

//Description:

//

//Dependencies:

//

//Revision:

//Revision0.01-FileCreated

//AdditionalComments:

//

//////////////////////////////////////////////////////////////////////////////////

modulelcd(clk,reset,lcd_rs,lcd_rw,lcd_e,lcd_d,flash_ce);

inputclk;

inputreset;

outputlcd_rs;

outputlcd_rw;

outputlcd_e;

output[3:

0]lcd_d;

outputflash_ce;

reglcd_rs,lcd_e;

reg[3:

0]lcd_d;

assignflash_ce=1;

assignlcd_rw=0;

reg[19:

0]delay_count;

reg[19:

0]num_count;

parameterstate1=6'b000001;

parameterstate2=6'b000010;

parameterstate3=6'b000011;

parameterstate4=6'b000100;

parameterstate5=6'b000101;

parameterstate6=6'b000110;

parameterstate7=6'b000111;

parameterstate8=6'b001000;

parameterstate9=6'b001001;

parameterstate10=6'b001010;

parameterstate11=6'b001011;

parameterstate12=6'b001100;

parameterstate13=6'b001101;

parameterstate14=6'b001110;

parameterstate15=6'b001111;

parameterstate16=6'b010000;

parameterstate17=6'b010001;

parameterstate18=6'b010010;

parameterstate19=6'b010011;

parameterstate20=6'b010100;

parameterstate21=6'b010101;

parameterstate22=6'b010110;

parameterstate23=6'b010111;

parameterstate24=6'b011000;

parameterstate25=6'b011001;

parameterstate26=6'b011010;

parameterstate27=6'b011011;

parameterstate28=6'b011100;

parameterstate29=6'b011101;

parameterstate30=6'b011110;

parameterstate31=6'b011111;

parameterstate32=6'b100000;

parameterstate33=6'b100001;

parameterstate34=6'b100010;

parameterstate35=6'b100011;

parameterstate36=6'b100100;

parameterstate37=6'b100101;

parameterstate38=6'b100110;

parameterstate39=6'b100111;

parameterstate40=6'b101000;

parameterstate41=6'b101001;

parameterstate42=6'b101010;

parameterstate43=6'b101011;

parameterstate44=6'b101100;

parameterstate45=6'b101101;

parameterstate46=6'b101110;

parameterstate47=6'b101111;

parameterstate48=6'b110000;

parameterstate49=6'b110001;

parameterstate50=6'b110010;

parameterstate51=6'b110011;

parameterstate52=6'b110100;

parameterstate53=6'b110101;

parameterstate54=6'b110110;

parameterstate55=6'b110111;

parameterstate56=6'b111000;

parameterstate57=6'b111001;

parameterstate58=6'b111010;

parameterstate59=6'b111011;

reg[5:

0]state;

regstate_change;

always@(posedgeclkorposedgereset)

if(reset)

begin

state_change<=1'b0;

delay_count<=1'b1;

end

else

if(delay_count==num_count-1)

begin

state_change<=1'b1;

delay_count<=1'b1;

end

else

begin

state_change<=1'b0;

delay_count<=delay_count+1'b1;

end

always@(posedgestate_changeorposedgereset)

if(reset)

begin

state<=state1;

num_count<=20'd750000;

end

else

case(state)

state1:

begin

state<=state2;

num_count<=20'd4;

lcd_rs<=1'b0;

lcd_e<=1'b0;

lcd_d<=4'h3;

end

state2:

begin

state<=state3;

num_count<=20'd12;

lcd_e<=1'b1;

end

state3:

begin

state<=state4;

num_count<=20'd205000;

lcd_e<=1'b0;

end

state4:

begin

state<=state5;

num_count<=20'd4;

lcd_d<=4'h3;

end

state5:

begin

state<=state6;

num_count<=20'd12;

lcd_e<=1'b1;

end

state6:

begin

state<=state7;

num_count<=20'd5000;

lcd_e<=1'b0;

end

state7:

begin

state<=state8;

num_count<=20'd4;

lcd_d<=4'h2;

end

state8:

begin

state<=state9;

num_count<=20'd12;

lcd_e<=1'b1;

end

state9:

begin

state<=state10;

num_count<=20'd4000;

lcd_e<=1'b0;

end

//setfuntionmode

state10:

begin

state<=state11;

num_count<=20'd4;

lcd_rs<=0;

lcd_d<=4'h2;

end

state11:

begin

state<=state12;

num_count<=20'd12;

lcd_e<=1'b1;

end

state12:

begin

state<=state13;

num_count<=20'd80;

lcd_e<=1'b0;

end

state13:

begin

state<=state14;

num_count<=20'd4;

lcd_d<=4'h8;

end

state14:

begin

state<=state15;

num_count<=20'd12;

lcd_e<=1'b1;

end

state15:

begin

state<=state16;

num_count<=20'd4000;

lcd_e<=1'b0;

end

//setentrymode

state16:

begin

state<=state17;

num_count<=20'd4;

lcd_d<=4'h0;

end

state17:

begin

state<=state18;

num_count<=20'd12;

lcd_e<=1'b1;

end

state18:

begin

state<=state19;

num_count<=20'd80;

lcd_e<=1'b0;

end

state19:

begin

state<=state20;

num_count<=20'd4;

lcd_d<=4'h6;

end

state20:

begin

state<=state21;

num_count<=20'd12;

lcd_e<=1'b1;

end

state21:

begin

state<=state22;

num_count<=20'd4000;

lcd_e<=1'b0;

end

//setdisplayon/off

state22:

begin

state<=state23;

num_count<=20'd4;

lcd_d<=4'h0;

end

state23:

begin

state<=state24;

num_count<=20'd12;

lcd_e<=1'b1;

end

state24:

begin

state<=state25;

num_count<=20'd80;

lcd_e<=1'b0;

end

state25:

begin

state<=state26;

num_count<=20'd4;

lcd_d<=4'hc;

end

state26:

begin

state<=state27;

num_count<=20'd12;

lcd_e<=1'b1;

end

state27:

begin

state<=state28;

num_count<=20'd4000;

lcd_e<=1'b0;

end

//cleardisplay

state28:

begin

state<=state29;

num_count<=20'd4;

lcd_d<=4'h0;

end

state29:

begin

state<=state30;

num_count<=20'd12;

lcd_e<=1'b1;

end

state30:

begin

state<=state31;

num_count<=20'd80;

lcd_e<=1'b0;

end

state31:

begin

state<=state32;

num_count<=20'd4;

lcd_d<=4'h1;

end

state32:

begin

state<=state33;

num_count<=20'd12;

lcd_e<=1'b1;

end

state33:

begin

state<=state34;

num_count<=20'd2000;

lcd_e<=1'b0;

end

state34:

begin

state<=state35;

num_count<=20'd82000;

end

//setDDRAMaddress

state35:

begin

state<=state36;

num_count<=20'd4;

lcd_rs<=1'b0;

lcd_e<=1'b0;

lcd_d<=4'h8;

end

state36:

begin

state<=state37;

num_count<=20'd12;

lcd_e<=1'b1;

end

state37:

begin

state<=state38;

num_count<=20'd80;

lcd_e<=1'b0;

end

state38:

begin

state<=state39;

num_count<=20'd4;

lcd_d<=4'h0;

end

state39:

begin

state<=state40;

num_count<=20'd12;

lcd_e<=1'b1;

end

state40:

begin

state<=state41;

num_count<=20'd4000;

lcd_e<=1'b0;

end

//nowstartswritingdatatoDDRAM

state41:

begin

state<=state42;

num_count<=20'd4;

lcd_rs<=1'b1;

lcd_d<=4'h4;

end

state42:

begin

state<=state43;

num_count<=20'd12;

lcd_e<=1'b1;

end

state43:

begin

state<=state44;

num_count<=20'd80;

lcd_e<=1'b0;

end

state44:

begin

state<=state45;

num_count<=20'd4;

lcd_d<=4'hf;

end

state45:

begin

state<=state46;

num_count<=20'd12;

lcd_e<=1'b1;

end

state46:

begin

state<=state47;

num_count<=20'd2000;

lcd_e<=1'b0;

end

state47:

begin

state<=state48;

num_count<=20'd4;

lcd_rs<=1'b1;

lcd_d<=4'h4;

end

state48:

begin

state<=state49;

num_count<=20'd12;

lcd_e<=1'b1;

end

state49:

begin

state<=state50;

num_count<=20'd80;

lcd_e<=1'b0;

end

state50:

begin

state<=state51;

num_count<=20'd4;

lcd_d<=4'hb;

end

state51:

begin

state<=state52;

num_count<=20'd12;

lcd_e<=1'b1;

end

state52:

begin

state<=state53;

num_count<=20'd2000;

lcd_e<=1'b0;

end

state53:

begin

state<=state54;

num_count<=20'd4;

lcd_rs<=1'b1;

lcd_d<=4'h2;

end

state54:

begin

state<=state55;

num_count<=20'd12;

lcd_e<=1'b1;

end

state55:

begin

state<=state56;

num_count<=20'd80;

lcd_e<=1'b0;

end

state56:

begin

state<=state57;

num_count<=20'd4;

lcd_d<=4'h1;

end

state57:

begin

state<=state58;

num_count<=20'd12;

lcd_e<=1'b1;

end

state58:

begin

state<=state59;

num_count<=20'd4000;

lcd_e<=1'b0;

end

state59:

begin

state<=state35;

num_count<=20'd800;

end

default:

begin

state<=state1;

num_count<=20'd800;

end

endcase

endmodule

NET"clk"LOC="C9"|IOSTANDARD=LVTTL;

NET"flash_ce"LOC="D16"|IOSTANDARD=LVTTL|DRIVE=2|SLEW=SLOW;

NET"lcd_d<0>"LOC="R15"|IOSTANDARD=LVTTL|DRIVE=2|SLEW=SLOW;

NET"lcd_d<1>"LOC="R16"|IOSTANDARD=LVTTL|DRIVE=2|SLEW=SLOW;

NET"lcd_d<2>"LOC="P17"|IOSTANDARD=LVTTL|DRIVE=2|SLEW=SLOW;

NET"lcd_d<3>"LOC="M15"|IOSTANDARD=LVTTL|DRIVE=2|SLEW=SLOW;

NET"lcd_e"LOC="M18"|IOSTANDARD=LVTTL|DRIVE=2|SLEW=SLOW;

NET"lcd_rs"LOC="L18"|IOSTANDARD=LVTTL|DRIVE=2|SLEW=SLOW;

NET"lcd_rw"LOC="L17"|IOSTANDARD=LVTTL|DRIVE=2|SLEW=SLOW;

NET"reset"LOC="L13"|IOSTANDARD=LVTTL|PULLUP;