计算机组成原理课程设计实验报告.docx

《计算机组成原理课程设计实验报告.docx》由会员分享,可在线阅读,更多相关《计算机组成原理课程设计实验报告.docx(40页珍藏版)》请在冰豆网上搜索。

计算机组成原理课程设计实验报告

计算机组成原理课程设计实验报告

、课程设计的题目

设计一台嵌入式CISC的模型计算机(采用定长CPU周期,联合控制方式),并运行能完成一定功能的机器语言进行验证。

1、内容:

输入1到8的之间的任一一个数N,求1到N之间的所有数的平方和并显示输出,和为单字长。

2、实现方法:

采用三总线结构的运算器,不采用RAM.

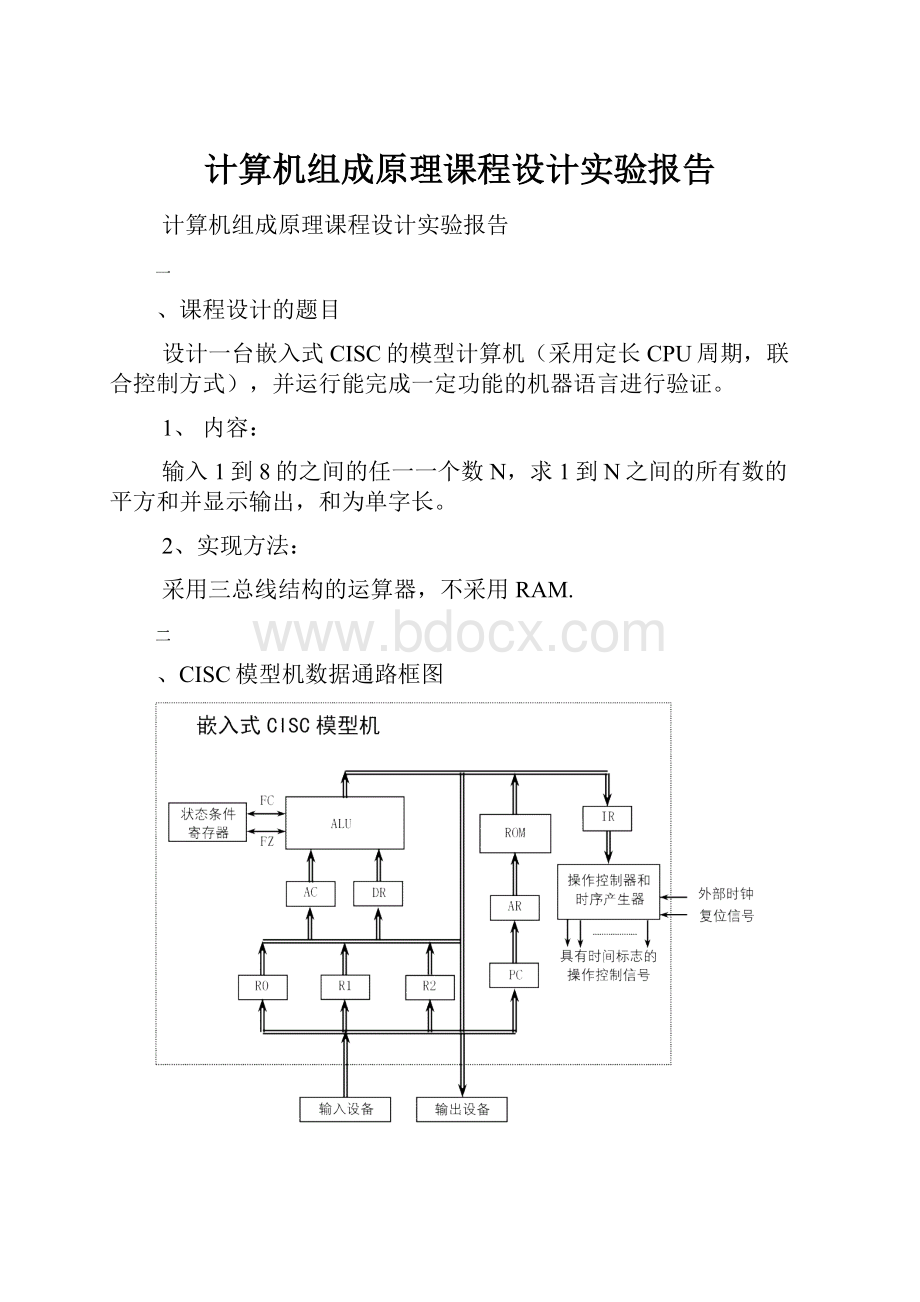

、CISC模型机数据通路框图

、操作控制器的逻辑结构框图

说明:

在T4内形成微指令的微地址,并访问控制存储器,在T2的上边沿到来时,将读出的微指令打入微指令寄存器,即图中的微命令寄存器和微地址寄存器。

、模型机的指令系统和所有的指令的指令格式

本模型机中的指令系统中共有10条基本指令,下表列出了每条指令的格式、汇编符号和指令功能。

助记符号

指令格式

功能

IN1Rd

1000

××

Rd

将数据存到Rd寄存器

OUT1Rs

1111

Rs

××

(Rs)→LED

ADDRs,Rd

1100

Rs

Rd

(Rs)+(Rd)→Rd

CMPRs,Rd

1010

Rs

Rd

(Rs)-(Rd),锁存CY和ZI

INCRd

1101

××

Rd

(Rd)+1→Rd

MOVRd,data

1001

××

Rd

data

data→Rd

JMPaddr

1110

××××

addr

addr→PC

JBaddr

1011

××××

Addr

若小于,则addr→PC

MOV1Rs,Rd

0001

Rs

Rd

(Rs)→Rd

MULRs,Rd

0111

Rs

Rd

(Rs)*(Rd)→Rd

说明:

①对Rs和Rd的规定:

Rs或Rd

选定的寄存器

00

R0

01

R1

10

R2

11

R3

②模型机规定数据的表示采用定点整数补码表示,单字长为8位,其格式如下:

7

6543210

符号位

尾数

、所有机器指令的微程序流程图

、汇编语言源程序

程序:

功能:

IN1R0从开关输入任意一个整数n→R0

MOVR1,1将立即数1→R1(R1用于存放参与运算的奇数)

MOVR2,0将立即数0→R2(R2用于存放累加和)

MOVR3,1将立即数1→R1(R1用于存放参与运算的奇数)L1:

CMPR0,R1将R0的整数n与R1的奇数进行比较,锁存CY/FC

和FZ/ZI

JBL2小于,则转到L2处执行

MOVR1,R3将R1寄存器的内容送给寄存器R3

MULR3,R3求平方

ADDR3,R2将平方送给R2

INCR1累加之后让R1的内容加1

JMPL1跳转到L1处继续执行

L2:

OUT1R2输出累加和

JMPL2循环显示

、机器语言源程序

助记符地址(十六进制)机器代码功能

IN1RO0010000000(SW)→R0

MOVR1,101100100011→R1

0200000001

MOVR2,003100100100→R2

0400000000

MOVR3,105100100111→R3

0600000001

L1:

CMPR0,R10710100001(R0)-(R1)

JBL20810110000L2→PC

0900010000

MOVR1,R30A00010111(R1)→R3

MULR3,R30B01111111(R3)*(R3)→R3

ADDR3,R20C11001110(R3)+(R2)→R2

INCR10D11010001(R1)+1→R1

JMPL10E11100000L1→PC

0F00000111

L2:

OUT1R21011111000(R2)→LED

JMPL21111100000L2→PC

1200010000

、机器语言源程序的功能仿真波形图及结果分析

注释:

1、R2:

存放累加和(本例中初始值R2=00,最后值R2=0E)

2、R1:

存放初始值,并进行自加运算。

(R1=01)

3、R3:

存放R1中的数据,并进行平方元算,最后将运算结果送给R2。

(R3=01)

4、R0:

用来存放任意值N。

(R0=03)

5、ID[7..0]:

外部输入,与R0的值相同(ID[7..0]=03)

6、OD[7..0]:

外部输出数据,只有最后才会输出数据,其值与R2的最后结果相同(最后结果OD[7..0]=0E)

7、IR:

指令寄存器,存放各指令(本例中:

00-80-91-92-93-A1依次执行的是INR0MOVR1,1MOVR2,0MOVR3,1CMPR0,R1这四条指令)

8、AR:

地址寄存器,存放各指令的地址(本例中:

00---IN指令的地址;;01-02----MOVR1,1指令的地址;;03-04----MOVR2,0指令的地址;;05-06----MOVR3,1指令的地址;;07-----CMP指令的地址)

NOTE:

IR、AR这两行的数据要对应机器语言源程序来看去理解

9、ntrom5|ADDR:

控制存储器,存放所有微指令和对应的微地址

NOTE:

本行的数据要根据指令流程图去理解;本例中MOV指令的地址和后继微地址为:

02-00-09-03-00而02-00-0A-04-05-00是CMP指令的地址和后继微地址。

十、故障现象和故障分析

1、源程序中出现错误。

本例中若只用三个寄存器,去掉R3这个有转换作用的寄存器,那么直接用R1相乘的话就会使得R1的值不是加1递增,而是在平方的基础上自动加1,比如:

当R1=01时,经过平方,R1寄存器中的内容为1,加1后变为02,经过下一次循环,平方后变为04,在进行加1后就会变为05,明显少算了许多值。

2、在连线顶层电路的过程中出错。

有时因为不认真连错线就会在仿真的时候,出现不正常的警告,而香型的项则不会输出任何数据,就像OD[7..0]此行,初始的时候是不应该有输出的,但是若在连线的时候错连或不连就会导致,在刚开始的时候就会有数值的输出,误导结果分析。

3、指令流程图中出现错误。

指令流程图可以说是整个实验中比较关键的一项,它的指令流程和指令的地址和后继微地址,是至关重要的,如果指令微地址的分配不合理会导致指令执行的混乱,导致不能指向正常执行的指令,结果在方针是就不会有结果输出或者输出错误的结果。

4、微指令代码表的填写不正确。

微指令代码表中关键是那些控制信号的输入一定要填写正确,否则在应该读入数据的时候,系统没有放映;在应该读出数据的时候,不能执行相应的功能。

NOTE:

下面列举一些比较重要的功能

(1)、2423222120191817161514131211109876543210

LOADLDPCLDARLDIRLDRiRD_BRS_BS1S0ALU_BLDACLDDRWRCSSW_BLED_BLDFRP1P2后继微地址

76543210

操作码

Rs

Rd

立即数或转移地址

(2)、

26252423222120191817161514131211109876543210

WRCSLOADLDPCLDARLDIRLDRiRD_BRS_BS1S0ALU_BLDACLDDRWR_OCS_ISW_BLED_BLDFRP1P2后继微地址

WR_O和LED_B一起控制输出,可以省去WR_O;

CS_I为ROM的片选信号。

(3)、

算术逻辑运算单元ALU的功能表

S1

S0

功能

0

0

(AC)+(DR)

0

1

(AC)-(DR)

1

0

(AC)+1

1

1

(AC)*(DR)

(4)、程序计数器PC的功能表

CLR

LOAD

LDPC

功能

0

×

×

将PC清0

1

0

↑

BUS-->PC

1

1

0

不装入,也不计数

1

1

↑

PC+1

(5)、控制信号的功能(均为低电平有效)

ALU_B

R0_B

R1_B

R2_B

R3_B

功能

0

1

1

1

1

输出ALU的结果

1

0

1

1

1

输出(R0)

1

1

0

1

1

输出(R1)

1

1

1

0

1

输出(R2)

1

1

1

1

0

输出(R3)

(6)、主存储器(CS低电平有效)

CS

功能

1

不选择

0

读

5、小细节方面:

在编写各器件源程序的时候要仔细,要和之前所做的指令流程、指令地址、微指令代码表以及自己所做实验中的各引脚的多少,应一一对应。

比如,本例中用到四个寄存器,就要在编写的时候改变一些原器件的引脚,如CROM、MCOMMAND的引脚要添加寄存器R3相关的引脚,R3_B等。

6、在仿真的时候:

要学会正确且熟练地输入各个初始值,要学会对应之前的成果来验证仿真的正确性,Q和CLR两个信号的控制要正确。

十一、软件清单,含各个部件的VHDL源程序(.vhd)或图像描述文件(.gdf)

、算术逻辑单元ALU

--ALU运算器单元源程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYALUIS

PORT(

A:

INSTD_LOGIC_VECTOR(7DOWNTO0);

B:

INSTD_LOGIC_VECTOR(7DOWNTO0);

S1,S0:

INSTD_LOGIC;

BCDOUT:

OUTSTD_LOGIC_VECTOR(7DOWNTO0);

CY,ZI:

OUTSTD_LOGIC

);

ENDALU;

ARCHITECTUREAOFALUIS

SIGNALAA,BB,TEMP:

STD_LOGIC_VECTOR(8DOWNTO0);

BEGIN

PROCESS(S1,S0)

BEGIN

IF(S1='0'ANDS0='0')THEN--执行加法运算

AA<='0'&A;

BB<='0'&B;

TEMP<=AA+BB;

BCDOUT<=TEMP(7DOWNTO0);--输出

CY<=TEMP(8);--进位

IF(TEMP="100000000")THEN--即TEMP(8)=1,进位

ZI<='1';--为0

ELSE

ZI<='0';--不为0

ENDIF;

ELSIF(S1='0'ANDS0='1')THEN--执行比较或减法操作

BCDOUT<=A-B;

IF(ACY<='1';--借位

ZI<='0';--不为0

ELSIF(A=B)THEN--等于

CY<='0';--不借位

ZI<='1';--等于0

ELSE--大于

CY<='0';--不借位

ZI<='0';--不为0

ENDIF;

ELSIF(S1='1'ANDS0='0')THEN--执行加1操作

AA<='0'&A;

TEMP<=AA+1;

BCDOUT<=TEMP(7DOWNTO0);

CY<=TEMP(8);

IF(TEMP="100000000")THEN

ZI<='1';

ELSE

ZI<='0';

ENDIF;

ELSIF(S1='1'ANDS0='1')THEN--执行乘法运算

AA<='0'&A;

BB<='0'&B;

TEMP<=AA*BB;

BCDOUT<=TEMP(7DOWNTO0);

CY<=TEMP(8);

IF(TEMP="100000000")THEN

ZI<='1';

ELSE

ZI<='0';

ENDIF;

ELSE

BCDOUT<="00000000";

CY<='0';

ZI<='0';

ENDIF;

ENDPROCESS;

ENDA;

、状态寄存器LS74单元

--状态条件寄存器单元源程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYLS74IS

PORT(

LDFR:

INSTD_LOGIC;

CY,ZI:

INSTD_LOGIC;

FC,FZ:

OUTSTD_LOGIC

);

ENDLS74;

ARCHITECTUREAOFLS74IS

BEGIN

PROCESS(LDFR)

BEGIN

IF(LDFR'EVENTANDLDFR='1')THEN--时钟信号LDFR的上边沿有效

FC<=CY;--锁存进位\借位标志位

FZ<=ZI;--锁存零标志位

ENDIF;

ENDPROCESS;

ENDA;

、--暂存器单元\通用寄存器\地址寄存器\指令寄存器单元LS273

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYLS273IS

PORT(

D:

INSTD_LOGIC_VECTOR(7DOWNTO0);

CLK:

INSTD_LOGIC;

O:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDLS273;

ARCHITECTUREAOFLS273IS

BEGIN

PROCESS(CLK)

BEGIN

IF(CLK'EVENTANDCLK='1')THEN--时钟信号CLK的上边沿有效

O<=D;--将输入的内容直接送给输出

ENDIF;

ENDPROCESS;

ENDA;

、1:

2分配器单元FEN2

--1:

2分配器单元源程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYFEN2IS

PORT(

WR,LED_B:

INSTD_LOGIC;

X:

INSTD_LOGIC_VECTOR(7DOWNTO0);

W1,W2:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDFEN2;

ARCHITECTUREAOFFEN2IS

BEGIN

PROCESS(LED_B,WR)

BEGIN

IF(LED_B='0'ANDWR='0')THEN

W2<=X;--将数据送往输出设备

ELSE

W1<=X;--将数据会送到数据内部通路

ENDIF;

ENDPROCESS;

ENDA;

、3选1数据选择器MUX3单元

--3选1数据选择器单元源程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYMUX3IS

PORT(

ID:

INSTD_LOGIC_VECTOR(7DOWNTO0);

SW_B,CS:

INSTD_LOGIC;

N1,N2:

INSTD_LOGIC_VECTOR(7DOWNTO0);

EW:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDMUX3;

ARCHITECTUREAOFMUX3IS

BEGIN

PROCESS(SW_B,CS)

BEGIN

IF(SW_B='0')THEN

EW<=ID;--从输入设备输入数据

ELSIF(CS='0')THEN

EW<=N2;--将ROM中读出的指令代码送入内部数据通路

ELSE

EW<=N1;--将4选1多路选择器的输出送入内部数据通路

ENDIF;

ENDPROCESS;

ENDA;

、4选1数据选择器MUX4单元

--4选1数据选择器单元源程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYMUX4IS

PORT(

C,D,E,F,G:

INSTD_LOGIC;

X1,X2,X3,X4,X5:

INSTD_LOGIC_VECTOR(7DOWNTO0);

W:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDMUX4;

ARCHITECTUREAOFMUX4IS

SIGNALSEL:

STD_LOGIC_VECTOR(4DOWNTO0);

BEGIN

SEL<=G&F&E&D&C;

PROCESS(SEL)

BEGIN

IF(SEL="11110")THEN--输出R0的内容

W<=X1;

ELSIF(SEL="11101")THEN--输出R1的内容

W<=X2;

ELSIF(SEL="11011")THEN----输出R2的内容

W<=X3;

ELSIF(SEL="10111")THEN----输出ALU的运算结果

W<=X4;

ELSIF(SEL="01111")THEN--输出R3的内容

W<=X5;

ELSE

NULL;

ENDIF;

ENDPROCESS;

ENDA;

、程序计数器PC单元

--程序计数器单元源程序如下:

--访问只读存储器ROM的程序计数器

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYPCIS

PORT(

LOAD,LDPC,CLR:

INSTD_LOGIC;

D:

INSTD_LOGIC_VECTOR(7DOWNTO0);

O:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDPC;

ARCHITECTUREAOFPCIS

SIGNALQOUT:

STD_LOGIC_VECTOR(7DOWNTO0);

BEGIN

PROCESS(LDPC,CLR,LOAD)

BEGIN

IF(CLR='0')THEN

QOUT<="00000000";--将PC清0

ELSIF(LDPC'EVENTANDLDPC='1')THEN--LDPC上边沿有效

IF(LOAD='0')THEN

QOUT<=D;--将数据总线BUS的内容送入PC

ELSE

QOUT<=QOUT+1;--PC+1

ENDIF;

ENDIF;

ENDPROCESS;

O<=QOUT;

ENDA;

、主存储器单元

--一个带有8位地址输入和8位输出的只读存储器

--主存储器ROM16单元,用来存放CPU要运行的程序和数据

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYROM16IS

PORT(

ADDR:

INSTD_LOGIC_VECTOR(7DOWNTO0);

CS:

INSTD_LOGIC;

DOUT:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDROM16;

ARCHITECTUREAOFROM16IS

BEGIN

DOUT<="10000000"whenaddr="00000000"andcs='0'else--inr0

"10010001"whenaddr="00000001"andcs='0'else--movr1,0

"00000001"whenaddr="00000010"andcs='0'else

"10010010"whenaddr="00000011"andcs='0'else--movr2,0

"00000000"whenaddr="00000100"andcs='0'else

"10010011"whenaddr="00000101"andcs='0'else--movr3,1

"00000001"whenaddr="00000110"andcs='0'else

"10100001"whenaddr="00000111"andcs='0'else--L1:

cmpr0,r1

"10110000"whenaddr="00001000"andcs='0'else--jbL2

"00010000"whenaddr="00001001"andcs='0'else

"00010111"whenaddr="00001010"andcs='0'else--mov1r1,r3

"01111111"whenaddr="00001011"andcs='0'else--mulr3,r3

"11001110"whenaddr="00001100"andcs='0'else--addr3,r2

"11010001"whenaddr="00001101"andcs='0'else--incr1

"11100000"whenaddr="00001110"andcs='0'else--jmpL1

"00000111"whenaddr="00001111"andcs='0'else

"11111000"whenaddr="00010000"andcs='0'else--L2:

outr2

"11100000"whenaddr="00010001"andcs='0'else--jmpL2

"00010000"whenaddr="00010010"and